�����������ż��ɵ�·�����ķ�չ���ô�ͳ�ķ�������оƬ��ϵͳ����Ѳ�������Ҫ��������Ҫ������Ч�ʡ��������ļ��������£��ܴ������Ѷȵ�VHDL��Ʒ�����Խ��Խ�㷺�ر����á�����VHDL�������Ϊ������Ƣ�������������������ߵ����˼�����·�ṹ���ѽڡ��������Ҫ�Ǹ���VHDL�������ϵͳĿ�������Ϊ����������Ȼ��ͨ���ۺϹ��߽��е�·�ṹ���ۺϡ����롢�Ż���ͨ�����湤�߽��������ܷ����ϵͳʱ�ӵķ��档ʵ����ƹ����У�����ÿ������ʦ�����Թ��Ե�·��Ϊ������̶Ȳ�ͬ��ÿ���˵ı�̷��ͬ������ͬ����ϵͳ���ܣ������ķ�ʽ�Dz�һ���ģ��ۺϳ����ĵ�·�ṹ���Ǵ��ྶͥ����ˣ���ʹ����ۺϳ��ĵ�·����ʵ����ͬ�������ܣ����·�ĸ��ӳ̶Ⱥ�ʱ�����Զ����кܴ�IJ������ijЩӷ�ĵ�·�����������Ԥ�ϵ����⡣�����������������Ǿͺ��б�Ҫ����������VHDL�������μ�·�ṹ���Ż���·��Ƶ����⡣

1 ���������Ե�·�ṹ��Ӱ��

��VHDL������ƣ��������ۺϳ��ĵ�·�ĸ��ӳ̶ȳ�ȡ�������Ҫ��ʵ�ֵĹ��ܵ��Ѷ��⣬������ƹ���ʦ�Ե�·�����������Ͷ���ƵĹ滮ˮƽ��Ӱ�졣�����ʹ��·���ӻ���ԭ��֮һ������д������౾����Ҫ������LATcH�Ľṹ������������Щ�ṹͨ�����ɴ����Ĵ�������ɣ�����ʹ��·�����ӣ������ٶȽ��ͣ���������ʱ����ϵ�ԭ������²���Ԥ�ϵĽ�����������ͬһ�����·�в�ͬVHDL������

1�� IF INDEX��"00000" THEN

STEPSIZE<��"0000111"��

ELSIF INDEX��"00001" THEN

STEPSIZE<��"0001000"��

LSIF INDEX��"00010" THEN

STEPSIZE<��"0001001"��

����

ELSE

STEPSIZE<��"0000000"��

END IF��

2��STEPSIZE<��"0000111" WHEN INDEX��"00000" ELSE

"0001000" WHEN INDEX��"00001"ELSE

"0001001"WHEN INDEX��"00010" ELSE

����

�������γ���������ͬһ�������·���ڶ��γ�������WHEN ����������ELSE����䲻�������������Ľṹ��ELSE��һ��Ҫ�н�������Բ��������⣬����һ�������������ELSE STEPSIZE������0000000����䣬�������һ������7λ�Ĵ����Ľṹ����Ȼ����ʵ����ͬ�����빦�ܡ����ǵ�·���ӶȻ������������ÿ������ʦ��д��ϰ�߲�ͬ���е�ϲ����IF��������ELSE����䣬�е�ϲ����WHEN����������ELSE�ķ�ʽ������IF����������ELSEʱ�����Բ�ע�⣬����������Ҫ�Ĵ����ĵ�·ʱû��ELSE����������·����Ҫ�Ŀ�����������VHDL�����Ҫ����IF ������ELSE��������������ֵ�������䡣

2 ��ƹ滮������ֱ��Ӱ���·�ṹ

��һ��Ҫ�����·���ӻ���ԭ���Ƕ���ƹ滮�IJ���������ȻVHDL�����ܴ���Ϊ�������ɵ�·����һ�����������һ����˵����������ֱ��������Ƶ�Ŀ�깦����ʵ�ֵġ���Ҫ����Ʒֳ����ɲ��֣�ÿһ�����ٷֱ���������Ϊ������漰����λ��ֹ���ģ������⣬Ҫ�������˽�Ľ����룬����ʹ���ָ���Ч�����ܽ��͵�·�ĸ��ӳ̶ȡ������������һ��ʱ��ԴΪ1KHZ��ÿ32�뷢��һ���źţ������飩�ļĿ�������˵������������ʵ�ַ�����

��1����15λ�ļ�����ʵ�ְ�����1KHZ��ʱ�ӷ�ƵΪ1/32HZ��Ȼ���������Ϊʱ������һ��3λ�ļ�����������������İ˸�״̬�ֱ�ͨ��һ��3��8������������Ҫ����źš�

(2)ֱ����18λ�ļ������������1KHZʱ�ӽ��з�Ƶ�������ü������İ˸����32���״̬���ƶ�һ��12��8��������ʵ�֡�

������˵����Ҫ��VHDL����ֱ�������ʾ��

1�� ��һ����Ʒ�����VHDLԴ����

ProcESS(cLK��ccLK��couNT2)

bEgIN

IF(cLK��'1' AND cLK'EVENT)THEN

couNT2<��couNT2 �� 1��

IF(couNT2��"000000000000000")THEN

ccLK<��'1'��

ELSE

ccLK<��'0'��

END IF��

END IF��

END ProcESS��

ProcESS(ccLK��couNT3��cTEmP)

bEgIN

IF(ccLK��'1' AND ccLK'EVENT)THEN

couNT3<��couNT3 �� 1��

IF(couNT3��"000")THEN

cTEmP<��"00000001"��

ELSIF(couNT3��"001")THEN

cTEmP<��"00000010"��

ELSIF(couNT3��"010")THEN

cTEmP<��"00000100"��

ELSIF(couNT3��"011")THEN

cTEmP<��"00001000"��

ELSIF(couNT3��"100")THEN

cTEmP<��"00010000"��

ELSIF(couNT3��"101")THEN

cTEmP<��"00100000"��

ELSIF(couNT3��"110")THEN

cTEmP<��"01000000"��

ELSIF(couNT3��"111")THEN

cTEmP<��"10000000"��

ELSE

cTEmP<��"00000000"��

END IF��

END IF��

END ProcESS��

2�� �ڶ�����Ʒ�����VHDLԴ����

ProcESS(cLK��cTEmP��couNT)

bEgIN

IF(cLK��'1' AND cLK'EVENT)THEN

couNT<��couNT �� 1��

IF(couNT��"00000000000000000")THEN

cTEmP<��"00000001"��

ELSIF(couNT��"001000000000000000")THEN

cTEmP<��"00000010"��

ELSIF(couNT��"010000000000000000")THEN

cTEmP<��"00000100"��

ELSIF(couNT��"011000000000000000")THEN

cTEmP<��"00001000"��

ELSIF(couNT��"100000000000000000")THEN

cTEmP<��"00010000"��

ELSIF(couNT��"101000000000000000")THEN

cTEmP<��"00100000"��

ELSIF(couNT��"110000000000000000")THEN

cTEmP<��"01000000"��

ELSIF(couNT��"111000000000000000")THEN

cTEmP<��"10000000"��

END IF��

END IF��

END ProcESS��

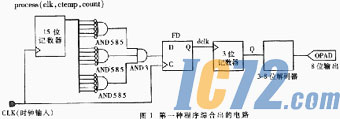

���ڵ�һ�ֵij�������ۺϳ��ĵ�·��ͼ1��ʾ��

�õ�·��һ��15λ�ļӷ����ͼĴ������һ��15λ�ļ��������ڼ���������һ�ܻص���000000000000000��ʱ��ͨ�������15���������ź�һλ�Ĵ������Ϳ���ʵ��ͬ���Ľ���215�η�Ƶ��ͬ�����32HZ��ʱ��ccLK��ccLK������һ8λ����λ�Ĵ��������ʵ��ÿ32�����һ�źš�

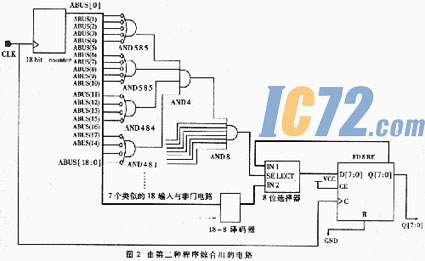

���õڶ��ֵij�������ۺϳ��ĵ�·��ͼ2��ʾ��

ͼ2��ʾ�ĵ�·��һ��18λ�ļӷ����ͼĴ������һ��18λ�ļ������������8��18��������ź�8����Ļ��š������1KHZʱ�Ӿ�������������Ƶ�������а˸����32HZ�ļ���״̬�����ž�������״̬���������İ����źš�����������ͨ��ѡ���������8λ�Ĵ���������ʵ��ͬ����������и�����������������������źŲ��䣬�ڰ˸�״̬�еĴ�һ��״̬�䵽��һ��֮ǰ������ǰһ������ֵ��ѡ��������������µ�����ʱ�����������ͨ�����������ݵ���֮ǰ��������������ݡ�

�������ַ�������ʵ����ͬ�������ܣ���ͼ2��ʾ�ķ������������˽���λ���ļ����������õ�����Ҳ�ϼ����һ������˶�·ѡ��������������Դ�������ۺϳ����ĵ�·�ϼ���XILINX

SPArTAN S05 ��3 оƬΪ������һ�ַ���ռ��оƬcLb��12%������FmAPSΪ9%����߹����ٶ�Ϊ82mHZ�����ڶ��ַ���ռ����15%��cLb��FmAPSռ��15%����߹����ٶ�ֻ��69��9mHZ������һ�������֮�о���ʡ20%�ĵ�·�����12��1mHZ�Ĺ����ٶȣ��ɴ˿ɼ���ѧ�Ļ�����ƶԽ��͵�·���ӳ̶ȵ���Ҫ���塣

3 ����ƶԵ�·�ṹ��Ӱ��

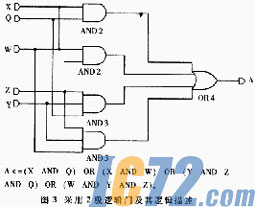

����һ��ʹ��·���ӻ���ԭ��������·��������̫��������ռ�ù������������Ǵ�ͼ3��ͼ4������ͬ���ܵ�����·�����Ƕ�Ӧ��VHDL������������

�Ƚ���ͼ��֪��ͼ3�Ƕ������ţ�ÿ�������ź��벻ֻһ������������ͼ4�����������ţ�ÿ�������ź�ֻ��һ�������������ڼ����٣���ʱҲ���٣����ͼ3���ٶ�Ҫ��ͼ4�졣Ȼ��������ͼ3��������Ҫ��ͼ4��Ķࣨ10:5������ˣ�ռ�õ������ȻҲ��ͼ3��ͼ4��ͼ3ͨ����ȡ��������������b��c�������ģ����ǰѸ��ӵ��м���ӵ��ṹ������ȥ��һ�ֹ��̣���ʹ���뵽����е����������ӣ������ٶȻ�����·ռ������ļ��١����ڶ���ʱҪ�ߵ�����²������ַ����ֽ�����·�Դﵽ���ٵ�·���Ӷȵ�Ŀ�ġ�

ͨ�����ϼ�������̽�֣����ǿ���֪������VHDL���м��ɵ�·����ƣ�ǣ�浽��VHDL���Ե�ʹ�÷����Ͷ���Ƶ�����̶ȡ��������������¼������Ż���·��Ƶ�3��ֵ��ע��ķ��棺

��1������VHDL���������Ҫע����ⲻ��Ҫ�ļĴ���������

��2���ڱ�д����ǰҪ�ȶ�������ƽ��н�������˽⢟��ѧ�Ļ�����ƣ������뼸�ַ������ٽ��бȽϢ��ö������λ���ĵ�Ԫȡ���϶�λ���ĵ�Ԫ��

��3������ʱҪ�ߵ�����£�����ȡ����·�����Ӣ������ֽ�ɺ����м�����Ķ༶��·�� |