引言

数字音频处理是指为真实再现声音的逼真效果而对音频进行的编解码处理技术,它是宽带网络多媒体、移动多媒体通信的关键技术.Audio Codec′97(音频数字信号编/解码器)是其中一种用于声音录放的技术标准,简称AC′97. AC′97采用双集成结构,即Digital Controller(数字信号控制器)和Audio Codec(音频编解码),使模/数转换器ADC和数?模转换器DAC转换模块独立,尽可能降低EMI(电磁干扰)的影响。

利用FPGA,可以实现复杂的逻辑控制,对大量音频数据做并行处理.FPGA提供可编程时钟发生器,满足音视频处理要求的时钟范围宽、相位抖动(Phase Jitter)小的要求,并为系统提供可控延时。

1 AC-Link音频编/解码原理

AC-Link是连接Digital Controller和Audio Codec的5线串行时分多路I/O接口,固定时钟频率48kHz由串行位时钟12.288MHz经256分频而来,支持一个控制器和最多4个编码器. AC-Link只能传输48kHz固定取样率的PCM(脉冲编码调制)信号,字长从16Bit到20Bit,其它取样率的PCM信号须经过SRC(取样率转换)转换成48kHz。

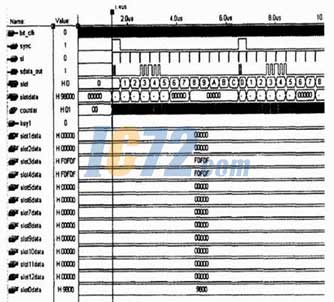

AC-Link接口时序如图1所示,输入输出音频数据和控制寄存器的读写命令组织在一帧里,一个输入或输出分割成12个时隙,每个时隙为20位采样分辨率.控制器把12.288MHz时钟256分频,产生一个SYNC信号,此信号用于标志一个输入(输出)帧的开始。

图1 双向AC-Link数据帧及时隙分配

由图1可知,每个输入(输出)帧除了有12个20位的数据/命令(数据/状态)复用时隙外,还有一个特殊的16位的帧首时隙,此时隙主要用来标志此帧是否可用,如果此帧可用,那么此帧中对应时隙中为有效数据。

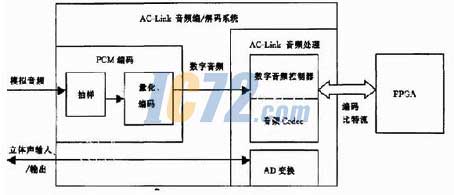

如图2所示,PCM通过抽样、量化、编码三个步骤将连续变化的模拟信号转换为数字编码,PCM编码是最高保真水平编码,音质好但体积大.AC-Link能够传输48KHz固定取样率的PCM信号,字长可以从16Bit到20Bit,其它取样率的PCM信号必须先经过SRC(Sample Rate Conversion,取样率转换)转换成48KHz。

图2 AC-Link音频编解码过程

如果PCM信号的字长低于DAC的,那么Controller会自动将PCM信号进行移位,使其MSB( Most Significant Bit,最高有效位)对齐,低位补0.如果PCM信号的字长高于DAC的,那么必须先通过Dither(抖动)降低字长后或者直接就经过AC-Link接口传输到Codec,如果DAC字长不够AC-Link接口的高,那么它会自动将AC-Link接口超过字字长的LSBs(Least Significant Bit,最低有效位)去掉.DAC输出的是阶梯状或者是脉冲状信号,还必须经过LPF(Low Pass Filter,低通滤波器)滤波整形恢复为原来的音频信号。

2 FPGA音频编/解码系统结构

FPGA音频编/解码系统以ACEX1K和AD1881芯片为核心,如图3所示。

图3 FPGA音频编/解码系统图

ACEX1K-FPAG有147个用户可用I/O,系统门数最多257000,逻辑门100000.内部有4992个逻辑单元(LE),有12个嵌入式存储块(EAB),即49125位双口RAM.使用EAB构成的RAM、ROM、双口RAM和FIFO等结构可大大提高基于查找表(LUT)的算术运算、数字信号处理性能.在AC-Link音频编解码系统中,FPGA控制模块根据后向控制流,为音频编码模块提供多路帧同步信号。

AD1881是A/D、D/A接口芯片,支持AC′97标准接口,实现全双工16位立体声的音频编?解码,采样率7K~48KHz.系统复位完成FPGA 程序加载后,由FPGA的I2C总线模块对AD1881初始化,初始化结束后等待采集命令.初始化成功后,AD1881实时处理模拟音频信号。

用FPGA实现AC-Link声卡的D/A变换功能所需要的资源并不多,用一片ACEX1K100芯片做D/A转换,只消耗了30%左右的资源,在具体应用中,有时并不需要校验位及出错信号,则占用系统资源更少。

3 AC-Link音频编/解码的VHDL设计

FPGA中的AC音频编/解码设计是通过VHDL编程实现的.VHDL是一种应用非常广泛的硬件描述语言,它的语言覆盖面广,描述能力强;可以描述最抽象的系统级,也可以描述最精确的逻辑级、门级. AC-Link系统采用结构化VHDL进行设计的整个系统是一个VHDL语言文件,包括几个BLOCK语言.下面分别介绍各模块实现的功能。

(1)sreg1.vhd,调用一个并行输入、串行输出的模块,模块的核心程序如下:

if(clk’event and clk=‘1’)then ―时钟下降沿

if(s1=‘0’)then ―S1并行输入允许

tmpreg<=datain;

else

for i in sreg_width-1 down to 1 loop ―串行移位输出

tmpreg(i)<-tmpreg(i-1);

and loop;

tmpreg(0)<=se;

程序中,S1用来为sreg模块作为并行输入允许端.该信号在每个时隙的第一个数据位时出现,在此时,该时隙的数据被置入sreg模块,然后该模块开始串行移位输出,以后的各个时隙也按此过程工作。

(2)调用并行输入、串行输出模块,设计AC-Link.vhd.AC-Link的D/A转换控制器向编码器写数据,然后这些数据D/A转换成模拟信号,最后经功放输出

程序中对时隙的分配是采用IF_THEN_ELSEIF_THEN_ELSE_ENDIF语句实现,当计数器小于16时是第0时隙,以后每隔20个计数为一个时隙.使用CASE语句在不同时隙,输出赋以相应的数据。

对于AC-Link输入帧,如果控制器想从编码器读取数据或状态,就在bit_clk的上升沿把SYNC置高,编码器在bit_clk下降沿采样到 SYNC变化,然后在上升沿开始发送数据.控制器在每个bit_clk的下降沿采样数据,同时SYNC保持16个bit_clk周期的高电平。

对于AC-Link输出帧,如果控制器要向编码器输出数据或命令时,则在bit_clk的上升沿先把SYNC置高,然后在每一个bit_clk的上升沿发送一位数据,SYNC与bit_clk的上升沿同步.编码器在bit_clk的下降沿采样到SYNC的变化,由此编码器知道控制器要与它通信,在下一个 bit_clk的下降沿编码器开始采样数据,此后每一个bit_clk的下降沿采样一位数据.控制器发送数据是在bit_clk的上升沿,而编码器采样数据是在bit_clk的下降沿.同时SYNC也要保持16个bit_clk周期的高电平。

下列程序用于产生16个的bit_clk周期的高电平的SYNC信号,SYNC是bit_clk的256分频,有16个周期是高电平,其余时间是低电平。

if(conv_integer(counter)<16)then

sync<=‘1’;

counter:=counter+1;

else

sync<=‘0’;

counter:=counter+1;

endif;

进行VHDL设计时,最好各模块单独进行并及时仿真验证,以便尽早发现问题.系统中其它模块在此不再叙述.

图4 AC-Link输出仿真图

AC-Link接口的仿真图如图4所示,实现了其D/A转换功能,仿真通过以后,可将程序下载到FPGA中实现,同时直接与通令机连接起来进行调试,并利用计算机进行调试获得成功,计算机的通信软件可用VB或Delpi等可视化软件来编制。

4 结论

AC-Link音频编/解码系统的是在FPGA平台上用VHDL设计的.AC-Link设计采用自顶向下的设计方法,通过建立VHDL行为模型和进行 VHDL行为仿真,可及早发现设计中潜在的问题,缩短设计周期,提高设计的可靠性和效率.实践证明,仿真结果和FPGA实现符合AC-Link控制和编码要求.

|