1.引言

近年来,随着电子技术的飞速发展,复杂可编程逻辑器件(CPLD)得到了越来越广泛的应用。CPLD由一个“门”阵列和一个“或”阵列组成,任意一个组合逻辑都可以用“与-或”表达式来描述,因此可以使用CPLD完成各种数字逻辑功能。

本文基于便携式示波表的整体设计项目,针对如何采用CPLD实现示波器峰峰值采样的快速显示,提高系统效率进行了探索和研究。通过CPLD实现对液晶屏上同一列的多点显示是本设计的创新点。设计使用的CPLD足Altera公司出品的MAx IIEPM1270T144C5。

2.硬件总体设计

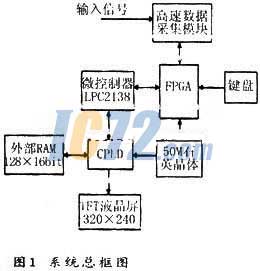

整个系统主要由高速数据采集模块,可编程逻辑器件FPGA,微控制器LPC2138,以及显示等四部分组成,系统框图1:

数据采样主要由高速模数转换芯片AD9480完成,实时采样率为250M,采样获得的数据存储在FPGA内部SRAM中。微控制器芯片采用嵌入式芯片LPC2138,主要负责对采样数掘的读取以及处理,然后传送到CPLD中。复杂可编程逻辑器件CPLD,对LPC2138传送过来的数据进行处理,将数据写入对应的外部RAM地址中。RAM的地址空间为128K,而显示屏液晶点数为320x240=76800、即75 K。RAM的地址与液晶点的对应关系为一对一。显示过程为CPLD通过定制计数器产生累加地址,读取RAM中数据,按显示屏时钟频率,每个时钟脉冲传送一个数据到对应显示屏位置进行显示,时钟频率为6.25MHz。

3.同列多点显示

3.1 设计思路

以往常用的示波表液晶屏显示方式是,波形更新时,微控制器通过逐点操作的方法,将每个点将要在屏幕显示的位置通过向RAM发送地址和数据来写入,再由CPLD的显示模块读取RAM数据进行显示。但是,当一次需要修改的点数较多,尤其是处于示波表的峰峰值显示方式时,如果仍采用微控制器进行逐点修改的方式,因为LPC2138控制芯片的操作频串不够高,代码命令行过多,将大大降低显示的更新速度,导致波形刷新率降低,不能将高速采样的结果适时呈现在屏幕上。因此,这里利用CPLD可灵活设计的特点,在峰峰值显示或者需要对同一列进行多点与操作时,只要通过LPC2138向CPLD发送该列的首地址和需写入点的个数,剩下的写操作全部由CPLD得用时钟节拍来完成,大大提高了波形显示的刷新速度。

3.2 显示节拍的安排

CPLD内部将系统时钟50MHz四分频,再四分频产生4个节拍,产生时钟节拍的框图如图2。

“CPLD读RAM时钟”由前3个节拍组成,是CPLD对RAM的读地址操作。 “显示时钟”由1、3节拍组成,等于液晶屏的显示频率,也等于CPLD的地址产生频率,由于是4个节拍里的2次不同的上升沿,所以频率为(50M/4/4)x2=6.25MHz.第4个节拍,是在写使能有效的情况下,将LPC2138发送的数据写入对应RAM地址。第2个节拍,就是我们这里用来进行同列多点修改时的时钟源。

3.3 同列多点显示模块设计

模块地址输入端的结构框图3所示。

ADD_IN[16..0]是微控制器发送过来的待写入RAM的列的首地址,EN是写使能控制信号地址作为锁存器的输入,锁仔器使能端由EN控制,当使能端有效时,锁存器输出端的“起始地址”等于ADD_IN[16..0]。在前面ADD IN[16..0]和EN还经过了一级D触发器来加强同步性,EN经过的D触发器有一个清零端,由READY信号控制,关于这个信号后面有详细说明。

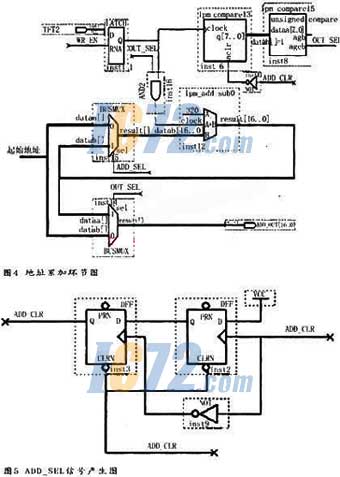

“起始地址”进入下面一级地址累加环节,用以产生同一列从上到下各点的地址,这是本设计的核心部分,其结构榧图如下:

“起始地址”进来后,遇到两个2选1的总线选择器,上面一个选择器的选择端信号是ADD_SEL,它选择进人累加环节的地址;下面一个选择器的选择端信号是OUT_SEL,它选择输出的地址是原始地址还是经过累加之后的地址。

地址累加的时钟源选择的是上一小节所述4个节拍中的第2个,其实从原理逻辑上讲使用第3个节拍也可以,但是考虑到数据传输过程中的延时因素,为了在笫4个节拍以前产生稳定有效的写地址,这里还是选择第2个节拍作为时钟源。时钟源前面加了一级锁存器,其使能端信号是上一个框图所示的WR_EN,这个信号相当于一个开关,为1时,运行后面的同列多点地址修改操作,地址累加;为0时,停止地址累加,始终输出原始地址。

加法器的时钟是时钟源和OUT_SEL信号相与后的输出,当两者同时有效时,才会产生高电平,OUT_SEL的产生将在后面说明。如图所示,计数器的时钟来自时钟源,当WR_EN有效时,计数器开始计数,计数器的位数这里限制在8位。因为根据示波表上的波形有效显示区域,同一列最多只需要显示199个点,而8位二进制数范围从0~255,已经可以满足显示要求。如果需要显示的范围更大,只要更改计数器输出位数即可。

计数器的输出接到一个8位比较器的输入端dataa[7..0],与datab[7..0]=1相比。这里设置与1比较是很重要的,当WR_EN有效时,模块开始工作,计数器时钟输入有效,第一个上升沿来到,计数器输出为0,经过比较器,0比1小, 因此ageb输出(a大于等于b)为0,即OUT_SEL为0,输出的第一个写地址为原始地址。第二个上升沿到来时,计数器输出为1,经过比较器,1等于1,则ageb输出OUT_SEL也为1,输出的第二个地址为累加一次之后的地址。以此类推,再往后的时钟沿始终使比较器输出OUT_SEL为1,输出的地址就是逐次累加后的地址。当一次同列多点写入完成后,有必要对计数器进行清零,以等待下一次操作到来,清零端信号为ADD_CLR经过非门之后的输入,ADD_CLR的产生将在后面描述。

由此可见,第一个时钟上升沿来时,加法器的输入ADD CLK无效,只有第二个上升沿来时,ADD_SEL选择原始地址作为加法器输入,加法器完成一次地址加320的操作,这里将加数定制为320是因为显示屏规格为320x240,每―行320个点,同一列上下一个点与上一个点的地址相差就是320。从第三个上升沿开始,ADD_SEL会选择修改后的地址作为加法器输入,以此实现地址累加。ADD_SEL信号产生的原理框图如下:

第二级D触发器的时钟是ADD_CLK经过非门的输出,这样做的结果是,在ADD_CLK的下降沿输出ADD_SEL等于1。结合上面的逻辑框图可以看出,第二_个时钟源上升沿到来时,即笫一个ADD_CLK上升沿,ADD_SEL为0,直到ADD_CLK的下降沿,ADD_SEL才变为1并一直保持,以此实现了上面所述的加法器地址输入的选择控制。

一次同列多点写入完成之后,会产生一个反馈信号READY供LPC2138查询,查询到READY有效,才进行下一次操作,否则等待。其结构框图如下:

NUM_IN[7..0]是微控制器发送给CPLD的同列修改点个数的数据,连接到8位比较器的一个输入端datab[7..0],比较器另一输入端dataa[7..0]则为前面所述8位计数器的输出。当计数器的输出夫于等于NUM_IN[7..0]输入时,ageb端输出为1,产生一个上升沿,使READY变为1,同时a1b也输出产生一个上升沿,使ADD_CLR信号变为1,这个信号用来对计数器进行清零。READY信号除了供微控制器查询外,还有一个作用就是对WR_EN信号禁用,使整个模块停止工作,直到微控制器发送命令ARM_CLR清除READY信号,模块才重新开始工作。

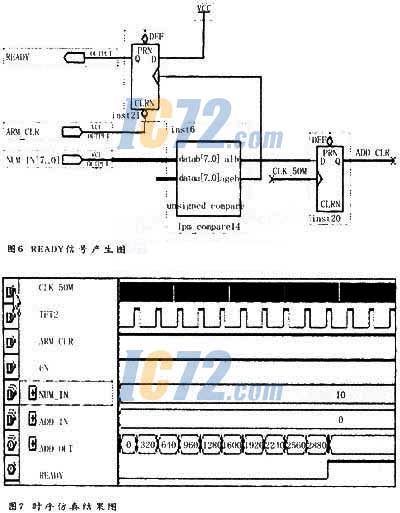

该模块的时序仿真结果如图所示,起始地址为0,列修改点个数为10,系统时钟50MHz,时钟源频率3.125MHz,占空比25%,ADD_OUT为模块输出地址:

前面均是关于同列多点修改的描述,当需要进行单点写操作时,只需让输入NUM_IN[7..0]等于0即可。

4.软件控制

LPC 2138对模块的控制很方便,通过编写C语言代码,在发送地址和计数次数数据前,先查询READY信号,如果有效则清除READY信号,并发送数据,之后又转入查询状态,以此循环。关于ARM_CLR信号,开始设计时专门由微控制器发送命令来产生,后为提高效率,直接用写使能信号(EN)产生,经测试可用。

5.结语

利用复杂可编程逻辑器件(CPLD)来实现对等待显示的同列多点的RAM写入是可行的。经过多次对方案的改进修正,目前的模块已经可以很稳定的工作,微控制器LPC2138对其的控制也简洁明了。如果需要进行同行多点的修改也可以采用这种设计方案,甚至将两者结合起来,通过一个控制端进行选择。这里因为主要应用在示波表峰值显示模式,故只采用同列多点修改的设计。

|