在设计大型FPGA信号处理系统时,设计师往往需要很长的仿真时间。FPGA设计工具(例如赛灵思的System Generator for DSP)通过提供稳固的硬件在环路(hardware-in-the-loop)接口,允许用户直接利用FPGA硬件进行设计仿真,从而解决仿真时间过长的问题。这些接口允许用户利用硬件进行部分设计仿真,从而在相当程度上加快了仿真速度(通常可达一个数量级或更多)。同时,利用硬件在环接口还使系统具备了实时FPGA硬件调试和验证功能。

System Generator for DSP提供适用于多种FPGA开发平台的硬件在环路接口,这些平台所提供的供PC机与FPGA硬件通讯的物理接口往往不同。例如,一个JTAG协同仿真接口就允许任何带JTAG接头的FPGA与赛灵思的FPGA在System Generator for DSP中进行协同仿真。有些其它板卡(例如XtremeDSP开发套件)则通过PCI总线与计算机进行通讯。到目前为止,仍然只有那些直接通过PCI或PCMCIA接口与PC机连接的开发板,能够进行存储带宽和数据吞吐量要求较高(例如视频和图像处理)的系统协同仿真。

通过以太网进行协同仿真

System Generator for DSP 8.1中包含一个新的以太网协同仿真接口,这个接口首次使赛灵思的ML402开发平台具备了高带宽协同仿真能力。ML402开发板可通过一根标准以太网电缆直接与PC机连接,或通过网络与PC机远程连接。

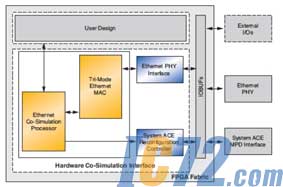

该接口的核心是赛灵思的三模以太网MAC核,支持10/100/1,000Mbps的半双工和全双工工作模式。当设计人员通过使用以太网硬件协同仿真接口生成一个设计时,System Generator for DSP将自动在设计周围建立必要的逻辑,从而在仿真的过程中通过以太网连接与FPGA进行通信(如图1所示)。

你还可以双击任意一个设计的System Generator模块打开它的参数配置对话框,从而生成一个用于以太网硬件协同仿真的设计。在编译菜单下,选择硬件协同仿真菜单下的ML402/以太网编译选项。此时,我们可以在以太网协同仿真的两种模式中选择一种。

图1:采用以太网硬件协同仿真接口的FPGA结构框图。

1. 基于网络的协同仿真

第一种模式是通过基于网络的接口进行协同仿真。有了基于网络的接口,我们就可以对一个连接到标准IPv4网络下的FPGA硬件进行协同仿真。标准IPv4网络如今几乎无所不在,因此,基于网络的接口就为我们提供了一种十分方便的方式,与一个连接到有线或无线网络的远程FPGA开发板进行通讯。这种接口在后台管理通讯和错误处理(丢包重传)的细节问题。System Generator for DSP则根据ML402开发板的IP地址决定在协同仿真时应该与哪一个平台通讯。

2. 点对点的协同仿真

第二种以太网协同仿真模式是一种点对点的接口,该接口使用原始的以太网帧来实现通过数据链路层与ML402板进行高带宽通讯。与基于网络的接口相比,点对点接口注重的是一个本地以太网段上的底层通讯。协同仿真的数据通过一根直接将ML402板卡连接到PC的标准UTP以太网电缆传输,因此要求PC机上必须具备可用的以太网插口。

点对点接口支持千兆位以太网标准,因而在配置成巨型帧(Jumbo Frame)时能够充分支撑大数据量传输的性能。采用这种接口之后,即便是对带宽最密集的应用也能进行协同仿真。

器件配置

以上两种以太网协同仿真接口均支持一种新的器件配置方法,即利用赛灵思的System ACE方案通过一根以太网电缆实现器件配置。配置过程与协同仿真采用相同的以太网连接,因而无需第二根编程电缆(例如赛灵思的Parallel Cable IV或Platform Cable USB)。ML402开发板上安装了一块CF卡,其中包含专用的引导载入程序(Boot-loader)镜像,在上电时会自动载入FPGA中。该镜像允许在仿真开始时,利用由以太网电缆送来的新FPGA协同仿真位流重新配置FPGA。整个配置过程均由System Generator for DSP透明处理。

设计举例

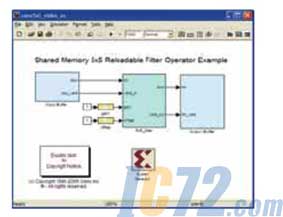

System Generator for DSP 8.1软件工具中包含一个名为conv5×5_video_ex的5×5滤波器算子设计模型。该设计向我们展示了如何利用n抽头的MAC FIR滤波器高效地实现一个二维图像滤波器。

图4:用于DSP5×5滤波器运算的系统发生器。

图5:System Generator for DSP5×5中滤波器视频流测试平台

图6:System Generator for DSP 5×5滤波器测试平台的结果

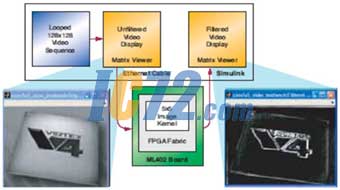

该设计中还包含一个硬件协同仿真测试平台,用于以实时帧速率通过其5×5内核传送一个循环视频序列(Looped Video Sequence)。在每个仿真周期都有一个视频帧被发送给FPGA进行处理,每个视频帧进入FPGA后都会由一个5x5的内核对其进行滤波,然后将其送回PC,由Simulink分析。仿真过程中,两个Simulink Matrix Viewer模块显示出未经滤波和已经滤波后的图像,通过测试平台的数据如图2所示。

图2:选用以太硬件协仿真作为系统发生器编辑类型。

基准测试

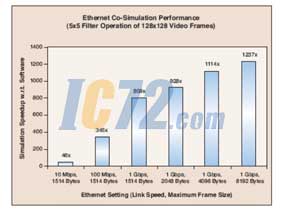

以上这个5×5滤波器设计的例子是针对点对点以太网硬件协同仿真进行编译的,并利用ML402开发板进行协同仿真。我们对硬件仿真速度与软件仿真速度进行了比较。测试基准特别考虑了每秒被读回的已处理的帧数目,并将得到的结果与对单个帧进行滤波操作所需的软件仿真时间进行比较。

图3总结了与纯软件仿真相比,以太网协同仿真所实现的仿真加速。结果表明,仿真速度提高了大约50~1,000倍。在现实设计中,仿真速度能够提高的程度会随设计复杂度、I/O口的个数以及I/O数据量等因素的不同而有所变化。图3还反映了与以太网设置相关的另外两个重要因素-链接速度与最大帧尺寸,这两个因素也会影响协同仿真的性能。

图3:指定ML402板的IP地址用于以太硬件协仿真。

随着网络连接速度不断增快,仿真时间会急剧缩短,因为可用于传送协同仿真数据的带宽将越来越大。由于千兆位连接允许出现巨型帧,因此通过增大最大帧尺寸还能进一步提升协同仿真的性能,从而保证实现最高效率的突发数据传输。

本文小结

System Generator for DSP的以太网硬件协同仿真接口为在ML402平台上仿真视频和图像处理应用提供了一个方便的高带宽方案。有了这些接口,我们就可以仿真远程FPGA平台,或者仿真一个通过以太网电缆直接连接到主PC机的开发板,从而提高仿真性能。利用SystemACE方案,还可以通过以太网连接进行器件配置,省去了第二根编程电缆。从测试结果中我们可以看出,这类接口可将仿真速度提升几个数量级。 |