本文向初次尝试设计XilinxVirtex-5 DDR2存储器接口的工程师介绍一些窍门,包括关于首选电路拓扑的快速指南,以及采用数控阻抗(DCI)片上终端元件来替代外部终端电阻的利弊概述。此外,本文还介绍了从以往设计中积累的实用设计指南和IBIS仿真结果。

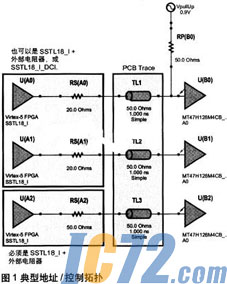

存储器接口电路拓扑图1和图2分别显示了适用于DDR2地址/控制和数据线的可行拓扑图。在双向数据线上,存储芯片作为驱动器,而Virtex-5器件则充当接收器,以便利用FPGA的DCI。图1中最上方的示意图显示了Xilinx推荐采用的模型,而另外两个图则为常规设计中经常采用的其它拓扑。

图3和图4分别对应于图1和图2电路拓扑的典型接收器眼图。接收器的输入信号切换阈值(threshold)如蓝色水平虚线所示。图1和图2中“指针”的颜色分别对应于图3和图4中的相关迹线。这些眼图是利用Mentor Graphics公司的HyperLynx软件生成的,其参数设置如下:伪随机二进制序列(PRBS),位序为7(序列长度为127);位间隔(bitinterval)=1.5 ns(667 Mbps);单序列重复;跳过前50位;未增加抖动。

观察图3中的迹线,可以发现,存这三种拓扑中,推荐使用的模型生成的眼图轮廓最为清晰。

图1中部示意图所示为DCI新手最常犯的错误――认为只要采用SSTL18_I_DCI驱动器,就无需使用任何其他外部终端元件。有些DCI用户常常误以为“_DCI”型SSTL(残余连续端结逻辑电路)驱动器系列中的器件能够调节自身的输出阻抗,以匹配DCI校准电阻,因此可以用作传输线的阻抗匹配驱动器。

但事实并非如此。例如,SSTL18_I_DCI输出驱动器的固定输出阻抗约为20Ω(如SSTL18技术规范)。图3中的黄色迹线清楚地表明了这种错误假设的灾难性后果。不仅眼图明显变窄,而且接收器输入端还出现了棘手的过冲/下冲现象。

只要将串联终端增至50Ω(如图1下部所示),就可以成功地避免过冲/下冲现象,但仍然不能使眼图恢复初始宽度。因此,应当始终在所有地址/控制线的末端采用并联终端。

如果没有适当的终端电压源可用,那么,可以在VCCO电源端和接地端之间串联两个电阻(每个电阻的阻值为所需阻抗的两倍),来形成一个戴维宁等效(Thevenin-equivalent)终端。在这种情况下,只需要将地址/控制的末端连接至包含这两个电阻的电路。请注意,采用这种端接方式时,电路的功耗会增加,因为VCCO电源的固定负载是两个电阻。

图4的数据线眼图也表明,拆下数据线末端的并联终端后,将产生不能接受的过冲/下冲现象。然而,在这种情况下,拆下串联终端似乎可以改善眼图,使之变宽,并有助于进一步抑制噪声,同时不会产生过冲/下冲。这个例子也提醒大家,盲目地遵从推荐使用的模型、经验法则或一般性指南,还不如对设计进行模拟来得有效。

请注意,在执行移除串联终端电阻的工程修改命令(ECO)之前,应当反转Virtex-5器件的数据线,将数据输出到外部存储器,并检查眼图来确定信号完整性(SI)是否良好。

为何使用DCI?

对比于等效外部终端,DCI拥有诸多优越性。例如在采用DCI的设计中,终端更加靠近输入端,因此可以存接收器输入端实现更好的SI。此外,使用DCI就不必再使用外部终端元件,从而缩小了PCB尺寸,减少物料单(BOM)中元件的数量。

使用DCI时应注意:阻抗随工艺、电压及温度(PVT)的变化而变化;功耗更高。

在采用DCI的设计中,作为终端阻抗的是CMOS晶体管,因此,阻抗会随FPGA的制造工艺、电源电压和工作温度(PVT)的不同而变化。于是,必须以终端阻抗的最高值和最低值执行两次系统级仿真,以确保系统在任何可能的PVT组合条件下都能正常运行。

在适当的终端电源电压条件下,在传输线末端采用DCI实现并联终端产生的功耗,高于采用外部电阻的设计。在这种情况下,可以将传输线的末端先连接上阻抗与传输线特性阻抗相等的电阻,再连接到电源上,并且不得在电源轨上安装任何负载。

相反地,如果采用DCI对传输线进行端接,则应利用两个传输晶体管(pass transistor)将接收器输入端分别连接至VCCO电源端和接地端。调整各个晶体管的有效阻抗,使其等于传输线的特性阻抗的两倍,以产生Z0到VCCO/2的戴维宁等效终端阻抗。

这种端接方式的副作用是会在电源轨上增加4Z0的阻抗,从而提高系统总功耗。如果系统架构设计的技术规范中并未提供VCCO/2的电源,那么使用DCI就不会发生功率损耗,因为不论在哪种情况下端接方式都必须是戴维宁等效终端。

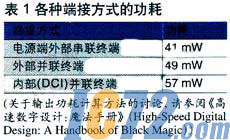

表1列出了在一条传输线上,三种端接方式的输出功耗:电源端串联、外部并联(假定有VCCO/2的电源)和内部并联(DCI)。

结语

本文分析了DDR2存储器接口电路拓扑以及多种其他电路拓扑形成的接收器眼图。读者应当明白,在设计DDR2存储器接口时,必须利用HyperLynx之类的IBIS仿真器进行系统级仿真。将来,随着存储器接口速率的日益提高以及I/O接口电平的不断下降,读者可以运用本文介绍的一般原则,设计更加复杂的存储器接口。

|