要 点

迅速的特性改进和低价格使 x86 CPU 在许多非 PC 设计领域很有吸引力。

在于 2005 年降至市场份额低点后,英特尔在最近几年有力地恢复了元气。

英特尔的数次挫折使 AMD 在本世纪初期时来运转,两家公司后来轮流上演成功和失败的故事。

威盛电子率先专注于成本和功率,其它 x86 供应商也在日后采取了这一策略。它的一种超标量乱序 CPU 终于要问世了。

那些考虑把 PC 构件用于非 PC 设计的人最好记住:把宝押在 PC 技术上并非完全正确。在这个体系结构方向经验丰富的同行们已经了解这一点。一方面,人们将受益于 PC 行业特有的迅猛创新速度,以及全球每年销售的数亿台 PC 带来的低价格。另一方面,这样的创新速度还导致了迅猛的报废速度,这对于那些生产周期超过六个月的系统而言可能会有问题 假设人们在自己的设计中构建了足够的采购灵活性,来包容供应的无常性,那么为 PC 量身定做的微处理器可以以合算的方式实现系统的性能目标。并且由于 PC 行业十分注重功耗,因此电池寿命、电源尺寸、散热也不像以前那样令人担忧了。不过,传统的 CPU 和 DSP 供应商在面对 PC 处理器的冲击时并未无动于衷,并且他们的替代解决方案在许多情况下依然是最优的。如果人们充分了解主要 x86 CPU 供应商的历史、当前状况和未来计划,就能评估将为各自的下一项设计走哪条道路(见附文1《Montalvo是何方神圣?》)。

英特尔:回归正轨

一家公司的命运会在短短五年内发生多大的变化?英特尔公司就是例子。在本世纪初,英特尔把其整个微处理器产品线(从笔记本电脑到服务器)都基于 NetBurst 微体系结构,只有 Itanium 处理器例外(见附文2《补充说明》)。NetBurst 有冗长的管线――在最初的 180 nm Willamette 变型中有 20 级,而在最后的 90 nm Prescott 和 65 nm Cedar Mill 迭代型号中扩展到多达 31 级。当代码特征与可预测度高的多媒体指令流相配时,这些管线表现很好。但是任何长管线方法中固有的低 IPC(每时钟指令数)属性,连同实质性的分支预测错误劣势,使 NetBurst 在更常规代码方面的性能令人提不起兴趣。并且在竭力提高时钟速率补偿长管线的劣势时,英特尔在 90 nm 工艺节点开始遭遇实质性的泄漏电流问题,这使该公司的 NetBurst 产品比最初的 10 GHz 微体系结构目标少了 6.2 GHz。(事实证明,即便达到 3.8 GHz 也是个艰难的项目。)

英特尔的命运从移动计算领域开始柳暗花明,当时在 2003 年春天,它推出了 Pentium M 微体系结构的第一个 Banias 迭代型号(参考文献 1)。Banias 是用 130 nm 工艺制造的,先于 90 nm 的 Dothan(具有更大的 L2 缓存)和 65 nm 双核 Yonah(具有共享 L2 缓存)问世(参考文献 2)。Pentium M 充分利用并扩充了 Pentium III 的执行单元,并把它和 Pentium 4 总线接口结合起来。这样,借助常规的代码迹线,按照每时钟比较,它提供了比 NetBurst 更高效的功率和指令。Yonah 代 CPU 没有使用前身的 Pentium M 品牌,而采用了酷睿 (Core) 营销名称(稍后的事实证明这有些令人困惑),当时该公司推广了一套基于 65 nm 工艺的 Merom、Conroe 和 Wolfdale CPU,分别涵盖了笔记本电脑直到服务器,并充分利用了后继的 Core 微体系结构,该公司在营销后者时使用了酷睿 2 (Core 2) 促销品牌。

英特尔目前正在发售其 Core 微体系结构的第二个迭代型号(名为 Penryn),它采用 45 nm 工艺蚀刻技术制造该产品。Penryn 反映了该公司的 tick-tock 战略,这是一种涉及较小蚀刻产品的布节奏,只有一些次要的相应特性调整(称作 tick),大约一年后在共同的工艺基础上做更实质的体系结构修改(称作tock)。

这样,与目前的Penryn tick对应的tock――Nehalem――在今年投产,并且英特尔正在以原型系统的形式公开演示该产品。Nehalem 将着手解决长期遭到AMD批评的几个问题,尽管迄今几乎没有任何基准测试表现出真实性能缺点方面的结果。通过目前的 Penryn 产品,所有核心间通信――不论是在晶粒内,多晶粒单片封装 CPU 内的晶粒之间,或是封装 CPU 之间――都通过同一前端总线(它承载通往外部子系统以及来自它们的数据通信)发生,只有晶粒内的共享缓存一致性同步例外。主要的外部子系统是核心逻辑芯片组,在如今的设计中,它包含 DRAM 控制器。

诸多性能

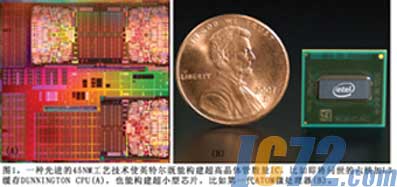

Nehalem级CPU集成了专用 QuickPath Interconnect 跨处理器,即从前的CSI(公共系统接口)。该链路在概念上让人回想起 HyperTransport 链路,后者是 AMD 于 2001 年推出的,用于一颗晶粒上的多个核心之间以及多晶粒 CPU 和封装 CPU 之间的通信。基于 Nehalem 的产品还会让人回想起 AMD 公司于2003年凭借 Athlon 64和Opteron K8(也称作 Hammer)CPU率先推出的技术,这些产品嵌入 DRAM 控制器的目的之一是降低延长的等待时间。目前,当由于缓存遗漏 (cache miss) 而需要访问外部存储器时,系统就会经历上述等待时间。谈到缓存,目前的英特尔产品把多颗晶粒组合在共同的封装罩之下,由此使核心数量超过两颗,而 45 nm 工艺可承受的庞大晶体管预算将使该公司能以单片形式把至少六颗 CPU 核心压缩到基于 Nehalem 的 Dunnington 芯片的单一薄片上(图 1)。正如当前其它产品那样,每对核心共享一块公共的 L2 缓存,并且所有六颗核心分用布局孔中的一块公共 L3 缓存,布局孔还可供第四对双核进入。

45 nm工艺使英特尔不仅能构建合算的大晶粒产品,而且能构建非常合算的小晶粒处理器。这种成本有效性是 Atom CPU 产品线的推动力,英特尔公司于今年四月初在上海英特尔开发者论坛上正式推出了上述产品(参考文献 3)。Atom 以前被称作 Silverthorne,结合了一种单片配套器件,英特尔以前把这种芯片组称作 Menlow。Atom 起源于正在开发并基于 x86 的 Larrabee PC 协处理器,后者预定用于图形、成像、物理和其它功能。英特尔的体系结构设计师断定:他们需要能够合算地把 16 或更多 x86 核心嵌在单一 Larrabee 晶粒上,并且断定:该公司的主流 CPU 的乱序执行和其它奇特属性应对目标应用绰绰有余。结果,英特尔“回到了未来”,重新启用它的 Pentium III 原理图为 Larrabee 提出面积优化的 CPU 核心设计。该公司正在试图另外开发具有很少物理核心的芯片,它们基于 Larrabee 原子构件,一些还具备 HyperThreading 虚拟多核支持,用于对功率和成本敏感的移动系统。而这么做是为了使投资回报最大化。

第一代 Atom CPU 有五个版本,时钟速度达到 1.86 GHz,TDP(热设计功率)范围是 0.65 W~ 2.4 W。相应的平均功率和闲置功率范围分别是 160 mW~至 220 mW 和 80 mW~ 100 mW。配套的系统控制器中心有三个版本,特性包括 3D 图形核心、硬件加速高清视频解码引擎、 高清音频处理,以及支持 PCI Express、USB、SDIO(安全数字输入/输出)连接。并且英特尔考虑了长寿命周期嵌入式系统设计,许诺了至少七年的产品支持。一个列入计划的双核 Atom 变型在低成本笔记本和台式系统领域将更加引人注目,并且英特尔还为明年计划了集成度更高的单片但可能多晶粒的 Moorestown Atom 家族。总而言之,在数年磕磕绊绊之后,英特尔似乎回到完全的大步发展阶段了。对于这个十年的余下时间,该公司路线图的最大问题也许是 Atom 将在多大程度上以一种财务方面对英特尔毫无吸引力的方式拼用公司自身的产品,而不是像英特尔希望的那样,通过挤压 ARM 等竞争对手拓宽 x86 市场。

AMD:去向不明

主要竞争对手英特尔在本世纪的最初五六年艰难挣扎,AMD抓住了这个有利时机。该公司的 K7 Athlon 微处理器是 1999 年推出的,事实证明是一种比英特尔一年后推出的基于 NetBurst 的 Pentium 4 更为常规的体系结构,因此从性能和功耗角度看,时钟效率非常高。英特尔多年来一直试图把 64 比特系统市场推向其专有的革命性的 Itanium 处理器――大部分都失败了,只有超高端配置例外,而 AMD 选择了一条更具演变性的途径――在 Athlon 基础上追加 64 比特指令支持。结果便是 2003 年基于 K8 的 Athlon 64 和 Opteron(参考文献 4)。K8 CPU 还提供了其它关键的演变性增强特性,比如 HyperTransport 链路和集成式系统存储器控制器。从 2005 年推出的多核 Opteon 和 Athlon 64 X2 来判断,AMD 还是第一个将多核 x86 CPU 推向市场的,至少从单片晶粒角度看是这样。

然而,最近几年却暴露了 AMD 的主要弱点:该公司是一家比英特尔小得多的 x86 市场参与者,无论是从员工人数还是市场份额衡量标准看均如此,因此它从事的每个项目的成败都比较关键。AMD 于 2003 年开始针对 K10 微体系结构探讨体系结构目标,并且于 2006 年公布了它以 64 nm 工艺为目标的单片四核 Opteron、Barcelona 以及 Athlon 后继型号 Phenom 的主要细节。AMD 最终把 Barcelona 的推出延期到 2007 年 9 月,然后进一步把全面生产发售推迟到两个月前,而在此前,该公司修复了一个令人尴尬的 L2 缓存 TLB(转换旁视缓冲器)缺陷,这是在 Barcelona 推出后发现的,并与 Phenom 的公布时间巧合。

AMD 在修复 TLB 缺陷之前发售了一些 Phenom 材料,伴随一份基于 BIOS 的微代码补丁,后者有一个令人遗憾的副作用――显著降低了与许多基准相关的性能。并且前沿的 Opteron 和 Phenom CPU 在部分程度上反映了 AMD 落后英特尔一代工艺的事实,它们运行时,在核心时钟速度和基准方面均落后英特尔同等产品。一方面,AMD 很熟悉这种情况。正如它在上世纪 90 年代中期的 P(性能)评级体系所暗示的那样,与英特尔提供的产品相比,它的产品早就表现出较低的时钟速度,而时钟使用效率更高。不过,尽管在本世纪的最初几年,AMD 与英特尔基于 NetBurst 的 CPU 旗鼓相当,但它眼下是在和 Core 衍生的出众的后继产品竞争。AMD 处理器的 HyperTransport 链路和集成式 DRAM 控制器弥补了时钟速度的部分不足,但它们无法完全弥补缺口。并且,在 AMD 预计向市场推出基于 45 nm 的 K10 后继产品时,英特尔也预告了将投产首批 32 nm Westmere CPU,由此保持蚀刻技术领先一代的优势。

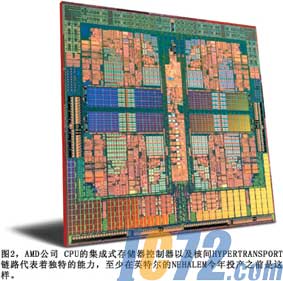

这个消息尽管令AMD烦恼,但对 AMD 并不全是坏事。尽管该公司积极的定价方式对产品利润率的影响不为人知,但在它的芯片性能和功耗特性使它能获得相当影响力的市场领域,已使它能对英特尔保持很强的竞争力。凭借 AMD 基于 HyperTransport 的核心互连方法,以及 K10 设计从一开始就包含的其它有吸引力的特性,AMD可以把一些部分程度有缺陷的晶粒作为三核 Phenom 芯片发售,由此使每片晶圆的收入最大化(图 2)。AMD也在把其基于 K8 的双核 CPU 转向 65nm 工艺,这应该会提高晶粒/晶圆使用率,也有利于AMD的专用产能和代工厂产能的结合。

与英特尔一样,AMD 出售一些嵌入式产品,它们具有延长的寿命周期保证、增强的测试,以及非 PC 客户重视的其它属性。并且 AMD 还继续出售 Geode 集成式 x86 系列,这是它于 2003 年从 National Semiconductor 公司收购的,其历史可追溯至 Cyrix MediaGX。(National Semiconductor 公司于 1997 年收购了 Cyrix 公司。)虽然 AMD 未正式就 Geode 的未来计划发表评论,但最新公开的产品变型 Geode LX 可追溯至 2005 年,而且该公司在 2006 年就关闭了它的 Geode 设计中心。

威盛电子:斗志旺盛的受压迫者

威盛电子长久以来一直作为核心逻辑芯片组供应商为人熟知,在 1999 年 9 月也成为了 CPU 制造商,当时它收购了 IDT 的 Centaur Technology 子公司。(威盛还于 1999 年 9 月收购了 National Semiconductor 公司专门面向 PC 的 Cyrix 资产。)从一开始,Centaur 就始终专注于为常规应用尽量减小晶粒尺寸和功耗,并竭力交付足够性能。这个立场在该公司的早年引起了争议,当时“时钟速率就是一切”的观念主导着这个行业,但现在Centaur的思想已变得更加主流了。

该公司的一系列 C3 代 CPU(在无风扇配置中称为 Esther),目前主要是派生自 Nehemiah 核心,尽管威盛把较老的 Samuel 2 设计作为某些 C3 产品的基础(参考文献 5)。Nehemiah 具有多种通用体系结构增强特性,比如全速浮点单元、更深的管线、更全面的 MMX 实现,以及从 3DNow! 改为由 SSE 增强的多媒体指令集。Nehemiah 还瞄向了嵌入式系统设计,比如一对基于发热的硬件 RNG(随机数发生器)。 威盛把这些 RNG 称作 PadLock RNG,并在日后的一种普及产品中称作 AES(高级加密标准)引擎,即 PadLock ACE。还提供单片 CoreFusion 产品,在统一封装中结合了Nehemiah CPU 和北桥核心逻辑晶粒。

对于更常规的台式机和笔记本设计(比如惠普公司最近推出的 2133 型 Mini-Note PC)以及更高端的嵌入式系统应用(无论是否有风扇),威盛还提供 C7 级 CPU(图3)。该公司采用合作伙伴 IBM 公司的 90 nm SOI(绝缘硅)工艺构建上述产品,并提供增强的 PadLock 功能。威盛的文档描述道:“威盛C7处理器中的Via PadLock Security Engine 添加了SHA(安全哈希算法)-1和SHA-256哈希法实现安全信息摘要,还添加了基于硬件的蒙哥马利乘法器,它支持长达 32kB 的密钥长度来加速公共密钥加密法,比如 RSA (Rivest/Shamir/Adleman)。威盛 C7 还提供 NX 执行保护,由此提供针对蠕虫和病毒等恶意软件的保护。并且它可用于带 SP2 的 Microsoft Windows XP。把安全特性直接集成到处理器晶粒上,可确保达到比软件高许多倍的速度和效率,而对处理器性能的影响可忽略不计。”

威盛CPU家族的多种配套芯片组反映了该公司长期积淀的核心逻辑技术,提供了系统设计灵活性,具有若干集成的选项,比如 2D 和 3D 图形加速,以及硬件加速的 MPEG-2、MPEG-4 解码和其它视频编解码器。外部接口选项包括单倍数据速率 SDRAM、多代双倍数据速率 SDRAM、并行和串行 ATA 海量存储、PCI 和 PCI Express 插卡,数量不等的 USB 端口。

许多 C3 和 C7 CPU 普及产品共同的 21 mm×21 mm NanoBGA2 封装高效利用了可用的系统板空间。谈到系统板,如果人们更希望不做自己的设计,则威盛将很乐意向他们出售它的某种 6.7"×6.7" (170 mm×170 mm) mini-ITX、4.7"×4.7" (120 mm×120 mm) nano-ITX 或 3.9"×2.8" (100 mm×72 mm) pico-ITX 板。它们有效缩小了 PC 主板,采用多种 CPU、核心逻辑芯片组和配套芯片组合,其中包括 10/100-MB Ethernet 和 GbE 收发器、超过双声道的环绕立体声模拟和数字音频、TPM(受信平台模块)、IEEE-1394 接口 IC、模拟视频编码器,以及 DVI 和 LVDS 数字视频输出。

mini-ITX 形状系数是威盛于 2001 年公布的,是三种选项中最成熟的,并且该公司成功地把它作为行业标准来宣传,这吸引了竞争对手的注意。第三方伙伴出售基于 AMD 和英特尔 CPU 的 mini-ITX 板,并且英特尔也制造自己的 mini-ITX 产品。值得关注的是,该公司在最近数月的多个公共论坛上展示了几种基于 Atom 的 mini-ITX 设计。

谈到 Atom,威盛与之竞争的 CPU Isaiah对于该公司的未来生存能力很关键。具有讽刺意味的是,英特尔已从它以前的体系结构中取消了乱序执行和其它多余特性,由此产生的做法在一定程度上让人回想起 Centaur 将近十年前的构想。相比之下,威盛的子公司 Centaur 的总裁 Glenn Henry 及其设计团队正在准备推出威盛的第一种三路超标量乱序体系结构。该公司于今年一月末正式公布了 Isaiah。它还增加了对 64 比特指令的支持、硬件虚拟化,以及目前具有竞争力的 CPU 的其它急需特性。威盛最初将采用代工厂的 65 nm 蚀刻技术制造 Isaiah,其中的设计目标包括:在同等时钟速度,整数性能是 C7 的两倍,浮点性能是其四倍。

Isaiah的65nm 功耗目标是:2GHz 时为25W TDP。威盛目前把首批基于 Isaiah 的产品安排在今年二季度生产,这比最初公布的时间表差了一个季度。当人们阅读本文或在稍后的时间,该公司应该在发售这些芯片了。威盛将为该 CPU 提供配套的核心逻辑芯片组。一个有趣的伙伴关系也许反映了该公司在 AMD 和英特尔瞄准的核心逻辑市场中日益减少的市场份额。按照该伙伴关系,Nvidia 也将销售为 Isaiah 量身定做的芯片组。 |