1��Modelsim��FLI�ӿڽ���

Modelsim��ModelTechnology��MentorGraphics���ӹ�˾����HDLӲ���������Է�������������ʵ��VHDL,Verilog���Լ�VHDL-Verilog�����Ƶķ��档

����֮�⣬Modelsim���ܹ���C����һ��ʵ�ֶ�HDL����ļ���Эͬ���档ͬʱ������ڴ������HDL����������˵��Modelsim�ڷ����ٶ���Ҳ���������ơ���Щ�ص�ʹModelsimԽ��Խ�ܵ�EDA����ߡ�������FPGA����ߵ�������

Modelsim��FLI�ӿڣ���ForeignLanguageInteRFace���ṩ��C���Զ�̬���ӳ�����������Ľӿڣ�����ͨ��C���Ա�̶�����ļ����и������档

2��Эͬ����ϵͳ�ṹ������

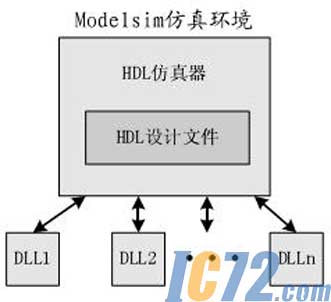

Эͬ����������÷��湤���ṩ���ⲿ�ӿڣ�����������������ԣ���HDL���ԣ��ȣ���̣��������湤�߽��з��档Modelsim�ṩ����C���Ե�Эͬ����ӿڡ���Windowsƽ̨Ϊ�����û�ͨ��modelsim�ṩ��C���Խӿں�����̣����ɶ�̬���ӿ⣬��modelsim������Щ��̬���ӿ���и������棨ͼ1����

ͼ1Эͬ����ʾ��ͼ

Modelsim��C����Эͬ����һ�����ڲ������������������ֹ���д���������ķ��������ǿ��Ը��ݳ���������Զ�����������ȷ�������ģ������ģ�飨��RAM���Ĺ��ܣ���ϵͳ��������ļ����档ʵ����һ���ǰ�һ�Ͷ������һ���ó����������������һ�������������ļ���Ϊ���룬��һ�����ɳ������Ը��������㣬�ѵõ��Ľ������������������Ƚϣ�������Ƿ���ȷ��ͼ2��������ģ��ܣ������Ѿ���һЩͨ��оƬ��ģ�������denali����ģ��RAM�Ĺ��ܡ����⣬�û�Ҳ��������modelsim�ṩ�ı�̽ӿ��Լ�ģ��һЩоƬ����Ϊ��Ȼ��������ļ����ӵ�һ����档

ͼ2���Բ��Գ����VHDL��Ƶ�Эͬ����ṹͼ

3��C���Զ�VHDL��Ƶ�Эͬ����

3.1���ɿ�ͼ

�����ļ��Ĺ�����ͼ3��ʾ������HDL�ļ��Ͷ�̬���ӿ⣨��C����ͼ��C�����Ӧ��VHDL�ļ�Ҫ����������Ӧ�Ķ�̬���ӿ��ļ�������ʼ��������������Ը���һЩ���ò�������̬���ӿ����õ�����������ź�ҲҪ�ڶ�Ӧ��VHDL�ļ���������

ͼ3�����ļ�����ʾ��ͼ

���磬�ٶ���һ��DLL�ļ���Ϊsim.dll,��Ӧ�ij�ʼ������Ϊsim_init���������ź�in1��in2������ź�out1��out2������������д��Ӧ��VHDL�ļ�(sim.vhd)��

libraryieee;

useieee.std_logic_1164.all;

entitysimis

port(

in1:instd_logic;

in2:instd_logic;

out1:outstd_logic;

out2:outstd_logic;

);

endentitysim;

architecturedllofsimis

attributeforeign:string;

attributeforeignofdll:architectureissim_initsim.dll��

begin

end;

����ʱ���������Զ����HDL�ļ����з��棬�����ݸ�VHDL�ļ��Ķ�̬���ӿ����������á�ִ����Ӧ�Ķ�̬���ӿ⡣

3.2��̬���ӿ�ij���ṹ

modelsim�ڷ���ʱ������VHDL�ļ�������������DLL�ļ�����sim.dll������VHDL�ļ����Ѿ������˵����ļ�(sim.dll)�ͳ�ʼ������������sim_init����modelsim������Щ��Ϣ������sim.dll�е�sim_init��������ɳ�ʼ����������ʼ��������

1.��ʼ��ȫ�ֱ�����

2.����VHDL��������ź���C��������Ķ�Ӧ��ϵ��

3.��������źŵ�һЩ��ʼ״̬��mti_ScheduleDriver����

4.�����ڷ��������·��棨restart���ͷ������˳����棨quit���������ִ�е�һЩ������mti_AddRestartCB��mti_AddQuitCB�ȣ������ͷŶ�̬������ڴ�ȵȣ�

5.�������б���������ijЩ�źŷ���ijЩ�仯����ʱ�������صȣ�ʱִ�еĺ�����

6.�ȵȡ�

������3.1�����ӣ�sim.vhd��������C�������Ʋ��衣

1.����ͷ�ļ�������C�����õ�һЩͷ�ļ���Modelsim�������ⲿ���Խӿ�ͷ�ļ�mti.h��Modelsim�������ⲿ�ӿں���˵�������Ͷ���ȶ���mti.h�С�

2.�����Լ��Ľṹ�壬��һ����Ҫ��Ϊ�˱�̷��㣬������������źŶ�Ӧ�ı����ڸ������л����϶����õ���������Щ���������һ���ṹ�����ڲ������ݡ����磬���ǿ���3.1��sim.vhd��������źŶ�Ӧ�ı�������ɽṹ��

typedefstruct{

driverIDout1;

driverIDout2;

signalIDin1;

signalIDin2;

}PortStruct;

����driverID��ʾ����źŶ�Ӧ�ı�����signalID��ʾ�����źŶ�Ӧ�ı��������������ﶨ��ı���out1,out2,in1,in2�ͷֱ���sim.vhd�е��ź�out1,out2,in1,in2��Ӧ��

3.3��д��ʼ������

��ʼ�������Ķ���Ϊ��

init_func(mtiRegionIdTregion,char*param,mtiInteRFaceListT*generics,mtiInterfaceListT*ports)

�������ĺ�����Բ���modelsim���û��ֲᡣ

��������������ij�ʼ������Ҫ��ɵ���������ϸ˵����

a.��ʼ��ȫ�ֱ������ԣ�

b.����VHDL��������ź���C��������Ķ�Ӧ��ϵ������ͨ������mti_FindPort����ʵ�ֵġ�mti_FindPort��������Ϊ��

mtiSignalIdTmti_FindPort(mtiInterfaceListT*list,char*name)��

���磬������������źŶ�Ӧ�ĽṹΪip:PortStructip;

�Ϳ����ã�ip.in1=mti_FindPort(ports,��in1��)����ʵ�������ź�in1�����in1�Ķ�Ӧ��ϵ��

������ź���˵������Ŀ���Dz�����������ˣ���Щ������out1��out2������Ҫ�ҵ���Ӧ������ź��⣬��Ҫ������Щ�źš����źŵ���������ͨ������mti_CreateDriver������ʵ�֡��ú����Ķ���Ϊ��mtiDriverIdTmti_CreateDriver(mtiSignalIdTsig)��

������Щ����һ��ֻ���ڶ�����������˿��Լ�д���������ʽ��

ip.out1=mti_CreateDriver(mti_FindPort(ports,��out1��))��

c.����mti_ScheduleDriver��������������źŵij�ʼ״̬��mti_ScheduleDriver�����Ķ���Ϊ��voidmti_ScheduleDriver tiDriverIdTdriver,longvalue,mtiDelayTdelay,mtiDriverModeTmode)��

����driver������źŶ�Ӧ�ı������������������ip.out1��ip.out2��value��Ҫ���ã���������ֵ����ߵ�ƽ(��1������ӦvalueΪ3)���͵�ƽ(��0������ӦvalueΪ2)������(��Z������ӦvalueΪ4)��δ��ֵ(��U������ӦvalueΪ0)�ȵȣ�delay�Ǵӵ�ǰʱ�俪ʼ�����ź������ɸ���ֵ��value���ĵȴ�ʱ�䣬��λ���������ǰʹ�õ���Сʱ�䵥λ��ͬ��modeΪ�ź�ģʽ��������ֵ�ɹ�3ѡ��MTI_INERTIAL������MTI_TRANSPORT���ֱ��Ӧ�ڱ�VHDL���Ե�INERTIAL��TRANSPORT�����磬���������ź�out1�ij�ʼ״̬Ϊ�͵�ƽ��mti_ScheduleDriver(ip.out1,2,0,MTI_INERTIAL);

d.�����ڷ��������·��棨��������restart�����˳����棨��������quit�Csim��������µ��õĺ�������һ������Ҫ��Ϊ���ͷ��ڴ���߱��浱ǰ״̬�ȡ���restartΪ�������������ڳ�������malloc�����˴洢�ռ�buf���ڷ�������restart��ʱ��Ҫ�ͷţ��Ϳ��������µĺ���������ע�mti_AddRestartCB(free,buf)��

��ע�����������������restartʱ�ͻ����free(buf)��

����һЩ�������Բ���Modelsim���û��ֲᣬ���ﲻ��������

e.�������б���������ijЩ�źŷ���ijЩ�仯ʱ����ʱ�������صȣ�ִ�еĺ��������磬�������ź�in1�����仯ʱ��Ҫִ�к���in1_change��in1_changeΪ�û�����õĺ������������������壺

processIDproc;

proc=mti_CreateProcess(P_in1change,in1_change,&ip);

mti_Sensitize(proc,ip.in1,MTI_EVENT);

Ҳ����˵���ȴ������̣�Ȼ���������б������������б�������ʱ���������ͻ�ִ�иý��̡�

mti_CreateProcess�����Ķ���Ϊ��mtiProcessIdTmti_CreateProcess(char*name,mtiVoidFuncPtrTfunc,void*param)��

name���ڷ�����������ʾ�����ƣ�func��ִ�еĺ����������param�Ǵ���func�IJ�����mti_Sensitize�Ķ��壺

voidmti_Sensitize ProcessIdTproc,mtiSignalIdTsig,mtiProcessTriggerTwhen)��

����procΪ����mti_CreateProcess�ķ���ֵ��sigΪ�ź�������VHDL�ļ�����������źŶ�Ӧ��C����ı�����when����ȡMTI_EVENT����MTI_ACTIVE����ֵ��

3.4C����ı���

��Windowsƽ̨�����õı�������MicrosoftVisualC++���������µ������н��б��룺

cl-c-I\modeltech\includeapp.c

link-dll-export:app.obj\modeltech\win32\mtipli.lib

�������modelsim�İ�װĿ¼����C����ij�ʼ���������������Ǹ�����sim.c�е�sim_init������֮��Ϳ�������.dll�ļ���

�������������C���Ի�����HDLֱ�Ӳ�����Ҫ������ߵ�Ӧ�ö�����ѡȡ��ķ�ʽ���ڴ��������£���C���Ժ�HDL�������ɲ��������������Щ�� |