但是若严格控制套刻精度,32nm及以下节点技术的存储器件后道(BEOL)图形化时,可选用DTP工艺。虽然由于金属层的反射属性,可能会让使用非扫描式电子显微镜(SEM)测试套刻精度颇为困难,但利用SEM作为主要的套刻精度测试工具则颇让人鼓舞。本文描述一种新颖的套刻精度测试和校正方法,可以容忍DTP工艺的缺点并使ACPV对CDU的影响降至最小。

DTP工艺流程

这种简化的DTP工艺流程(图2)一开始形成十字线空白。将栅宽为128nm的空隙曝光,在晶圆上形成沟槽。通过硬质掩膜进行第一次刻蚀后,第二次曝光时偏移64nm形成另一套沟槽,在晶圆级别实现64nm的设计沟道。

使用DTP工艺时,线条的左右边缘在不同的曝光步骤形成(与DLP相反)。这就意味着双沟槽法的第二次曝光步骤出现的套刻精度误差在最终的线条和间距图形中形成CD误差。

DTP套刻精度测量

最终刻蚀后,可以在设备确定中使用CD-SEM测量DTP套刻精度(比如,在位于主器件栅格附近的存储器栅格或专用的CD-SEM套刻精度栅格标记内)(图3)。1这时套刻精度定义为:

最后一次刻蚀完成后,DTP的图形样式与DLP的图形样式几乎相等。利用我们的VeritySEM2工具,在ASML(荷兰Veldhoven)光刻机上完成测量,并将结果发表在SPIE20071,DLP工艺的CD-SEM测量表明了保持套刻精度测量(表)的可靠性,它符合国际半导体技术蓝图(ITRS)的要求。

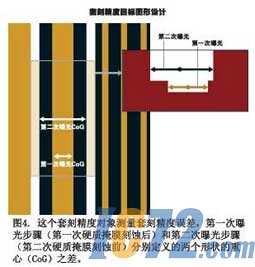

但是在第二次硬质掩膜刻蚀(图2c)后对套刻精度误差进行CD-SEM测量,会无法再次进行光刻。因此最好开发一种技术,在第二次硬质掩膜刻蚀前对套刻精度误差进行CD-SEM测量(图2b)。因此,为了利用CD-SEM精确并可重复测量DTP的套刻精度,我们设计了一种沟槽内沟槽对准SEM标记,可放置在裸片划片槽之间或横跨裸片的器件栅格附近。图3所示为该标记的横截面示意图。第一次硬质掩膜刻蚀期间,形成了窄沟,第二次光刻步骤形成宽沟。这样可以通过测量沟槽中心线条的偏差,计算套刻精度误差(两个沟槽的重心[CoG],图4)。

OLE=第二次曝光CoG-第一次曝光CoG

此处第二次曝光CoG是宽沟的中心,第一次曝光CoG是窄沟的中心。

为验证对套刻精度误差的测量,我们对沟槽的CoG测量结果与故意设计的套刻精度误差(由SEM蒙特卡罗模拟形成的沟槽2)进行了比较。设计值和实际测量值间获得了很高的校正因子(0.974)。此外,最近在利用CD-SEM的ASML上进行的CoG套刻精度测量证实了0.2nm的套刻精度测量的精确性,并符合2006ITRS的要求(对于1nm的套刻精度测量灵敏度,p/t=0.2)。

要完全利用这种沟槽内置沟槽的SEM标记设计,需要将第二次曝光的底部防反射薄层(BARC)材料的性质纳入特殊工艺考虑的范围。二次曝光后,第一次硬质掩膜沟槽中(“沟槽内置沟槽”套刻精度标记中)填满了BARC,SEM无法分辨沟槽(SEM信号动力学仅对表面状况敏感)。因此,应在第二次曝光后采用BARC去除技术。有一种从注入机工艺流程搬来的方法,即采用一种可以湿法显影的有机BARC(如BrewerScience的注入式BARC,IMBARC)3,这种BARC已进行了适当的成像和加工改进。显影剂可以在第二次曝光光刻胶显影期间去除第一个套刻精度标记硬质掩膜沟槽中的BARC,并可让SEM测量两个沟槽间的套刻精度误差。还须投入更多的研发精力来优化此技术。

DTP套刻精度校正

要进行套刻精度校正,CD-SEM套刻精度的结果必须反馈到某种自动工艺控制(APC)系统,如ASML公司的GridMapper。这种APC技术校正扫描仪和工艺残余误差(栅格扭曲),如平移、旋转和放大,以及放大和旋转不对称。正如DTP工艺所表明,由于涉及多个工艺步骤,这些误差变得很严重。通过在曝光区域对五个或五个以上位置进行取样,APC解决方案可以实现高阶扫描校正(图5)。

由于误差会影响CDU预算,场内DTP套刻精度残余误差可能导致器件生产合格率低下的严重后果。出现套刻精度漂移时,可以通过在第二次曝光步骤后计算套刻精度误差,提高产率。若发现及时,可重新进行第二次曝光,并针对下一次漂移进行校正。CD-SEM套刻精度测量法通过将套刻精度测量结果馈送到APC方案,可以成为校正栅格扭曲的一种可行方法。APC方案会动态校正误差,使ACPV最小,并使CDU最佳。