|

SDH设备时钟(SEC)是SDH光传输系统的重要组成部分,是SDH设备构建同步网的基础,也是同步数字体系(SDH)可靠工作的前提。SEC的核心部件由锁相环构成。网元通过锁相环跟踪同步定时基准,并通过锁相环的滤波特性对基准时钟在传输过程中产生的抖动和漂移进行过滤。而当基准源不可用时,则由SEC提供本地的定时基准信息,实现高质量的时钟输出。

SEC需要满足ITU-TG.813建议[1]中的相关指标要求。SEC可以工作在自由振荡、跟踪、保持三种模式下,并且能够在三种模式之间进行平滑切换。由于ITU-TG.813建议规定的SEC带宽较窄(-3db带宽在1~10Hz内),且需要在三种工作模式下输出稳定的时钟,同时还要保证在三种模式切换过程中输出时钟稳定(即平滑切换),采用模拟锁相环(APLL)很难实现。因此一般采用数字锁相环(DPLL)实现SEC[2];也有许多芯片厂商直接采用单片集成电路芯片实现SEC,如SEMTECH公司的ACS8520[3]等。

本文介绍一种采用单片现场可编程门阵列(FPGA)芯片实现SEC功能的方案,在此将用FPGA设计的SEC功能芯片命名为TSP8500。

1 TSP8500芯片内部结构及设计原理

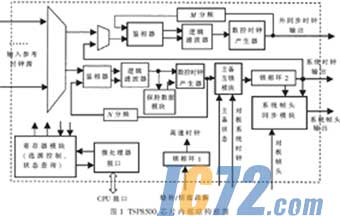

TSP8500芯片采用Altera公司的EP2C5T144-8FPGA实现。芯片的内部结构框图如图1所示。

TSP8500提供两类时钟输出接口:①给SDH网元系统中各功能模块提供38.88MHz系统时钟sysclkout和2kHz系统帧头信号sysfpout;②给其他网元设备提供2.048MHz的外同步输出基准时钟ext_clk_out。

该芯片需要外部输入一路19.44MHz的本地时钟,通过FPGA的内部PLL(锁相环1)倍频后得到311.04MHz高速时钟,作为芯片内部数字锁相环的工作时钟。当所有参考源丢失时,为保证SEC仍然能够输出高质量的时钟,本地时钟一般采用高稳定度的温补晶振(TCXO)或者恒温晶振(OCXO)提供。

该芯片还提供微处理器接口,用于各数字锁相环的参考源选择、工作模式的设置以及芯片内部工作状态的查询。

1.1系统时钟的设计实现

从图1可以看出,芯片输出的系统时钟sysclkout,主要由一路全数字锁相环(ADPLL)[4]、主备互锁模块(实际上也是一路ADPLL)和FPGA的内部PLL(锁相环2)共同完成。

该芯片可以从输入时钟中任选1路作为参考时钟进行跟踪。应用该芯片时,用户通过微处理器接口设置参考源的优先级表(Prioritytable)后,芯片便可根据参考源的质量等级自动选择最优的参考源进行锁相跟踪。

在TSP8500芯片中设计的ADPLL和其他类型的锁相环结构基本一致,主要由鉴相器、逻辑滤波器和数控时钟产生器三部分组成。SEC要求在保持模式下仍然能够输出高质量的时钟,所以在用于产生系统时钟的ADPLL中,增加了保持数据模块。

系统时钟工作在跟踪模式时,通过ADPLL环路实现输出系统时钟和参考时钟的同步。同时,将频率控制字数据保存在FPGA内部自带的RAM中(即图1中的保持数据模块)。当所有参考源丢失时,SEC进入保持工作模式,芯片将保持数据模块中保存的频率数据按先进后出的方式取出,对数控时钟产生器进行控制,保证了系统时钟在保持模式下仍然能够输出高质量的时钟。

系统时钟工作在自由振荡模式时,由高频时钟直接自由分频得到系统时钟。

根据ITU-TG.813建议要求,SEC带宽较窄(-3db带宽在1~10Hz内)。在逻辑滤波器模块,采用FPGA内部的数字逻辑实现二阶线性滤波器,满足了SEC噪声传递特性的要求。为了灵活应用,滤波器的环路带宽可以通过微处理器接口进行灵活调整。当参考源切换时,通过滤波器的平滑设计,保证了频率控制字缓慢变化,可靠地实现了参考源的平滑切换。

数控时钟产生器模块由高频时钟在频率控制字的作用下进行受控分频得到。为了减小数控时钟产生器输出时钟在受控分频过程中产生的数字相位噪声,TSP8500芯片设计时采用了独特的“微小相位调整技术”,使数控时钟产生器输出时钟的Cycle-Cycle抖动仅0.4ns。

SEC一般都采用主备备份设计。由于SEC本身的带宽较窄,俘获速度较慢,当主备SEC跟踪同一路参考源时,无法时刻保持主备SEC相位同步。设计中增加了主备互锁模块,保证了主备相位的快速同步。主备互锁模块也由ADPLL实现,但其环路带宽设计的较宽,俘获速度很快,足以保证主备相位准确同步。SEC工作在主模式时,主备互锁模块直接锁定本板的全数字锁相环ADPLL输出的时钟;而当SEC工作在备模式时,主备互锁模块锁定对板送来的系统时钟RDSYSCLK。

主备互锁模块输出的时钟,仍然有0.4ns的相位抖动。在这里通过FPGA自带的PLL(锁相环2)进行相位平滑。

主板的系统帧头直接由主板的38.88MHz时钟自由分频得到。而备板的系统帧头,则由本板的系统时钟在主板送来的同步帧头受控下分频产生。由于主备系统时钟的相位同步了,所以保证了系统帧头的相位同步。

1.2外同步时钟的设计实现

芯片输出的外同步时钟ext_clk_out由一路ADPLL实现。

外同步时钟可以从输入时钟或系统时钟中任选一路作为参考时钟进行跟踪;通过微处理器接口进行选源。

外同步时钟环路的滤波设计,也由FPGA内部的数字逻辑直接实现,但是环路带宽设计得比较宽。当进行参考源切换时,ADPLL会短暂地进入保持工作模式,保证了输出时钟的稳定。

由于外时钟频率为2.048MHz,不能由311.04MHz时钟整数分频得到,所以数控时钟产生器模块采用了小数受控分频设计。由于采用了小数分频,数控时钟产生器输出的外同步时钟的相位抖动为0.8ns。

鉴于FPGA的PLL资源限制,外同步时钟没有采用APLL进行滤抖,而是直接由数控时钟产生器输出。但是输出时钟的相位抖动也远远能够满足小于0.05UI的要求。

2输出时钟的性能指标测试

对TSP8500芯片输出的系统时钟和外同步时钟的各项指标进行了测试。下面主要给出时钟的抖动特性以及锁定模式下SEC的相位漂移特性和保持模式下SEC的相位漂移特性。

2.1输出时钟抖动特性

将高速示波器设置为“长余晖”模式,测试TSP8500输出的系统时钟sysclkout和外同步时钟ext_clkout的信号波形,得到输出时钟的P-P抖动特性。其中sysclkout时钟的P-P抖动小于100ps;ext_clkout时钟的P-P抖动小于2ns。

2.2 SEC的相位漂移特性

采用铷钟作为测试时钟基准源。基准时钟送TSP8500进行跟踪,同时送时间间隔分析仪。 测试方法如图2所示。

TSP8500的系统时钟sysclkout的参考源,通过CPU接口选定为时钟基准源送来的2.048MHz时钟。由于系统时钟sysclkout输出为38.88MHz,不便于用时间间隔分析仪进行测试,所以采用外同步时钟ext_clk_out接口输出2.048MHz时钟送时间间隔分析仪进行TIE曲线的测试;而ext_clk_out时钟的参考源,则通过CPU接口选择sysclkout时钟。

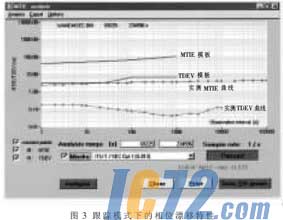

在跟踪模式下,图2中的开关K闭合,测试24小时后得到的MTIE/TDEV曲线,如图3所示。

从图3的测试结论来看,TSP8500跟踪模式下的相位漂移特性满足ITU-TG.813建议要求。

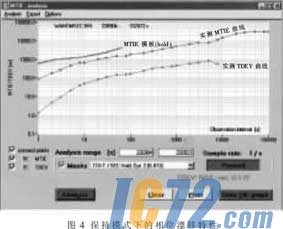

跟踪24小时后,将图2的开关K断开,TSP8500的系统时钟自动进入保持工作模式,继续用时间间隔分析仪表测试24小时,得到保持模式下的MTIE/TDEV曲线,如图4所示。

从图4的测试结论来看,TSP8500芯片在保持模式下的相位漂移特性也满足ITU-TG.813建议要求。

采用单片FPGA实现的SEC芯片TSP8500,输出时钟满足其在SDH设备中应用的要求,各项时钟性能指标完全满足ITU-TG.813的相关建议要求。TSP8500芯片已在国内某著名通讯设备厂商开发的SDH设备中得到应用。

另外,TSP8500芯片所采用的FPGA,其成本低于10$,远低于商用SEC芯片的价格,且功能可靠,具有相当高的性价比,有望得到更大规模的商用。 |