1 引言

ARM作为一种16/32位高性能、低成本、低功耗的嵌入式RISC微处理器。普遍应用于工业控制、消费类电子产品、通信系统、无线系统等产品。大多数ARM微控制器都集成了DMA控制器。

且直接内存存取(DMA)作为一种独立于CPU的后台批量数据传输技术,以其快速、高效的特点在数据采集领域得到了广泛的应用。本文以三星公司的S3C2410为例,介绍了其内部DMA控制器的特点和使用方法.以S3C2410和FPGA为核心结合DMA技术设计了CCD相机采集系统,并且给出Linux操作系统下DMA设备驱动程序的设计方法。

2 DMA工作过程简介

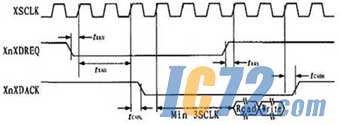

S3C2410是基于ARM920T内核的RISC微处理器.主频可达203 MHz,适用于信息家电、手持设备、移动终端等领域。S3C2410可提供4个DMA通道.用于系统总线内部或与外围总线之间的数据交换。现以外部DMA 请求为例简要介绍DMA的工作过程。图1所示为DMA基本工作时序。

图1 DMA基本工作时序图

当需要进行DMA操作时,外部DMA请求引脚XnXDREQ置为低电平。此时DMA控制器向CPU发出占用总线的请求,当总线请求成功后,XnXDACK引脚变为低电平,表示CPU已经将总线使用权交给DMA控制器,可以进行数据传输。当数据传输完成后应答信号XnXDACK置为高电平,通知CPU完成一次DMA操作。

S3C2410提供了3种不同的DMA操作模式,分别是单服务命令模式、单服务握手模式和全服务握手模式。在利用DMA进行数据传输前必须对其相关寄存器进行设置。主要有:源地址寄存器、目的地址寄存器和各自的控制寄存器,以及配置DMA模式的控制寄存器等。

3 采集系统硬件设计

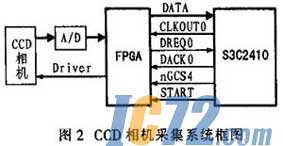

根据DMA的特点,设计了基于ARM和FPGA的CCD相机采集系统。

系统结构如图2

FPGA选用Altera公司的Cyclone系列器件EP1C6T144C8,可为CCD相机提供工作所需的驱动时序.同时接收经模数转换的 CCD输出图像数据。S3C2410通过DMA方式从FPGA内部采集数据,通过数据线、DMA信号线、片选信号和输出时钟线与FPGA相连。

这里主要介绍DMA方式的数据采集,FPGA内部的CCD驱动逻辑暂不介绍。

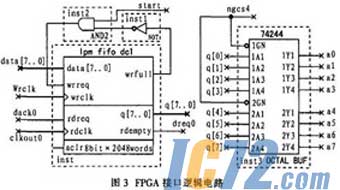

FPGA与ARM的接口逻辑电路如图3。

FPGA内部采用异步FIFO解决CCD输出数据频率和S3C2410采集频率不匹配的问题,写时钟由CCD输出位同步信号提供,读时钟由 S3C2410的时钟输出引脚CLKOUT0提供。CLKOUT0根据ARM内部寄存器的设置可以输出不同的时钟频率。FIFO输出数据经过以nGCS4 为选通信号的BUFFER后接到ARM的数据总线上。nGCS4是S3C2410存储空间中BNAK4的片选信号,当S3C2410对地址范围 0x20000000~0x28000000的存储空间进行读写操作时,BANK4为低电平,其余时间均为高电平.用它作为BUFFER的选通信号能有效地避免数据总线的污染。

FIFO的写请求信号由S3C2410与FIFO的满状态共同控制。当ARM发出START信号并且FIFO未满时,写请求信号为高电平。FIFO在写时钟的控制下写入数据。当START信号撤销或者FIFO满时,写请求信号变为低电平,停止写操作。

FIFO的读操作与ARM的DMA操作配合进行。系统采用单服务命令模式的DMA操作,每次传输一个字节数据位。当DREQ0信号变为低电平时 DMA操作开始,每次传输一个字节后产生一个DACK0应答信号,而且只要DREQ0为低电平DMA操作就继续进行,直到DMA控制寄存器中的计数器为 0.产生DMA中断。根据上述时序特点,将FIFO的空信号作为DMA的请求信号DREQ0.当CCD输出的数据写入FIFO中时,空信号跳变为低电平启动DMA操作,同时以DACK0信号作为FIFO的读请求。每一次DMA传输完成后应答信号使FIFO的读指针移动一位,以实现数据的快速准确采集。

4 Linux下的驱动程序设计

系统采用ARM+嵌入式Linux的构架,Linux版本为2.4.18,采集系统必须和高效灵活的接口驱动程序相结合才能在操作系统下正常工作。

4.1 驱动程序的基本概念

设备驱动程序是操作系统内核和硬件之间的接口,它属于内核一部分,主要功能如下:

(1)对设备初始化或释放;

(2)把数据从内核传送至硬件。从硬件读取数据:

(3)读取应用程序传送给设备的数据,回送应用程序请求的数据:

(4)监测和处理设备出现的异常。

设备驱动程序为应用程序屏蔽了硬件的细节,在应用程序中,硬件设备只是一个设备文件,可以像操作普通文件一样对硬件设备进行操作。

4.2 修改代码

嵌入式Linux在arch/arm/mach-s3c2410目录下的DMA.c 文件中定义了一些与DMA操作相关的通用函数,主要有:申请DMA通道函数s3c2410_re,quest_dma()、申请DMA中断函数 request_irq()、加入DMA队列函数s3c2410_dma_queue_buffer()、进行DMA操作函数process_dma() 以及中断处理程序dma_irq_handler()等。在进行特定接口操作时,必须对其进行适当的修改。根据接口设置修改如下内容:

增加外部DMA操作的寄存器设置:

#define XDREQ0_CTL(DEMAND_MODE | SYNC_HCLK | INT_MODE | TSZ_UNIT | SINGLE_SERVICE | HWSRC(CH0_nXDREQ0) | DMA_SRC_HW | CLR_ATRELOAD | DSZ(DSZ_BYTE)| TX_CNT(0));

//设置DMA为单服务命令模式,8位数据总线、允许中断且通过DREQ0硬件触发DMA操作

#define XDREQ0_RD_SRC 0x22000000

#define XDREQ0_RD_SRC_CTL BUF_ON_MEM_FIX

//设置DMA操作的源地址为系统总线上的0x22000000且地址固定

#define XDREQO_RD_DST_CTL BUF_ON_MEM

//设置DMA操作的目的地址在系统总线且地址逐次加1

通过DMA读取FPGA数据时必须由操作系统在内存中开辟一个空间做为DMA操作的目的地址。操作系统开辟的内存位于虚拟空间.而DMA操作的目的地址必须为物理地址,所以必须进行虚拟地址到物理地址的转换。因此在process_dma()中增加如下代码设置DMA的目的地址寄存器:

regs->DIDST=virt_to_bus(buf->dma_start)

virt_to_bus()是操作系统提供的虚拟地址到物理地址的转换函数,buf->dma_start是系统开辟的虚拟地址空间的首地址。

另外由接口原理图可知,S3C2410须向FPGA发送START信号启动FIFO的读写和DMA操作。所以系统定义GPB3作为START信号,定义如下:

#define START(GPIO_MODE_OUT | GPIO_PULLUP_DIS | GPIO_B3);

同时在process_dma()函数中增加如下代码启动DMA操作:

write_gpio_bit(START,1);

START引脚置为高电平后立即启动FIFO的写操作,同时也就启动了DMA操作进行数据传输,当DMA计数器减为0后发生DMA中断,并且在中断处理程序中将START位置0停止FIFO的写操作。

4.3 接口驱动的关键代码

利用系统提供的DMA操作函数,接口驱动的设计就显得比较容易。接口驱动属于字符设备驱动.重点在初始化和read函数部分。

初始化函数中完成DMA引脚定义、BANK4总线设置、申请DMA通道以及注册字符设备等。read函数是接口驱动的核心。应用程序正是通过调用read函数来读取数据。其核心代码如下:

fpga_buf_t *b=&fpga_buf;

dma_addr_t *buf;

b->size=count;

buf=kmalloc(b->size,GFP_DMA);

s3c2410 dma_queue_buffer(b->dma_ch,(void*)b,buf,b->size,DMA_BUF_RD);

if(copy_to_user(buff,buf,b->size))

return -EFAULT;

kfree(buf);

return b->size;

系统调用read函数时首先通过kmalloc分配一段虚拟内存空间,并将其指针和DMA通道、传输字节数一起通过 s3c2410_dma_queue_buffer()加入DMA队列.在队列函数中调用process_dma()函数将虚拟地址转换为物理地址并且启动DMA操作。DMA操作完成后退出队列并调用copy_to_user()将采集到的数据由内核空间拷贝到用户空间进行后续操作。 |