Stream Processors公司(SPI)是一家在美国麻省理工学院和斯坦福大学研究成果基础上建立起来的无晶圆厂IC公司。这家公司近期通过发布两款与众不同的DSP,在业界进行了高调亮相。SPI称,这两款器件采用了具有原创性的新架构,并将流处理首次商用在DSP中。

从2006年末开始,SPI已经开始推出其Storm-1产品系列。这家初创公司的管理层透露,它们已与一位客户合作近一年时间了。这些器件锁定的是诸如视频和图像处理等高性能信号处理应用。SPI介绍说,它们分别是每秒可进行80亿次运算的8通道SP8-G80和每秒可进行160亿次运算的16通道SP16-G160。据称,这些器件比传统DSP在性价比上有10倍以上的提升。

SPI将流处理描述为一种编程模式,以及一种处理器架构,这种架构设计用于带编译器管理分级的并行处理应用。该架构通过在核心功能中采用数据并行来取得高性能。据SPI介绍,该架构最适合关涉数据并行性并体现数据位置的计算密集型应用。这些应用包括:音视频编解码器、分析、图像和图形处理。

SPI的软件工程副总裁Tim Southgate表示,这种可编程处理器还可被用于其它应用。SPI的业务拓展副总裁Bengt Christensson介绍,SPI的路线图昭示出它将致力于更高性能的应用以及增加用于消费领域的新产品。

SPI的高层介绍,其架构不包括在传统DSP上占用大部分空间的硬件缓存。的确,SPI的器件依靠线寄存器文件为其多个线存储I/O流。保持数据定位可使该架构得到最好的效率和最高的带宽,Southgate介绍。

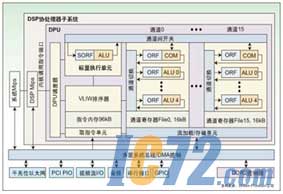

图:16通道SP16-G160提供单流执行及比分割多核方法更简单的设计

独立分析公司Berkeley Design Technology的总裁Jeff Bier很推崇这一迅速向高度并行架构转变的趋势。Bier表示,主要是基于这样一个共识:在保持合理的成本和功耗下,更高的并行程度是得到更好性能的最佳方法。

实现更高的并行性有各种途径,Bier说。SPI着眼于数据层面的并行,而其它公司更专注任务级的并行。“结果是,SPI可为程序设计师提供简单得多的编程模型,而专注于任务级并行的公司就做不到这点,”Bier声称。SPI器件的一个关键特性是ANSI C编程环境。SPI提供一种功能调试器库、一个目标模拟器和Storm SP16开发组件。

其它多核方法是在不同处理器上运行不同任务,从而使编程变得复杂。SPI的方法是一次运行一个任务,但借助多层次的并行以加速关键任务的执行速度,Bier介绍。对SPI的挑战在于它要显示出其目标应用与SPI的方法“相得益彰”并可有效利用可用的处理资源,他说。

Bier说,SPI的利好消息是,该公司一直追逐的视频和图象处理应用具备大量的数据并行性。“诸如对将视频帧从一种分辨率调整为另一种分辨率的某些应用,SPI的方法非常适合,”他说。“但即使在视频应用内,也有其它一些你并不十分清楚该如何应用该架构的任务。”

SP8-G80和SP16-G160在1万片时的单价分别为59和99美元。它们都工作在500MHz并包括32、64或128位的DDR2 DRAM。这两款器件由台积电(TSMC)采用130nm工艺制造。SPI计划采用65nm技术制造其第二代器件,Christensson表示。 |