65nm及以下节点的可制造性设计(DFM)问题正变得越来越关键,其原因在于,随着芯片关键结构尺度的不断缩微,相同的绝对物理变异可能导致相对较大的电气变异。在65nm及以下节点,光刻效应成为制造性变异的最大因素。37页表示的是芯片中心的一个门。由GDSII表述的该逻辑门的几何形状轮廓显示在左边(红轮廓线代表硅片中的扩散区,而四个绿色矩形反映的是伴随单个晶体管的多晶硅栅极区)。右上角的黄箭头指示了其中一个晶体管的沟道宽度和长度(沟道实际上是被栅极覆盖的一个硅片区域)。

问题是硅芯片特征(结构)尺寸现在小于用来生成这些特征的光的波长。若一个特征根据光刻图像被原样复制在光掩膜上,那么随着新技术节点的缩微其特征尺寸将越来越小,从而导致出现在硅片上的图形形状与理想形状的差异越来越大。

目前用传统设计流程解决该问题的方法是用诸如光学接近修正(OPC)及相移掩膜(PSM)等各种分辨率增强技术(RET)对GDSII文件进行后处理。例如,物理设计工具通过强化现有特征或增加新特征(被称为次分辨率辅助特性――SRAF)的手段修改GDSII文件以获得更好的可印刷能力。它意味着,若工具预计印刷过程会产生某种失真,则工具将自动增加反方向失真,以使两个失真相互抵消。问题在于,设计中的每个结构都受临近结构的影响。也即,若GDSII文件生成了两个几何形状并在光掩膜时相互隔绝,则这两个形状将以确定方式被打印。但若使同样这两个形状相互靠得很近,则这两个形状间的相互干扰通常会以非直观的方式擅自改变这两个形状。这些干扰的结果将导致时序、噪声和功耗变异并最终影响良率。

图1:真正的可制造性设计需要适应绝对物理变异。

制造和良率问题可大致归为四类:灾难性、参数型、系统类(特性决定)和统计类(随机)。灾难性问题是那些使芯片彻底报废的问题,如过孔丢失。发生参数型问题的芯片其功能仍完好,但指标达不到标称要求,如:一款500MHz器件现只可运行在300MHz,或设计功耗本来是5W,但实际上达到8W。灾难性和参数型问题的出处都又可进一步分为:系统效应和统计事件。

真正具有DFM意识的方案必须要能应对全部这些问题,也就是说,它意味着在实现、分析、优化和验证等过程中要能对全部系统和统计效应建模。

实现可接受性能和良率的途径是使包括单元表征、IC实现、分析、优化和签字确认在内的整个设计流程的各个环节都兼顾DFM要求。在这样一个流程中,可在最恰当同时最有效的时机理解并解决制造性问题,并在设计和制造这两个环节间建立起更紧密联系,这样,设计意图就能正确传送给下游制造,而生产数据又反馈给上游设计。

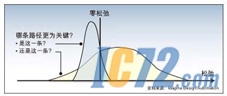

图2:当被应用于两个时序PDF曲线时,SSTA必须能解读灵敏度和临界态。

设计工具(特别是实现、分析和优化引擎)一直是基于规则考虑的。也就是说,将一套规则提供给这些工具,这些工具根据规则对设计进行分析和修改以确保不违背规则。但在当今的超深亚微米技术中,这些规则不再能反映制造工艺的基础物理特性。即使设计工具尽职尽责地遵循代工厂提交的全部这些规则,得到的芯片仍可能存在参数型(甚至灾难性)问题。

为解决这些问题,工具现需要采用基于模型的技术。这意味着工具要按照芯片实际被制造的样子建模。例如在光刻模拟中,工具需要建模光通过光掩膜及任一透镜的方式、光与硅片表面上化学物的反应方式以及如何生成最终结构等。

一个真正具有DFM意识的设计环境需从具有DFM意识的表征开始。它涉及将与标准单元库相关的全部文件以及PDK(工艺设计包)和DFM数据以及代工厂提供的模型通盘考虑,然后在时序、功耗、噪声和良率整个背景下,针对工艺变异和光刻效应生成统计概率密度函数(PDF)。作为这一流程的一部分,还能自动提取和/或生成各种技术规则供下游工具使用。

真正具有DFM意识的表征环境还能为各个单元提供良率评分,在评分过程中,它将化学机械抛光(CMP)效应考虑在内,并利用诸如关键区域分析(CAA)等技术解读随机微粒缺陷。此举允许模型表征过程同时提供灵敏度和鲁棒性指标,随后供实现、分析和优化等引擎使用。例如,通过了解每个单元的延时或漏电灵敏度等参数,实现工具可以通过规避这些单元来优化关键时序路径,或通过修改其位置将这种灵敏度降至最低。

传统综合引擎根据库内不同单元的时序、区域和功率特征以及设计师提交的设计约束来执行选择和优化。在具有DFM意识的环境,综合引擎会将每个单元的噪声和良率特征以及构成库的单元的变异特征(工艺和光刻)加之这些特征是如何影响每个单元的时序、功耗、噪声和良率等诸多因素全部考虑在内。

就该流程的物理设计部分而言,如我们前面指出的那样,设计中的每个结构受其周边环境的影响,具体表现在那些临近结构以非直观方式造成的干扰。这就要求布局工具能感知光刻并留意下游制造RET工具的限制和要求。

同样,在布线引擎中嵌入光刻仿真能让它识别必须规避的图案,并确定为了避免生成下游RET工具无法修复的光刻“热点”而必须修改的版图位置。光刻感知布局和布线功能的结合有助于把对后布局RET的需求减至最小,并提高所需任何RET的效率。

真正具有DFM意识的设计环境还必须支持对时序、功耗、噪声和良率结果的分析和优化。先看时序,形成芯片中路径的每个部分,诸如线段、过孔和单元(逻辑门)等,都存在与之相关的时延问题。这些延时是工艺、电压和温度(PVT)的函数。传统的设计环境一直基于诸如静态时序分析(STA)那样的最坏情况分析引擎。STA为不同路径设定最坏情况延时。例如,STA假定:形成特定路径的全部延时不是最长就是最短,当然这种假设既不实际又很悲观。为解决这些问题,具有DFM意识的设计环境必须采用基于统计的方法,并使用比如统计静态时序分析器(SSTA)。

真正具有DFM意识的设计环境的一个关键因素是若没有相应的DFM意识优化能力,则DFM意识分析的用处将被大打折扣。例如,为执行对变异敏感的时序优化,具有DFM意识的SSTA引擎必须要能解读灵敏度和临界态。

在传统STA中,越是关键路径对电路延时的影响就越大,即具有最大负延时的路径最关键。而在具有DFM意识的SSTA中,最关键路径是最有可能对电路延时影响最大的路径。基于此,具有DFM意识的SSTA优化必须基于诸如临界态参数(用于确定关键路径,即最有可能成为限制性因素的路径)这样的函数。

除时序分析和优化外,所有其他分析和优化引擎(泄漏功耗、噪声和良率)也必须采用具有变异意识的统计来有效解读变异。利用这些技术才可能使设计更具鲁棒性,并对变异不那么敏感,进而在器件的整个生命周期内最大化良率。

最后,环境必须提供具有DFM意识的签核验证。在该阶段,经DFM优化后的设计被送至一组验证引擎进行诸如设计规则校验(DRC)和光刻工艺校验(LPC)等检查。需要重申的是,所有这些引擎必须在时序、功耗、噪声和良率指标背景下,针对工艺变异和光刻效应对设计进行分析和检验。因许多制造性问题难于用必须遵守的规则来表述,所以物理验证环境必须要适应基于模型的解决方案。另外,由于需要处理大量设计数据,所以验证方案必须高效且可扩展。

真正的DFM设计流程的一个关键要求是采用统一的数据模型且所有实现、分析和优化引擎能准确地对同一数据实施立即和共时访问。进一步解释就是说:在布线器放置一条线段的同时,还进行RC寄生效应的提取,进行延时、功耗、噪声和良率的计算以及对该线段信号完整性的评估,且仍在此时此刻,布线器利用这些数据自动进行我们感觉不到的任何必要修改。

通过在实现流程中集成DFM,可以消除采用独立点工具方法可能导致的潜在性设计反复。任何设计决策和权衡取舍都是在整个设计背景下完成的。因此,诸如减小面积以及降低动态和静态功耗等任何内核改进成果都能立即加以利用,而设计师可确保潜在的DFM结果不会干扰或削弱这种好处。在设计完成后和出带前,可以利用DRC/LVS/光刻引擎进行自动的具有DFM意识的签核验证。

真正具有DFM意识的设计环境可以在整个流程的各个阶段、在时序、功耗、噪声和良率背景下解读工艺变异和光刻效应。它从对单元库的表征开始,贯穿实现、分析和优化过程,直至签核验证结束。 |