1 引 言

随着计算机技术、通信技术的飞速发展,互联网的迅速普及,嵌入式技术已成为新世纪最有生命力的技术之一,其得到了飞速的发展和广泛应用。随着复杂控制、汽车电子、医疗仪器、数字通信、网络应用等复杂要求的出现,常用的单片机系统和DSP系统等这类简单的嵌入式系统已经无法满足要求。在面对日益复杂和高性能应用时,大多采用主机(由微控制器或微处理器充当)+DSP的方式构成主从式系统,这样既可以利用DSP强大的数字信号处理能力进行复杂的运算,又可以利用微处理器丰富的片内外设和接口对整个系统的运行进行控制。

在这种系统中,主机与DSP的数据交换就成为系统设计中必须考虑的重要问题。传统的单片机与主机交换数据大多采用串行通信方式或共享存储器方式。串行通信方式只适用于通信量较小的系统。共享存储器方式,需外扩一双端口RAM及触发器锁存器等芯片,使得系统的硬件结构复杂。

ADI公司生产的DSP芯片ADSP2191配置了主机接口(Host Port Interface,HPI),可以实现与主机之间并行高速的数据传输。HPI可以很容易地与各种主机互联,甚至不需要外加接口逻辑,可以大大简化系统的硬件结构。且DSP依靠自身的硬件来协调冲突,在主机访问HPI的时候,不会打断DSP正常的程序运行。

2 ADSP2191M主机接口简介

主机接口HPI(Host Port Interface)是Analog DeviceInc.公司在新一代高性能DSP芯片上配置的与外部主设备或主处理器进行高速数据交换的并行接口。HPI是地址和数据总线复用的8位/16位并行口,只能做从机,外部主机(微控制器、FGPA或者另一片DSP)是HPI的控制者。通过HPI,主机可以访问DSP的内部存储空间、引导空间和I/O空间;另外,还可以通过HPI口把程序加载到DSP。ADSP-2191有24个引脚专门用于HPI,如表1所示。

HPI地址总线的低16位是与数据总线复用。数据总线默认情况下是8位,使用HAD[7:0]八个引脚。在复位后,DSP本身或外部主机(通过主机接口)可以配置HPI为16位口。

3 硬件设计

MPC555微控制器是Motorola公司PowerPC 500系列的代表产品,是一款高速高性能的32位浮点处理器,其工作时钟可达40 MHz。其内部资源极其丰富,有26 kBRAM和6 kB TPURAM,448 kB FLASH、多通道串行模块、CAN 2.0B控制器等,特别适于做复杂的实时控制和处理。MPC555与ADSP2191的接口电路如图1所示。

HPI提供2种硬件寻址模式:地址周期控制模式(ACCM)和地址锁存模式(ALEM)。其中,ALEM适用于与地址总线和数据总线复用的微处理器接口;ACCM模式适用于与地址总线和数据总线分开的微处理器接口。硬件寻址方式是由上电复位时HALE引脚的逻辑电平决定。如果上电复位时用外部下拉电阻把HALE拉低,就是ALEM方式;反之,如果用外部上拉电阻把HALE拉高就是ACCM方式。

HPI总线是一种异步通信协议,硬件握手可以是ACK方式,还可以是Ready方式,2种方式的有效极性都可以在上电复位时配置。另外,读/写选通信号的极性也可以在上电复位时配置。如果在上电时,读/写信号为高电平,那么读/写选通信号就是低有效。

综合考虑MPC555的外部总线时序和HPI接口的时序要求,在本设计中硬件寻址采用ACCM方式,应答方式采用ACK方式。读信号HRD、写信号HWR和应答信号HACK都是低电平有效。

要控制主机与DSP的数据交互,即主机要知道何时能从DSP读取数据,而何时又该写数据,还需要一个联络信号。本设计选用ADSP2191的1个I/O口PF0作为对主机的中断信号。

4 HPI的读写操作和接口软件设计

4.1 HPI接口的配置

要通过HPI访问DSP的内部存储空间和I/O空间,必须先配置HPI的寄存器。HPI接口有15个寄存器,其中9个是专门用于DMA方式的,对于直接访问方式,只有主机接口配置寄存器(HPCR)和主机接口直接访问页寄存器(HPPR)是必须配置的。外部主机或者DSP自己可以通过配置这2个寄存器,设置主机接口的访问参数,包括外部总线宽度、要访问的存储空间的页地址和数据类型等。下面是DSP自己配置主机接口的程序代码:

4.2 主机对HPI接口的读写操作

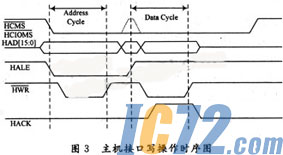

在ACCM方式下,HALE引脚上的逻辑0电平会触发HWR引脚产生一个下降沿跳变以便把地址锁存到HPI。时序图如图2,图3所示:

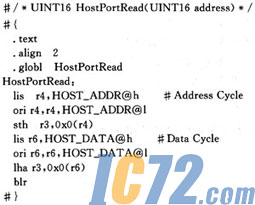

所以,主机对HPI的访问包含地址周期和数据周期2个周期。MPC555访问HPI的子程序汇编代码如下:

读操作:

写操作:

5 结语

目前,该方案已经成功运用于母线保护设备中,经测试在DSP接近满负荷工作时,数据传输速率也能达到2 MB/s,完全能满足系统需要。实践证明,HPI接口是一种电路简单、性能稳定、高效可靠的通信方式,而且具有很强的通用性,可广泛应用于各种含有HPI接口的多CPU嵌入式系统。 |