2控制回路的设计

传统的开关电源普遍采用电压型脉宽调制(PWM)技术,而近年来,电流型PWM技术得到了飞速发展,本设计采用电流型控制器UC1843来实现控制回路。UC1843工作频率可达500 kHz,并它具有大电流推拉式输出,低启动工作电流等特点。电路中在开关管通断瞬间,必须供给栅极较大电流,并对栅源极间电容进行快速充放电,以使开关管高速工作。UC1843的输出级为图腾柱式,输出电流为1 A。它不必增加任何外围电路,就可将其直接接到开关管的栅极,并驱动VMOS管高速工作。UC1843具有精度高、电压稳定、外围电路简单优点。相比电压型PWM,电流型PWM具有更好的电压调整率和负载调整率,系统的稳定性和动态特性也有明显的改善。

3双路输出设计

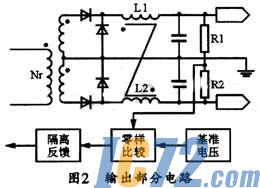

本设计中的双路输出部分电路如图2所示。

由于该电路要求对称输出,故将正负两路输出滤波电感L1、L2绕制在同一磁芯上,并采用双线并绕的方法来保证L1、L2电感量完全相同。线路在接人方法上采用了差模相位关系,这种连接方法可使2路输出电流的变化量相互感应,从而在一定程度上改善2路输出的调整率。

其次,也可将采样比较器R1、R2直接跨接到正负电源的输出端上。本设计的逻辑"地"不是电源的输出地.而是以负电压输出端作为采样比较和基准电压的逻辑"地"电位。这样,采样误差将同时反映出正、负2路输出的电压精度变化,并对正、负2路同样存在有反馈作用,以在很大程度上改进2路输出的调整率。

4变压器设计

开关电源的设计主要分为两部分,一是电路部分的设计。二是磁路部分的设计。开关电源变压器是高频开关电源的核心元件,必须进行合理设计才能达到理想效果。一般情况下,开关电源变压器的选用原则如下:

(1)要有较高的饱和磁通密度BS和较低的剩余磁通密度Br,以减少变压器的匝数和铜损。

(2)在高频率下应有较低的功率损耗;因为变压器高频工作时会发热而造成磁心损耗,从而影响电源输出效率,造成波形畸变等不良后果。

(3)适中的磁导率;不同的相对磁导率适合于不同的工作频率,比如相对磁导率为2000的材料,其适用频率在300 kHz~500 kHz。

(4)较高的居里温度;居里温度是使磁性材料失去磁特性时的温度。居里温度值过低,高温工作时会使磁心的饱和磁通密度严重跌落,从而影响正常工作。

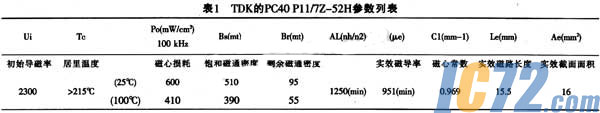

为此,本电路根据工作频率、输出功率、模块体积等要求,选用磁心规格为PC40-P11/7Z-52H的TDK磁性材料。其参数见表1所列。

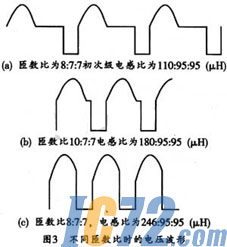

实际绕制变压器时,先根据计算所得的变压器匝数比,以绕满罐为原则来绕制变压器,再在电路中根据输出效率要求和工作电压范围,来观察开关管漏极上的电压波形,并对变压器匝数进行适当调整。事实上,当电源初次级匝数比增大时,电源效率会提高,但电源正常工作最小输入电压也会升高,电路的工作范围变窄;而当电源初次级匝数比减小时,电源正常工作最小输入电压降低,电路的工作范围变宽,但效率会降低。图3给出了不同匝数比时漏极上的电压波形:

其中图3(a)是变压器初次级匝数比为8:7:7,初次级电感量比为110:95,:95的波形,此时的电路输出效率为75%,最小输入电压为14 V;

图3(b)是变压器匝数比为10:7:7,初次级电感量比为180μ:95μ:95μ时的电压波形,此时的电路输出效率为78%,最小输入电压为16 V

图3(c)是变压器匝数比为13:7:7,初次级电感量比为246μ:95μ:95μ时的电压波形,此时的电路输出效率为81%,最小输入电压为20 V

由此可见,匝数比增高,效率逐渐提高,但低端电压逐渐上升,工作范围变窄。本设计最后确定的初次级匝数比11:7:7。电感量为200:95:95,效率为80%。

5磁复位设计

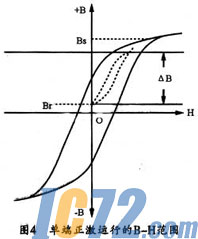

本电路中变压器的工作方式为单端正激式,变压器磁心工作在磁滞回线的第一象限,如图4所示,为了确保变压器在磁化曲线的线性区工作,设计时应在开关功率管截止期间将高频变压器复位,并使增长的磁通和减小的磁通平衡,以防止变压器磁芯饱利。

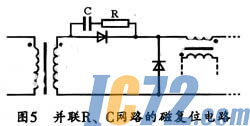

本电路在次级整流管两端并联了一个如图5所示的RC网络,以实现磁复位。该电路相比二极管加去磁绕组复位电路,其结构比较简单。这样,当开关关断时,磁感应电流便可通过变压器的次级绕组流出,并通过电容C使磁感应电流减至零。R,C取值时,C的电容量要足够小,以便在最短的关断时间内将磁感应电流衰减到零。而电阻R的电阻值则不能过小,电阻值过小会与内部寄生电感形成自激振荡。磁复位时,要求在输入电压为最小值或最大值时,磁复位电路都能对高频变压器进行准确地复位。

6输出纹波电压的降低

为达到降低输出纹波电压的目的,设计时,首先要减小功率开关管的电压尖峰。因为当VMOS管由导通变成截止时,在变压器的一次绕组上就会产生尖峰电压和感应电压,其中尖峰电压是由高频变压器漏感(即漏磁产生的自感)引起的,它与直流高压和感应电压叠加后很容易损坏VMOS管,故在设计时,要优化功率变压器的设计,减小变压器初级漏感;第二,电路布线时要尽量减少VMOS各端点的连接线长度,特别是栅极引线,如果无法使引线缩短,可以靠近栅极处串联一个小电阻,或者在漏级与地之间接上电容以减小振荡,减低尖峰电压;第三,应采用合适的RC吸收网络,以减小功率开关管的电压尖峰;此外,整流二极管在关断时的反向恢复时间也会导致尖峰电流,从而造成纹波,因此,设计时要优选反向恢复时间短的肖特基二极管来减小尖峰;最后,LC滤波电路要合理确定电感器的电感,应选用高可靠、温度性能好的高频独石电容为滤波电容,以减小纹波电压。

7结束语

本文介绍的双路输出正激式DC/DC变换器采用厚膜混合集成电路技术,裸芯片组装,金属全密封封装,同时采用平行封焊工艺来保证产品的高可靠性,表2所列是其电路性能参数由表2可见,该产品输出电压稳定,产品一致性好,同时具有体积小、重量轻、可靠性高、耐冲击、组装方便等优点,完全满足使用要求,可以应用于航空、航天、船舶等多项领域,以便为我国国防武器现代化提供保障。