摘要:介绍了Flash存储器的特性和应用场合,在16位地址总线中扩展大容量存储的一般方法。讨论了MCS-51系列单片机与Flash存储器的硬件接口方式和软件编程过程,以及在应用中应该注意的问题,并以W29C040为例,给出了实际原理图和有关实现。

关键词:Flash存储器;单片机;MCS-51;系统扩展

1 Flash存储器的特性和应用场合

Flash存储器是在EPROM和EEPROM的制造技术基础上发展起来的一种可擦除、非易失性存储元件。1983年Intel公司提出EPROM隧道氧化层ETOX(EPROM Tunnel Oxide)原理,1988年推出了可快速擦写的非易失性存储器Flash Memory,随后Toshiba公司又推出基于Fowler Nordheim的冷电子擦除原理和EEPROM的NAND体系结构的Flash Memory。

根据采用的工艺不同,Flash Memory至少有以下5种常用的体系结构:最初的2种占主流的是Intel的“或非”(NOR)型和Toshiba的“与非”(NAND)型,后来Hitachi和Mitsubishi在NOR型的基础上吸收NAND型的优点分别开发出“与”(AND)型和采用划分位线技术的DiNOR(Dividedbit-lineNOR)型,另外美国Sundisk则采用一种独特的Triple-Poly结构来提高存储器的密度。

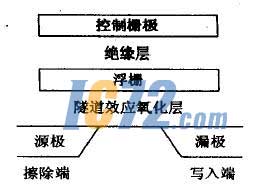

目前商品化的Flash存储器大多是用1μm的CMOS工艺制成的,其基本存储单元和EPROM一样,是一种浮栅器件,图1为一个存储单元的示意图。在浮栅和硅衬底之间有一层薄薄的氧化物质,当在控制栅极和漏极上加上高电压,源极接地时,沟道中电子由源极流向漏极。部分电子会在漏极附近被加速成为“热电子”,他们在控制栅极高电位的吸引下穿过氧化物质绝缘层,附着在浮栅上,使浮栅带电而引起阀值电压升高,使该元件处于高阀值电压状态。浮栅上电荷的保护期与EPROM器件相同,可超过100年。擦除浮栅上存储电荷使该元件返回到低阀值电压状态的方法则与EEPROM相似,只要将控制栅极接地,在源极上加上高电压,浮栅上的电荷便会穿过氧化物薄层流向源极。由于一块集成块上所有单元的源极内部是连在一起的,因此Flash存储器只能是整片擦除,这一点又与紫外线擦除的E2PROM相同。一些较新的Flash存储器,把整个芯片的存储单元划分为若干个扇区(或称为块、页),芯片既可以整片擦除,也可以对指定扇区擦除。

图1 一个存储单元的示意图

在单片机的早期应用中,对于一些可以改变、但是不会频繁修改的参数,一般只是用硬件开关来实现;引入EEPROM后,可以将少量的参数、关键数据用软件方式长期存储起来,但是要保存大量的数据仍是难以满足。在单片机系统中使用Flash存储器,可以有效地将单片机系统的灵活性和大容量存储结合起来,用简单的设计完成复杂的任务。本文以流行的MCS-51系列单片机和Winbond公司的W29C040为例,介绍接口方法和编程应用。

2 在MCS-51系统中的硬件接口方法

W29C040有512K×8位存储容量,按页组织,每操作。写入速度快且功耗低(工作电流为25mA,闲置电流为μA级),写入一页数据的时间为5ms,写入一个字节的典型时间周期为19.2μs;读取时间根据具体型号分别为70/90/120ns。所有的输入输出引脚都和TTL电平兼容,并且提供了数据写入的软件保护功能(SDP)和硬件保护,以防止在电源开关或外部干扰时芯片的误写操作。W29C040具有10年的数据保存能力。该芯片共有32个引脚。

W29C040的读数据操作由#OE和#CE控制。当W29C040向外部输出数据时,这2个脚都必须为低。当两脚之中任何一脚为高电平时,数据总线呈高阻态。

W29C040的写操作(擦除或编程)基于页模式:每页包含256字节,如果要改变某一页中的某个数据,则需将整页的数据都调入内存,否则,本页的其他数据将在写操作过程中全部被“FFH”填充。在写操作之前需将#CE脚和#WE脚置为低电平,#OE置为高电平。写操作包括2个周期:载入字节周期和内部写周期。载入字节周期就是将整个页载入内存;内部写周期就是将页缓冲区中的数据同时写入内存进行非易失存储。在字节载入周期,地址在#CE或#WE的下降沿进行锁存,数据在#CE或#WE的上升沿进行锁存。如果载入下一个字节在典型的字节载入时间(TBLC)200μs之内,W29C040将会继续处于页加载周期,则其他的数据可以依次连续载入。如果没有数据被载入到页缓冲器,则页加载周期将停止,开始内部写(编程或擦除)周期。地址线A8-A18为页地址选择线,所有载入页缓冲器内的数据必须处于同一页地址,A0―A7是同一页内的各个字节地址线。在内部写周期,页缓冲器内的所有数据(即256个字节的数据)被同时写入存储器阵列。在内部写周期完成之前,CPU可以处理其他事务,例如从其他地方取出数据以便准备写入下一页。

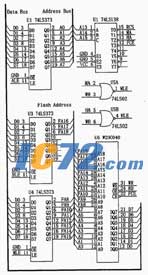

W29C040有19条地址线(一般Flash存储器都有较多的地址线),而MCS-51单片机只能提供16位的地址信号。可以用P1、P3中闲置的引脚作为高位地址,但是如果资源紧张,则难以奏效。一种有效的方法是,将高位地址从数据总线送出,安排锁存器先行锁存,要对W29C040进行读写时,将锁存器中的地址一并输出,实现地址信号的“分时输出、同时有效”。照此思路,可以采用如图2所示的结构。

对W29C040的读写操作,分三步完成:先向两个地址锁存器U3、U4写入高位地址,然后再向W29C040输出最低8位地址以及读写控制信号。如图所示,U3、U4的地址可分别为4000H和2000H,W29C040的高位地址为60H。

图2 W29040和单片机的连接原理图

3 编程方法

假设对W29C040读写的地址存放在flash ptr h、flash ptr m、flash ptr l三个存储单元,则对该地址读写的子程序就是:

read 29040:

mov dptr,#4000h

mov a,flash ptr h

movx @dptr,a

mov dptr,#2000h

mov a,flash ptr m

movx @dptr,a

mov dph,#60h

mov dpl,flash ptr l

movx a,@dptr

ret

write 29040:

push acc

mov dptr,#4000h

mov a,flash ptr h

movx @dptr,a

mov dptr,#2000h

mov a,flash ptr m

movx @dptr,a

mov dph,#60h

mov dpl,flash ptr l

pop acc

movx @dptr,a

ret

有了这两个子程序,W29C040的所有操作就相对简单了:像对整个芯片的擦除是一个六字节的命令,也就是六次写操作,依次向5555h、2aaah、5555h、5555h、2aaah、5555h单元写入aah、55h、80h、aah、55h、10h。子程序如下:

erase 29040:

mov flash ptr h,#00h

mov flash ptr m,#55h

mov flash ptr l,#55h

mov a,#0aah

call write 29040

..

ret

下面是对W29C040编程的例子,假设要写入的一页数据存储在外部RAM地址为flash wbuf的区域中,目标高位地址已经放入flash ptr h和flash ptr m:write page:

clr ea

mov b,#00h

mov flash ptr l,#00h

mov dptr,#flash wbuf

write byte:

movx a,@dptr

inc dptr

push dph

push dpl

call write 29040

inc flash ptr l

pop dpl

pop dph

djnz b,write byte

setb ea

wait:

call read 29040

mov b,a

call read 29040

xrl a,b

jb acc.6,wait

ret

需要特别指出的是,该子程序一开始便关了中断,其目的是要让整页数据的载入不要被外部事件所打断。否则,有可能提前进入内部写周期,使得实际写入数据不到256字节。最后检测内部写周期是否结束使用的翻转位(Toggle Bit)方法:如果内部写周期没有结束,则连续两次读出的数据的D6位是相反的,所以我们可以对同一个单元连续读取,根据该位两次读取结果是否一致来判断写周期是否结束。另一种检测内部写周期是否结束的方法是数据查询方式(Data Polling):当W29C040处于内部写周期时,读取先前载入的最后一个字节的结果,其最高有效位变成了真正数据的反码,只有读到的数据变回实际数据,才表明写结束,上述子程序可改为:

..

mov dph,#high(flash wbuf)

mov dpl,#0ffh

movx a,@dptr;最后一个字节实际数据

mov b,a

mov flash ptr l,#0ffh

wait:

call read 29040

xrl a,b

jb acc.7,wait

ret

4 结语

数据量和运算量的增大已成为各种微机控制系统面临的共同挑战。在不改变原有体系结构的基础上,采用大容量存储器,在当前是一种简便可行的办法。上面给出了在16位地址总线中扩展512K存储的一般方法,如果所需要的存储容量还要扩大,则有2种实现方式:使用单片更大容量的存储器和使用多片较小容量的存储器。实际上,以上原理图不用改动,就可以与24位地址、16M的Flash存储器相接口;如果要使用多片存储器,也只需将各片存储器的片选分别与译码器输出相联接,其余连线不变,还可以扩展4片。总之,按照这种连线方式,系统中允许有5片16M的存储器存在,足以满足各种要求。 |