1����

�뵼��洢��ͨ���ڵ�·�����ڴ�ų�������ݡ��ڳ��ڵĵ�·ʵ���У����߷��֣�ͨ�������ʧ�ԣ������粻�ᶪ���������ݣ����д洢���Ĵ洢��Ԫд���ض������ݣ��������ذ��Ų��д洢���ĵ�ַ�ߣ�An���������ߣ�Dn����ʹ�ܣ�CE�����ſأ�OE�����������ŵĹ��ܣ����Էdz�����ؽ�����Ϊ�����оƬʹ�ã������˵�·��Ӳ����ơ������ڴ洢���۸��൱�����Ľ��죬�����������ʹ�÷���ʧ�Բ��д洢�����������Լ�·��������ԡ���߿ɿ��ԣ�������Ч�ؽ����з��ɱ������Ľ��Է���ʧ�Բ��д洢����Ϊ����������ʱ����оƬ�����о�̽�֡����û���ر�ָ���������ᵽ�Ĵ洢����ָ����ʧ�Բ��д洢����

�����ֵ�·����У����dz���ϣ����ij���ض����ܵ�оƬ�����г��Ϻ����ҵ�����û��оƬ���ṩ����Ҫ�Ĺ��ܡ���ʱ��һ����ʵ���еİ취���Dz��ÿɱ����������PLD�����ƹ��ܣ����������ô洢����ʵ�֡����ַ����������ƹ㵽�������������͵ķ���ʧ�Բ��д洢������EPROM��EEPROM��Flash�ȡ���ʹ�Ժ��Ƴ������յķ���ʧ�Դ洢��оƬ��ֻҪ�Dz�������/����ģ��洢���������á�

2��EPROM2764��8k��8��ʵ�ֵļ��ֵ�·

2��1��2764��Ϊʮ�����ƣ��߶����������������

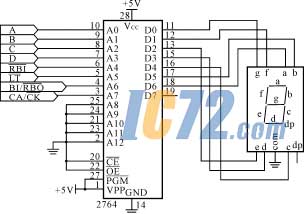

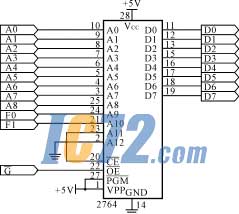

���ֵ�·�о�����Ҫʮ�������߶��������������оƬ����֪��74LS48��74LS248��оƬ����ֻ��BCD�룭�߶����������������������ȷ��ʾʮ������A��F�������ŵ�·��ƣ���Ȼ�����Ͽ��У�������оƬ̫�࣬���߹��ڸ��ӣ����ô洢��ʵ��ȴ�ܷ��㣬��������ѡ���������������������ƪ������ȥ2764��Ϊʮ�����ƪ��߶���������������������� 74LS48������ֵ����

��2764���д����ֵ���е����ݣ���ʹ��16����ַ��Ԫ��A3��A0:0000��1111������ʵ�ֻ�����ʮ�����������߶��������ʾ�Ĺ������빦�ܡ����Ҫ�������߶�������ǹ����ģ�ֻҪ��д��2764��������D6��D0ȡ�����ɡ�����ֻ����2764�洢��8λ�ֳ��е�7λ��δ�õ�D7�ɸ��ݵ�·������Ҫ����С������ʾ���������ܡ�

Ϊ��ʹ���������������������ֳ��ϵ���Ҫ���������롰����/����ѡ���ܣ�������74LS48���������¿������ţ�

CA/CK��������/����ѡ��Ϊ��ʱоƬ��Ϊ��������������Ϊ��ʱ��Ϊ��������������

BI/RBO���������/��һλ��Ч������������͵�ƽʱʹ�߶�ȫ��

LT�����Ʋ��ԣ�Ϊ�͵�ƽ��BI/RBOΪ��ʱ��a��g���ȫ�ߣ���������ܵ��߶ζ�������������������ܻ�оƬ�û���Ϊ��ʱ����������ʾ��

RBI������̬������룬Ϊ�͵�ƽ��LT��BI/RBOΪ��ʱ������ʮ������0ʱʹ����ܲ���ʾ������ʮ������ֵ����Ӱ�죨��������������ʾ��������ǰ����㣩��Ϊ��ʱ����ʮ������0����ʹ������������ɴ��ٰ�����ֵ�����ԣ���

����ֵ���е����ݰ���ַд��2764��û���õ��ĸ�λ��ַ��ȫ���ӵأ����Ǿ͵õ���һ������������ʮ�����ƣ��߶����������������,���ҹ����ϼ���74LS48��BCD�룭�߶������������������ͼ1Ϊ�����߶�����ܵĽ���ͼ��ͼ��CA/CK��2764��3�ţ�Ӧ�ӵأ���Ϊ������ǹ����͵ġ�RBI��BI/RBO��LT������ͽӷ���74LS48��ȫһ����

���ѿ�������2764��8K����ַ��Ԫ�����ǽ�ʹ���˵Ͷ˵�256����

2��2��2764��Ϊ��ͨ��ͬ��/������

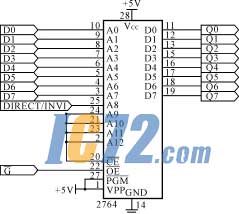

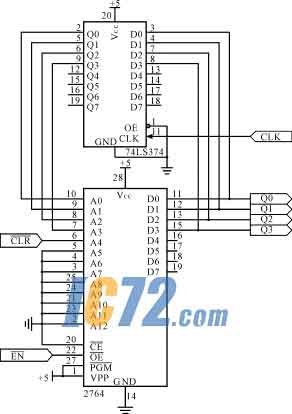

���ڵ�·��Ƶ���Ҫ������ϣ����һ��оƬ�ṩ8λͨ����ͨ��һ�����ŵĵ�ƽ���������������ͬ��Ƿ��ࡣ����֪����һ��������ǿ��Կ���һλͨ��������ģ������4�������74LS86����ʵ��ϣ���Ĺ��ܡ�������8ͨ����˵������Ҫ2Ƭ74LS86������1Ƭ2764�Ϳ���ʵ�֣���д��8ͨ��ͬ��/����������ֵ�����ԣ����ٽ���ֵ���е����ݰ����ַд�� 2764���Ϳ��Խ�����Ϊ8ͨ��ͬ��/�������ˡ�����2764�Ľ�A8���Ӹߵ�ƽʱ�������������ͬ��ģ��ӵ�ʱ������������Ƿ���ġ����ڿ����Ƿ�������ߵ�ƽʱ���Ϊ����̬�����Ǵ洢�������Ĺ��ܣ���д��������ء�ͼ2Ϊ�����Žӷ���ʵ��8ͨ��ͬ��/����������2764��512���͵�ַ��Ԫ��

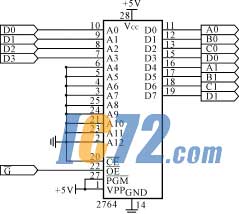

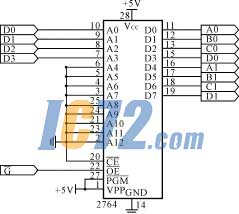

2��3��2764ʵ��ʮ�����ƣ���λ�����ƣ���BCD����ת��

�������ʮ��������Ϊ0��9��������Ϊ 0000��1001��ʱ�����������BCD��ĸ��ֽ���Ϊ0000�������ֽ����������λ��������ͬ���������ʮ����������A��F��������Ϊ 1010��1111��ʱ������ĸ��ֽ���Ϊ0001�������ֽ�Ϊ0000��0101��������ܿ������ŵ�·ʵ�֣���ʹ��1Ƭ74LS154���Ī�ʮ������������2Ƭ��74LS147��ʮ�ߪ��������ȱ�������8���������������൱�鷳������2764�洢��ʵ������ȴ�ر����ֵ���ԣ���

������BCD��ת����ʮ��������ִ���������෴��ת��������ת����·�ֱ��ͼ3(a)��3(b)��ʾ������ת�����ֱ�ռ��8k�洢�ռ��ǰ16����256����ַ��Ԫ������������1���洢��ʵ��2��ת���������⡣

2��4ʹ2764ͬʱ��������4�ֹ���

���������У����Ƕ�ֻ���õ���2764��8k�洢�ռ��к���һ���ֵͶ˵�ַ��δ�õ��Ľϸ�λ��ַ�߶��ǽӵصģ����Ծ�������洢��Ԫ�������š���ʵ������ȫ���Խ����ֹ��ܵ����ݰ���ַ�ֿ�д��2764�У������оƬ�������ʡ���ʹ��ʱ�����������øߵ�ƽ��͵�ƽ��ѡ�����Ҫ�Ĺ��ܡ�

ͼ4Ϊ��2764ʵ�������������ܵĵ�Ч��·��ͨ���ı�F1F0����2764��A10��A9�ţ��ĵ�ƽ���Ϳ���ʹ2764�ṩ��ͬ�Ĺ��ܡ�

���ڸ���������Ĵ洢�ռ䲻һ���࣬��������Ҫ���洢�ռ�Ĺ���Ϊ�����������ܵ�����Ҳ��ռ����ô��洢�ռ䣬��ֻʹ�����еĵͶ˵�ַ����Ȼ����������Ҫ�ռ�С�Ĺ��ܼ�����һ�𣬺���ʹ��һ���뵥����Ҫ�ռ�ϴ�Ĺ�����ͬ��С�Ĵ洢�������Խ�һ����ߴ洢�ռ�������ʣ����ڱ�����ռ�ÿռ�������8ͨ��ͬ��/������,����Ҫ512����ַ��Ԫ����������3������Ҳ��ռ��512����ַ��Ԫ��������������ڴ洢��ַ�˷ѵ����⡣��������ˣ�1Ƭ2764��ʵ�ֵĹ��������൱�ɹ۵ġ�����ÿ��������Ҫ512���洢��ַ���㣬2764��8K��ַ��Ԫ����ʵ��16��������Ĺ��ܡ��ɼ��ô洢��ʵ�����������оƬ���о����Խ�ԡ�

���������ӿ��Կ�����ʹ�ô洢�����Էdz������ʵ�ָ��������оƬ�Ĺ��ܣ������źŵ������Ŀȡ���ڴ洢���ĵ�ַ�������������ſ��źš�Ƭѡ�źŵȣ���������źŵ������Ŀ��ȡ���ڴ洢�����ֳ�����ˣ�����û���Ҫ�������źŽ϶࣬����ѡ��������Ĵ洢оƬ����Ҫ������϶࣬��ѡ���ֳ�Ϊ16λ��32λ��оƬ����֮��ֻҪ�洢����ַ�ߺ���������������Ҫ�Ϳ���ʵ���κο���������������ܡ�

��Ҫע����ǣ���������һ��ǿ���������������ʱ����������Ϊ�洢��û�����湦�ܣ��ڶ�ģʽ�£�������������ʵ��ʱ�����������ڴ洢�����롢������������������������8D������74LS373��8D����������74LS374��Ҳ�ǿ��Զ���ʱ�������ܵġ�

2��5��2764��������������

��������һ�֡���λ��ࡱ�룬���ص����������������ֻ��һλ���ȡֵ��ͬ�������ͨ������һ�ֿɿ��Խϸߵı��롣�����뻹���ڿ�ŵͼ�У����и����źŵ����ۺ��á�����λ�������������ԣ������Ƶ�����������ֵ�������1��ʾ��

�Ƶ�Ҫд��Ĵ洢�����ݣ�����1���ݵķ����ǣ���0����ַ��Ԫ������һ��Ӧ����ļ���ֵ��0001����Ȼ�˼���ֵ��Ϊ�洢����ַ���ڴ˵�ַ��д����һ���������ֵ�����ѭ��ֱ������ʮ�����洢��Ԫ�����������ݡ����ַ�����Щ�������ݽṹ�еġ�ָ�롱�����Ȼ�����Ҫ��ĸ�����λ���ܳ����ֹ���д�洢�����ݽ��dz���������ʱ��û����ü����������ɣ��㷨Ϊ������һ������A�������д�����Ӧ��ʮ����Ԫ�أ�A[0]��A[15]�����ȶԵ����Ԫ�ظ���һ��Ԫ�صĸ�����A[0]=0001�����±�Ϊ��ʮ����ֵ1��0001��������Ԫ�ظ���һ��������ĸ�����A[1]=0011���±�Ϊ3��0011��������Ԫ�ظ�A[3]=0010����������A[2]=0110��A[6]=0111......���̼�ͼ5��ʾ��ͨ��һ��ѭ���Ϳ����������������Ԫ�ظ�ֵ������A�Ͱ�����Ҫд��洢�������ݣ������±�Ϊ��ַ��Ԫ��ֵΪ�洢�����ݡ�

�� 1 �� λ �� �� �� �� �� �� �� ֵ ��

| CLR |

������������ |

��������� |

| A4 |

A3 |

A2 |

A1 |

A0 |

D3 |

D2 |

D1 |

D0 |

| 0 |

X |

X |

X |

X |

1 |

0 |

0 |

0 |

| 1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

| 1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

| 1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

| 1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

| 1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

| 1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

| 1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

| 1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

| 1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

| 1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

| 1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

| 1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

2764��74LS374�Ľӷ���ͼ6��ʾ�����ɵĸ������������CLKʱ�������ؼ�����CLR��A4������Ϊ������λ�õġ�����Ϊ�͵�ƽʱ��A3��A0������ʲô��ƽ����������ݶ���������A[9]Ԫ�ص����ݣ�1000���������һʱ�ӣ�CLK���������أ�Q3��Q0�������ַΪA[8]�����ݣ�0000���Ӷ�������ͷ��ʼ���ɼ�ΪCLRͬ�����㡣

��ʵ�ϣ�ֻҪ����1�������Զ�������Ϊ��ַ����Ӧ��������Ϊ����д��2764����һ����λ�����Ƽӷ�����������2764��ַ����ˣ����ܷ����ʵ�ָ�����������ܣ�����ֻ������������ɡ����Ա���ֻ��Ϊ��˵���ô洢��ʵ��ʱ���������ǿ��еģ���û��ʵ�ü�ֵ���ӱ��������Կ���������ʱ��������Ҫ�����������ķ����������ֹ���дʱ��������ֵ������������ӵöࡣ

3ʵ���������ʱ�������ܵ�һ�㲽��

1��ȷ����Ҫʵ�ֵĹ��ܣ�������Щ���롢����źţ�����Ŀ����ź����ȼ�˳���ж�ij�����źŵ����ȼ������ǣ����������Ч�����������ź�Ϊij����ƽΪǰ�ᣬ��ô���ź����ȼ��ϵ͡���2��1������RBIҪ��͵�ƽ��Ч����Ҫ��LT��RI/RBO��Ϊ�߲��У����������3���ź������ȼ���ͣ�ͬ��LT���ȼ���RI/RBO�͡�RI/RBOҪ�����ò���Ҫ�����ź�Ϊǰ�ᣨ���ﲻ�ؿ����ſ��źţ���Ϊ���������ַ�ߣ�������RI/RBO�����ȼ���ߡ�

2���滮�������źź�����ź�Ӧ�ӵĴ洢�����š�ͨ������������ź�Ӧ���ڵ�ַ��λ�����������λD0�Ӵ洢����ַ��A0���š������ź��������ȼ������ν�����ַ�߸�λ�����ȼ�Խ�ߣ���ַλԽ�ߡ�

3������ַ˳���г���ֵ���е����ݣ������������ݺͿ����źŵĵ�ƽ��ijһȷ��ֵʱ��Ҫ�����������ʲô��Ҫ��ϸ��ÿ����ַ��Ԫ��

4�����Ҫ��һ���洢��оƬ��ʵ�ֶ�����ܣ��ͽ������ֱܷ�������ֵ�����ۺ�ʱ���ҳ���������ռ�����Ĵ洢�ռ䣬������������Ӹ�λ��ַ�ߡ�������Ŀ��ʵ�ֵĹ������йء����磬Ҫʵ�ֵĹ�����5��8����Ӧ����3����λ��ַ�ߡ������͵õ��ۺϺ����ֵ����ҲӦ����ַ˳���г�����

5��������ֵ�����ɱ���õ������ļ���

6���ñ����������д��洢����

7������̳ɹ��Ĵ洢�����ڵ�·�У����չ滮�õ����롢����ź��������š����ڴ��ж�����ܵ�оƬ����Ҫ�����ۺ�ʱ����ֵ�����������Ӹ�λ��ַ�ߵĵ�ƽ��δ�õ��ĸ���λ��ַ�ߡ����ù�����δ�õ�

��ַ�����Ŷ�Ӧ�ɿ��ӵأ�����������š�

4�洢��������ȱ��

4��1�ŵ�

��PLD�еĿɱ�������У�PLA�����ɱ����������PAL����ͨ����������GAL��һ�����ô洢��ʵ���������ʱ������ʵ������һ�ּ����������Ӳ�����϶���оƬ���ܵķ���������߲�ͬ���ǣ��洢������ʵ�ʾ��Dz���������洢�����൱��һ��������������һ���кţ���ַ�����Ϳ��Դ�����õ���������һ�е����ݣ����洢�����ݣ���������������벢û��ʲô���ϵĹ�������PLA��PAL��GAL������������������ϵĹ�ϵ������������뾭��������õ��ġ����Ժ��߶�д������ݽ����ˡ�ѹ�������û���д����ЩоƬ֮ǰ��Ҫ����ֵ��������;�����ɳ����������������ϵ���洢������ȫ����Ҫ�û���������ֻҪ�����밴λ��ɵ�ַ�����ݵ�ַ��ʵ�ֵ�������ȷ��ϣ���õ����������ΪӦ��ŵ����ݡ���ֵ�����ݵ�ȡ�üȿ������ֹ��ķ�����Ҳ�����ó������ɡ����ڴ洢��û�ж����ݽ��С�ѹ����������кܴ������ȣ������ݴ�����Ҳ��PLA��PAL��GALǿ�öࡣ����Ҫ���ǣ����洢��оƬ�۸�������洢������������Խ���ʮ���������ɰ���ǧ��������Ĺ�����һ���洢��ʵ�֣���ͽ�һ��������ʹ�ô洢��ʵ�ָ��ֹ��ܵijɱ���

4��2ȱ��

��������ֱ�Ӷ���ʱ�������ܣ������������������ϲ���ʵ�֡�

�������Ҫ��ʵ�ֵ�оƬ��������˫���书�ܣ���74LS245������˫�أ���CD4016��CD4066�����Ͳ���ֱ���ô洢��������Ҳ���������·��ϡ�

����OC�ţ��洢���������OC�ţ���������ô洢���������ΪOC�ŵĹ��ܡ��������ǿ���ͨ���������ؼ��缫��·���������74LS07�����洢�����ת��ΪOC�������

�������ܽ��洢����Ϊ���Ӵ������������������á��洢��������ר�ŵ������������ܴ洢�����������������ź�ͬ�࣬����Ҫָ���洢��ͨ����̾���Ϊ������74LS244����ͨ��������/������������ô�������������

�����洢��Ҳ����ʵ��ʩ���ش�����������ʩ���ش����йصĹ��ܡ�ʩ���ش������ֳƵ�λ�����������������ȶ������״̬������������ֵ��ƽVT����VT�����������źŵ�ƽ�ɵ���߱仯����������ƽVT��ʱ������������������ijһ���״̬���������źŵ�ƽ�ɸ���ͱ仯����������ƽVT��ʱ����������ת����һ���״̬�����ʩ���ش������Ĵ������ͺ����ԡ��洢�������봿���Ե�ƽ�ߵ��ж���0��1�����Բ���ʵ��ʩ���ش�������ع��ܡ�

������PLA��PAL��GALоƬ��ȣ��洢��������ʵ�����ݼ��ܣ�����Ч����оƬ���ݵ�֪ʶ��Ȩ����ΪֻҪ�ڴ洢����ַ�˼��ϼ����źţ��ͺ����ؽ���洢���������ݶ�������GAL�ȿɱ��������ͨ�����ܣ��ɴ�������������Ϣ���Ѷȡ�

�����ڸ������ݴ���������Ӧ����Ϊ��оƬ�Ĵ洢����ϸ���Է���ʹ�ã��Ͼ��洢���Ķ���ʱ����һ��TTL��������ʱ�䣨100ns���ڣ���Ȼ��Ǻܳ��ģ�����2764�Ķ���ʱ������ͺŵIJ�ͬ��100ns�� 450ns���ȣ���CMOS4000ϵ����Щ�ӽ���EEPROM��Flash�Ķ���ʱ��Ҫ��һЩ�������DZ�TTL���������Ƶĵ�·�����ڸ������ݴ������ʱ��Ҫ��dz��ϸ�ij��ϣ��ô洢����������оƬ�Ϳ��ܵ���ʱ�����ҡ���ʱӦ����GAL���ֳ��ɱ�������У�FPGA��������Ŀɱ��оƬ����������������յĸĽ����洢������ʱ����TTL�൱ʱ����һ�����Ծ���Ȼ���ٴ��ڡ�

5����

�ò��д洢����ʵ���κ���������ܣ�������ֻ���������ַ�ߺ���������ߵ������������Խ��������ܼ�����һƬ�洢���У�ʹ��ʱͨ�������ŵ�ƽ���п�����ѡ��Ҫʵ�ֵĹ��ܡ���PLD��ȣ��ô洢��ʵ�������������������Խ�ԡ��������ô洢������ֱ��ʵ��ʱ�������ܣ�������Ӳ�����ƣ��洢��������һЩӦ���ϵľ����ԡ���������ô�����ܶೡ�������ô洢������оƬ���ܣ��ڵ�·��ơ�����ʱ�϶����յ��°빦����Ч���� |