随着各种电路和芯片的性能(速度、集成度等)不断提高,尤其是在军事、航空航天等用途中对可靠性的要求往往是第一位的,人们对于系统的可靠性方面的要求日益增加,这对电路系统的设计和制造都提出了严格的目标要求。

存储器是电路系统中最常用的器件之一,采用大规模集成电路存储芯片构成。实际统计表明,存储器在太空应用中的主要错误是由瞬态错误(也叫单个事件扰动,SEU)所引起的一位错[1]或者相关多位错,而随机独立的多位错误极少。半导体存储器的错误大体上分为硬错误和软错误,其中主要为软错误。硬错误所表现的现象是在某个或某些位置上,存取数据重复地出现错误。出现这种现象的原因是一个或几个存储单元出现故障。软错误主要是由α粒子引起的。存储器芯片的材料中含有微量放射性元素,他们会间断地释放α粒子。这些粒子以相当大的能量冲击存储电容,改变其电荷,从而引起存储数据的错误。引起软错误的另一原因是噪声干扰。同时在太空环境下,在带电粒子足够能量撞击下,存储器的存储单元中的位发生翻转从而产生SEU错误 [2] 。本文设计实现了用CPLD技术和纠检错芯片对存储器进行容错,大大提高了系统的可靠性。下面是具体容错存储器和门警电路的设计。

1 检错与纠错原理

常用的能检测2位错同时能纠正1位错(简称纠一检二,SEC-DED [3、4] )的纠错码有扩展汉明码(Extended Hamming Code)和最佳奇权码(Optimal 他们的最小码距都为4,两者有相似之处,如冗余度一样,对于数据位数k,校验位数r应满足2 r-1 ≥k+r。当k=16时,r=6,数据位长增加1倍,校验位数只需增加1位,编码效率较高。另外从来源上讲,两者分别是汉明码的扩展码和截短码,也有资料称最佳奇权码为修正汉明码(Modified Hamming Code)。文献[4]介绍了SEC-DED和SEC-AUED)码的编解码理论。从性能上看最佳奇权码比扩展汉明码更为优越,前者在纠检错能力方面也优于后者,他的3位错误的误纠概率低于后者,而4位错误的检测概率高于后者,最重要的是他便于硬件实现,故应用的最多,本文采用最佳奇权码。

首先构造最佳奇权码的校验矩阵即H矩阵,最佳奇权码的H矩阵应满足:

(1)每列含有奇数个1,且无相同列。

(2)总的1的个数少,所以校验位、伴随式生成表达式中的半加项数少,从而生成逻辑所需的半加器少,可以节约器材、降低成本和提高可靠性。

(3)每行中1的个数尽量相等或接近某个平均值,这种决定生成逻辑及其级数的一致性,不仅译码速度快,同时线路匀称。

应用中采用(13,8,4)最佳奇权码,数据码为(d7 d6 d5 d4 d3 d2 d1 d0),校验码为(c4 c3 c2 c1 c0),P矩阵和编码规则分别为:

译码时把数据再次编码所得到的新校验位与原校验位模2加,便得到伴随式S,由其可判别错误类型:

(1)若S=0,则认为没有错误;

(2)若S≠0,且S含有奇数个1,则认为产生了单位错;若S≠0,且S含有偶数个1,则认为产生了2位错。

因此,错误图样S=[s 0 s 1 s 2 s 3 s 4 ]与产生的错误一一对应,从而实现纠一检二功能。

2 存储器容错芯片设计实现

2.1 存储器设计实现方案

(1)备份行(或列)方案

这种方案是在存储芯片的设计与制造过程中增加若干备份的行(或列)。在芯片测试时,若发现失效的行(或列),则通过激光(或电学)的处理,用备份行(或列)去代替。此方法的优点是设计简单,管芯面积增加较少,电路速度没有损失。但是,他需要增加某些测试与修正实效行(或列)的工艺环节,更重要的弱点是这种方案仅适用于RAM,不能用于ROM。

(2)纠错编码方案

这种方案是在存储芯片内部采用纠错编码,自动检测并纠正错误。此方案不需要额外的测试和纠正错误等工艺环节,除提高成品率外,还对可靠性有明显改进。这种方案最突出的优点是特别适合ROM;在对速度要求不高的情况下也可用于RAM。他的主要缺点在于要占用额外的芯片面积,同时因编译码而影响芯片整个的工作速度。将用于存储器系统级的纠错编码等容错技术引入存储器芯片内部,是提高存储芯片成品率和可靠性的有效措施。例如服务器中使用的ECC内存就采用了此技术。

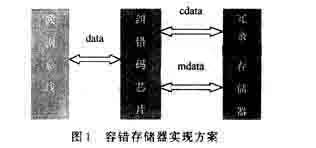

本文的容错存储器采用纠错码方案,其实现框图如图1所示。

2.2 纠检错电路设计

纠检错电路必须配合CPU的读写时序进行工作,可以将CPU的时序分为读周期和写周期。在写周期时,总线通过纠错电路直接将数据写入到存储器,同时数据通过纠错电路产生5 b校验码写入到冗余存储器。读周期时分成2步,第1步从存储器和冗余存储器分别读取数据和校验位数据送入纠错电路锁存;第2步进行检错,如果没有错误直接将数据送出到数据总线,有2位错产生中断进行处理,有1位错对数据进行纠错并送入数据总线。因需要的是正确数据,如果是校验位出错则不进行任何处理,直接输出正确数据。

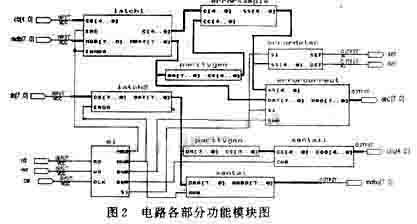

2.3 电路输入输出设计

RD,WR,CLK为CPU输入到纠检错信号,通过控制电路产生芯片内控制信号。在写信号时,DB[7..0]从数据总线输入,通过锁存以后经过三态控制(Santai模块)写入到存储器,同时数据通过校验码产生模块(Paritygen)产生5 b校验码,通过三态控制写入冗余存储器。读信号时,存储器数据读入纠检错电路经过锁存后产生5 b校验码,同时与从冗余存储器读入的5 b检验码一起通过错误图样模块(Errorsample),产生错误图样。通过错误图样检测错误,当数据产生错误时通过纠错模块(Errorcorrect)纠错后将正确数据输出到数据总线。Errordetec为错误状态模块,SEF,DEF为错误状态信号。0,0时无错,1,0时1位错,1,1时2位错。电路实现的各部分功能模块如图2所示。

3 仿真及其波形

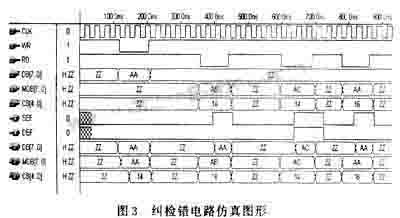

本文采用Altera公司的CPLD器件EPM7128作为设计环境 [5] ,图3是纠检错电路仿真图形,用CPLD实现纠检错电路仿真,图中118~205 ns时从数据线上写入数据AA,359~443 ns时仿真了读数据时产生1位错情况,601~692 ns时仿真了产生2位错情况,此时检测到了2位错,但是不能纠正。781~863 ns时仿真了校验位产生1位错时的情况。

4 分析与结论

本文利用最佳奇权码的基本原理设计的纠错码电路可以校正单位错,检出2位错,存储器不因单位错而中断工作,故其平均无故障时间MTBF增大,提高了可靠性。但是纠一检二码的新增器材又使MTBF有所下降。

在效率上,设在时间T内,发生1位错的次数为n 1 ,发生2位及多位错的次数为n 2 ,采用纠错码时,平均无故障时间为T 1 =T/(n 1 +n 2 ),采用最佳奇权码后,1位错是可纠的,仅2位及多位错是不可纠的,作为出错处理。设由于采用纠错码而增加器材δ%,因而采用最佳奇权码后的平均无故障时间为:

据资料估计,对于1位错占整个错误的比例 增益G=4.6~9.3。通过CPLD来实现存储器的容错,大大缩短了设计开发周期,降低了成本,同时提高了系统的可靠性。 增益G=4.6~9.3。通过CPLD来实现存储器的容错,大大缩短了设计开发周期,降低了成本,同时提高了系统的可靠性。

|