1 ����

������֪���ڸ��ӱ��������£�Ҫ����СĿ�����ȷ��Ч�غ�����١�̽����һ�����⡣��������£�����Ŀ���뱳���ĶԱȶȽ�С������Ƚϵͣ���ֱ�ӽ��и��١�̽�������Ƚ����ѣ����Ա����ȶ�ͼ���źŽ����˲�Ԥ�������Դﵽ���Ʊ�������������Ŀ��ǿ�ȣ��Ӷ����ͼ������ȵ�Ŀ�ģ�Ϊ���������������õĻ�����

ʵʱͼ�������У��ź�Ԥ����������ͼ��ĸ����˲���ֱ��ͼͳ�Ƽ����⡢ͼ����ǿ���Ҷȱ任�ȣ����ǹ�ͬ���ص��Ǵ����������������һ���������ʵ���Ʊػ�Ƚ�����������һЩʵʱ��Ҫ��Ƚϸߵ�ϵͳ�������ٶ�������Ҫ���ǵĹؼ����أ�һ���ٶȸ����ϣ�ʵʱ��Ҳ��̸�����ͼ��Ԥ����������ṹ�Ƚϼ��ص㣬��FPGA����Ӳ��ʵ�������������ѡ������ͬʱ������ٶȺ�����ԣ���������DSP�ĸ�����

��ϵͳ����Verilog HDL���ԡ�����һ�ֿ��ٵ���ֵ�˲��Ľ��㷨�Ե�·������ƣ�����Altera��˾������Stratix II EP2S60F67214��FPGAоƬΪӲ��ƽ̨���������̳���Altera��˾Stratix IIϵ�еĹ�ͬ�ŵ㣬����������ո�µ�����Ӧ��ģ��(ALM)��ʹ��Stratix II�и��ߵ����ܺ�����װ�����ٵ����Ͳ������Լ���ǿ��DSP֧�֣���Stratix II EP2S60F67214���DZ�Xilinx��˾����������Virtex-4XC4VLX60���18���������������а���51 182���Ĵ���λ��2 544 129���洢��λ�Լ�48 352��ALUT����������Դ�ḻ��ֻ��ռ�ú�Сһ����ʵ����ֵ�˲�����Ϊ������Ƶ��������и���ռ䡣

2 ��ֵ�˲��Ļ���ԭ�����Ľ��㷨

2��1��ֵ�˲��Ļ���ԭ��

��ֵ�˲�����Tukey������һ�ַ������źŴ�����������������һά�źŴ����������ܿ챻�õ���ά����ͼ��ƽ���У���һ����Ч����ͼ�����������ͼ������ȵķ������˲�����������һ���������㣬�����ھ�����������IJ��Ǽ�Ȩ��ͣ����ǰ������е����ذ��Ҷȼ���������Ȼ��ѡ�������м�ֵ��Ϊ�������ֵ�����ֵ�˲����Լ����������˲�����ȣ���ֵ�˲�����ͻ���ص����ںܺõ��˳���������(Impulsive Noise)�ͽ�������(Salt and Pepper Noise)��ͬʱ�����ܹ�����Ŀ��ͼ���Ե������ϸڡ��ù�ʽ��ʾΪ�?br>

g(x��y)=median{f(x-i,y-i)}��(i,j)��S (1)

ʽ��g(x��y)��f(x,y)Ϊ���ػҶ�ֵ��SΪģ�崰�ڡ�

����ֵ�˲��ľ���ʵ�ֹ���һ��Ϊ��

(1)ѡ��һ��(2n+1)��(2n+1)�Ļ�������(ͨ��Ϊ3*3����5*5)��ʹ����ͼ�����ݵ��л����з��������ػ���(ͨ��Ϊ�������ң����ϵ��������ƶ�)��

(2)ÿ�λ����Դ����ڵ����ػҶ�ֵ�����������������õ��м�ֵ���洰������λ�����صĻҶ�ֵ��

2��2��ָ�˲��ĸĽ��㷨

��ֵ�˲����㷨�ܶ࣬��ͨ�������������ϴ���Ҫ���Ĵ���ʱ�䣬������ͼ������ʵʱ�ԡ����IJ���һ�ִ��ڴ�СΪ3*3�Ŀ��������㷨���������������

Ϊ�˱���˵������3*3�����ڵĸ������طֱ���ΪM11��M12��M13��M21��M22��M23��M31��M32��M33�������������1��

���ȷֱ�Դ����е�ÿһ�м������ֵ����ֵ����Сֵ������һ�����Եõ�9����ֵ���ֱ����3�����ֵ��3����ֵ��3����Сֵ��

��һ�е����ֵ��Max1=max[M11��M12,M13]��

��һ�е���ֵ��Med1=med[M11��M12,M13];

��һ�е���Сֵ��Min1=min[M11��M12,M13]��

�������ƣ�

Max2=max[M21��M22,M23]��Med2=med[M21��M22,M23]��Min2=min[M21��M22,M23]��

Max3=max[M31��M32,M33];Med3=med[M31��M32,M33]��Min3=min[M31��M32,M33]��

ʽ��,max��ʾȡ���ֵ��med��ʾȡ��ֵ��min��ʾȡ��Сֵ��

�����жϣ�9����ֵ�С�3�����ֵ�е����ֵ��3����Сֵ�е���Сֵһ����9�������е����ֵ����Сֵ��3����ֵ�е����ֵ���ٴ���5�����أ��������е���Сֵ������2�е���ֵ����Сֵ����3����ֵ�е���Сֵ����С��5�����أ��������е����ֵ������2�е���ֵ����Сֵ����Ƚ�3�����ֵ�е���СֵMin_of_Max��3����ֵ�е���ֵMed_of_Med��3����Сֵ�е����ֵMax_of_Min���õ����м�ֵ��Ϊ�˲��������Med_of_nine��������̱�ʾ���£�

Min_of_Max=min[Max1��Max2,Max3]��

Med_of_Med=med[Med1��Med2��Med3]��

Max_of_Min=max[Min1��Min2,Min3]��

������˲������

Med_of_nine=med[Min_of_Max,Med_of_Med��Max_of_Min]��

��������������ֵ�˲��������17�αȽϣ��봫ͳ�㷨��ȡ��Ƚϴ��������˽�2�����Ҹ��㷨ʮ����������FPGA�������д��������������˲����ٶȡ�

3��ֵ�˲���Ӳ����·���

�ؼ�Ҫ���2��ģ�����ƣ��ֱ��ǣ�

3��1 3*3����ģ��

��Ӳ��ʵ�ֶ�ά��ֵ�˲�������Ҫ��һ�����ܿɿ��ش洢ʵʱͼ�����ݣ�����ʹ��ʱ��̡�Ϊ������ʵʱ�Ե�Ҫ��ͼ�����ȫ֡Ԥ������������ȫ֡Ԥ�����������Ƚ���֡ͼ��������ȫ�����ڴ洢���к��ٶ�ȫ֡ͼ�����ݽ��д��������Ǵ洢n-1��ͼ�����ݺ�㿪ʼ����������nΪ���ڴ�С���ڱ�����У�ѡ��3*3���ڵ���ֵ�˲�������n=3��������Ƶĺô��ǣ�FPGA�����Դ�����ˮ��ʽʵ�ָ�ģ�飬��ʡ������ʱ�䣬Ϊʵʱ��������������������ͼ1����3*3������ֵ�˲�Ӳ����ͼ��

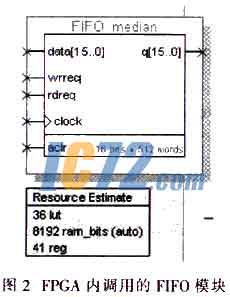

ͼ1�У�D������ʱ����FIFO�����Ƚ��ȳ��洢�������Ƚ��ȳ��洢��ģ����ͼ2��ʾ��wrreq��rdreq�ֱ�Ϊд����ʹ�ܣ�aclrΪ�첽���㡣ͼ������������ʱ�ӽ��Ĵ�����������������룬FIFO�����洢һ�����ݣ��Ӷ�ʹM11��M12������M33���ö�Ӧ3*3���ڵ�9��ͼ������(����1)�������������ϴ��������������ʱ��3*3ģ���Ӧ��ͼ�����ݲ��ϵظ��ű仯�������Ϳ��Զ�һ֡ͼ����������ض�����3*3ģ�崦����

3��2 3*3������9����ֵ������ģ��

��ǰ��2��2�ڶ���ֵ�˲��Ľ��㷨��˵�����ѿ�������������ʵ�ʾ���Ҫ����7��3ֵ�Ƚϣ�

1) 3*3����ÿһ�е�3�������бȽϣ��ֱ�ó�ÿ�е����ֵ����ֵ����Сֵ��һ����3�У���3��3ֵ�Ƚϣ�

2)3�����ֵ�顢��ֵ�顢��Сֵ�����3ֵ�Ƚϣ�3������3��3ֵ�Ƚϣ�

3)���ֵ���е���Сֵ����ֵ���е���ֵ����Сֵ���е����ֵ3�����ٽ���һ�αȽϡ���1��3ֵ�Ƚϡ�

Ϊ�˾�����Լ��Դ���������Ӳ������е�"ģ�鸴��"ԭ��ֻ�������һ����3ֵ�Ƚ���ģ�飬7�ε��ø�ģ�鼴�������������ֵ�˲�����

���⣬��ͼ��ĸ�����Ե����������3*3���ڸ���(���ڵ�һ����Ҫ���ǵ�ͼ����ⲿ)��������ֱ�ӵ��ø���ֵ�˲�����ģ�顣�ο��˴������������ͼ��Ӳ������ϵͳ�����������Ľ�ͼ���Ե���ؼ����"0"��������Ӱ��������ֵ�˲���Ч��������ֻ���ټ�һ���жϴ���λ�õ�ģ�飬����жϽ���DZ�Ե����������ģ�����"0"ֱ�Ӹ�������ˣ���֮������ø�����ģ�顣

4 ����FPGA�Ĵ������

������·�����ʹ��Verilog HDL���Ա�д����Altera��˾��Stratix II EP2S60����ΪӲ��ƽ̨����Quartus II 5��1����������������ʵ��320*256*16 bit�Ҷ�ͼ�����ֵ�˲�����ͼ��1��ʱ����20ms(���г�����ʱ��ԼΪ6��35 ms)������ʱ����6 MHz���㷨ռ����Դ���2��ʾ��

�ɱ�2�ɼ�������ֵ�˲���Ƶ�оƬ��Դռ�����Ƿdz�С�ģ���˾�����Դ�������ں����Ŀ�������С�����һ����������ʱ���ԼΪ4��2 ms����ȫ��������ϵͳ���ٶȵĸ�Ҫ��ͬ����3��3ģ����ֵ�˲�����ADI��TS201��DSP�ϴ���������ʱ��ԼΪ15��3 ms���Զ���������Stratix II EP2S60��ʵ�ֺ���ͼ�����ֵ�˲��Ȼ���TS201��ʵ���и��õ�ʵʱ�����ƣ����Ҹ����ʹ���˿�����ֵ�˲��㷨�����Աȴ�ͳ�㷨��Լ�˸���ʱ�䣬��Դռ����Ҳ�dz�С�����롢���ͼ��ֱ���ͼ3��ͼ4��ʾ�����ڱ��˲�ģ��ѱ�Ե��Ϊ0������ͼ�ı�Ե��һ�����ߡ��Ա�ǰ��ͼ����Կ�����ֵ�˲��Խ��������кܺõ��˲����á�

5 ������

����Ʒ���������һ�ָĽ��Ŀ�����ֵ�˲��㷨���ɹ�����Altera��˾�ĸ�����Stratix II EP2S60��ʵ���������ֺ���ͼ���˲����ڱ�֤ʵʱ�Ե�ͬʱ��ʹ��Ӳ�������Ϊ����������˳ɱ������к�ǿ��ʵ�ü�ֵ������ٽ�������˲�Ԥ��������������Խ�һ��������˳����������������õظ���ͼ������������Ʒ���ֻ�������ھ�����3*3ģ�壬�����������͵�ģ��(��5*5ģ�塢ʮ������ģ��)����Ҫ���½���ϵͳ��ơ����⡣��FPGA����У�һ��Ҫ�ϸ����ʱ��֤ʱ�����㹻�Ľ���ʱ��ͱ���ʱ�䣬����֤ʱ����ϸ�ͬ������·����ʱӦ�þ�����С�� |