摘 要:研究分析了CMOS多晶电容的工艺误差,给出了氧化硅介质层厚度的梯度误差、边际效应等工艺因素对CMOS多晶电容的影响。基于单位电容的改进设计,给出了CMOS多晶电容阵列的共心设计方法。采用0.6μm CMOS DPDM工艺,实现了基于CMOS多晶电容阵列的开关电容带通滤波器,实验结果表明本文的CMOS多晶电容设计方法具有较高的精度,能直接用于亚微米及深亚微米集成电路设计。

关键词:多晶电容;CMOS;工艺误差;共心分布

1.引言

电容是CMOS模拟集成电路中非常重要的器件,RC振荡器、RC滤波器等诸多模拟电路的性能都取决于电容的实现精度,CMOS开关电容滤波器的时间常数是由电容的比值来决定,与电容的绝对值无关。在目前标准的CMOS集成电路技术中,片内电容的典型电容值误差在设计值的10-30%之间,很难实现高精度的电容,所以研究分析CMOS电容的工艺误差和优化电容设计方法是非常重要的。

文献1系统的分析了CMOS电容的不匹配误差,但是没有给出减小误差的版图设计方法。文献2/3在分析CMOS电容的工艺误差的基础上,给出了传统的单位电容设计方法,但是没有考虑CMOS单位电容的边际效应等误差。

本文基于CMOS多晶(Poly)电容,分析了集成电路工艺引起的随机误差及系统误差。基于多个等值小电容并联实现电容的设计方法为单位电容设计方法,针对CMOS开关电容电路,系统研究了单位电容设计方法,提出了最优化的单位电容尺寸和共心电容阵列设计方法,有效的减小各种工艺误差。基于0.6μm CMOS DPDM工艺,采用本文提出的设计方法,实现了CMOS开关电容带通滤波器,实验结果与传统的开关电容滤波器进行了比较,以验证本文设计的正确性。

2.Poly电容的工艺误差分析

Poly电容的工艺误差主要为随机误差2/3,可分为全局随机误差和局部随机误差。全局随机误差主要影响电容面积的周长,即电容的边际效应;局部随机误差主要是电容介质层厚度的随机误差,如多晶电容的氧化硅介质层。对于正方形的Poly电容CK,全局随机误差引起的相对误差为CK-3/4,局部随机误差引起的相对误差为CK-1/2[1]。如果将Poly电容CK分为NK个等值Poly电容CNK,每个等值Poly电容的局部相对误差为CNK-1/2,但是能将Poly电容全局相对误差减小NK1/4倍。

Poly2的侧面与Poly1等附近层次所形成的寄生电容为Poly边际电容。Poly边际电容增加了电容的有效值,并会引起电容及周边器件的串扰。通过在电容周围引入保护环,不仅能有效抑制Poly边际电容对周边器件的串扰,也能有效的减少Poly边际电容。

在集成电路制造中,光刻胶的曝光程度存在一定的差异性,所以器件面积及周边形状就存在一定的误差,对Poly电容也会产生一定的影响。如果电容的Poly2层的周边形状完全一致,则能减小光刻曝光的不均匀,其中基于单位电容的设计方法能将曝光不均匀性最小化。基于单位电容所设计的Poly电容,其Poly之间的氧化硅介质层厚度决定了方块电容值,但是整个晶圆(Wafer)的栅氧化层厚度存在同方向的梯度误差,所以高精度电容的设计也需要考虑氧化层厚度的梯度误差。本文基于单位电容所提出的共心版图设计方法,能有效的减小梯度误差对电容值的影响。在基于单位电容的设计方法中,一般采用第一层金属(Metal1)连接并联电容的上基板Poly2,所以金属连线与Poly1之间存在互连寄生电容,增加了设计电容的有效值。本文基于单位电容所提出的共心版图设计方法,也能有效的减小互连电容对电容值的影响。

Poly电容的工艺误差除了上述几种因素外,集成电路内部部分较大功耗引起的热梯度也会对电容值产生一定的影响,光刻掩膜板(MASK)的误差也会引起电容值的误差。通过结合具体的电路功能,合理设计版图的布局,合理选择单位电容的面积周长比,能减小这些误差。

3.基于单位电容的共心电容设计方法

3.1 单位电容设计

由于单位电容的全局随机误差随着周长的增加而增加,所以单位电容的周长应尽可能的小。同时,电容的全局随机误差随着单位电容的数目NK的NK-1/4,以及为了保证芯片面积的利用率,单位电容的面积应尽可能的大,所以必须合理选择单位电容的面积,并保证单位电容面积周长比的最大化。传统的单位电容为边长L的正方形,其面积周长比为0.25L;如果为等面积的圆形单位电容,则面积周长比为0.282L。由于集成电路光刻技术对圆几何形状存在较大的误差,由于135o角有利于提高单位电容的面积周长比[1],所以本文采用图1所示的单位电容几何形状,边长为L,0≤x≤L。

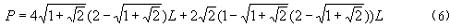

近似值为S=0.9534L2。对应的单位电容周长P为

近似值为P=3.6407L。所以得到的面积周长比约为0.262L,虽然比圆的面积周长比要小,但是比正方形的面积周长比要大得多,并考虑了光刻及制版的几何误差。在基于亚微米CMOS工艺的实际设计中,L的长度以10~30μm为适宜。

3.2 基于共心算法的电容阵列设计

基于图1所示的单位电容并联实现电容时,必须合理布局单位电容阵列,以减小各种工艺误差。假设采用NK个单位电容Cunit并联实现电容CK,氧化硅介质层的梯度误差为常数,选择一坐标,围绕该坐标点对称对称分布单位电容,以减小氧化硅介质层的梯度误差,这就是本文提出的共心电容阵列布局。

在共心电容阵列布局设计中,如电容CK由奇数个单位电容Cunit并联实现,即NK为大于1的奇数,则放置3个单位电容在共心坐标上,其它的NK-3个单位电容对称分布于共心坐标的周围;如果NK为大于2的偶数,则放置2个单位电容在共心坐标上,其它的NK-2个单位电容对称分布于共心坐标的周围。

4.实验结果与讨论

基于本文提出的单位电容及阵列设计方法,采用0.6μm CMOS DPDM工艺,设计实现了CMOS电容阵列,应用于中心频率为2130Hz的CMOS开关电容带通滤波器,并在同种工艺下与传统的单位电容阵列设计方法进行了比较,图2(a)为传统单位电容阵列的芯片照片,图2(b)为本文的单位电容阵列的芯片照片。0.6μm CMOS DPDM工艺的Poly电容PCM参数为0.80±0.15Ff/μm2,图2(a)和(b)中的单位电容值均为0.08Pf,即有效电容面积为100μm2。

CMOS开关电容带通滤波器的频域特性主要由相关的电容比值决定,所以通过测试芯片的频域特性及动态范围,就可以验证本文提出的单位电容设计方法。开关电容滤波器的动态定义为20log(Vimax/Vimin),其中Vimax是开关电容滤波器的输出端在没有明显失真条件下的最大输入信号幅度;Vimin是能够从输出噪声中识别出开关电容滤波器输出电压的最小信号幅度。动态范围越大,则电容的设计精度越高,开关电容滤波器处理小信号的能力越强;通带中心频率的增益越高,则电容的设计精度越高,滤波器的滤波特性更正确。表-1为分别采用图2(a)和(b)的单位电容设计方法的测试结果。测试结果表明,采用本文提出的单位电容设计方法的开关电容滤波器具有更大的动态范围和更高的中心频率增益,即验证了本文提出的电容设计方法的具有较高的设计精度。

5.结论

电容是CMOS模拟集成电路中的最重要的器件之一,研究CMOS电容的工艺误差及高精度设计方法,对模拟集成电路及混合信号集成电路设计具有重要的指导意义。本文从CMOS多晶电容的工艺误差分析研究出发,提出了单位电容的改进设计方法,并给出了基于改进单位电容的共心电容阵列设计方法。采用0.6μm CMOS DPDM工艺,物理实现了传统电容阵列和共心电容阵列,并应用于CMOS开关电容带通滤波器,实验结果表明了本文的CMOS电容设计方法在精度上实现了较大的提高。 |