�� ����

���ż��ɵ�·���칤�������ߴ�ij�����С�ͻ������ڵ����ܶȵ�Ѹ��������ο����������ص��ɵ�Ǩ�ƣ��������������������ЧӦ��������������ˣ���Ϊ��������ͭ���������е�һ����Ҫ����ۣ��ݡ�����ʿ�﹤���Ʊ���ͭ����ϵͳ�ڵ���������ͨ������������ɢ��������硢ͭ����ɢ�赲�㣨�ã������������桢ͭ�����ϵ���ʸ��Dz�֮��Ľ��棨��ͭ�ߵ��ϱ��棩�ȡ���ԭ��Ǩ�ƻ��Ƶ��о���������������Ҫ��ԭ������ͨ����ͭ�ߵ��ϱ���ۣ�-���ݡ�ͨ������ã�ףУۣ��ݻ�ԣ�ۣ��ݵȽ����Ա��渲�Dz�������������ͨ���ѱ�֤���ܹ����������ͭ�ߵĿɿ��ԡ�Ȼ�����ڵ����ı䷽����κξֲ����ᷢ������ӵ��������ӵ���Ĵ���ʹ��������·����ȷ�ϸ��Ӹ��ӻ�������ĵ���ӵ�������ܹ�ͨ���ṩһ������������������Ƶ�Ǩ��ЧӦ�ۣ��ݣ�������ʹijЩԭ������ͨ�����и����ԭ��Ǩ�����ʣۣ��ݡ��ڱ����У�һ��ר����ƵIJ��Խṹ���ԷŴ�ͭ����ɢ�赲����洦�ĵ���ӵ��ЧӦ��ͨ���Ըýṹ��ʵ���������ֵ����������������ͭ�������ڵ���ӵ�����������˵�Ӱ�졣

�� ʵ��ͽ��

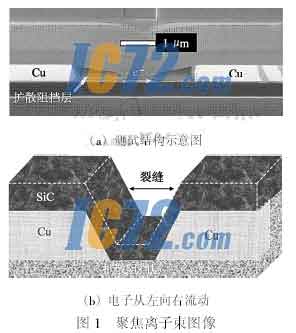

���õ������ʿ�﹤���Ʊ��IJ��Խṹ��ͼ����ʾ���������γ��ȷֱ�Ϊ�������̣���ͭ�ߣ��м�ͨ�����̣�������ɢ�赲��ĵ棨������������£̣������ӡ��ڱ��������õIJ��������£����Ӵ����ͭ������£̣����������ߵ���ģ£̣�Ȼ������Ҳ�ͭ�ߵ������ˡ��ڵ��ӽ���ͭ�ߵľֲ��������ڵ����������仯���������Եĵ���ӵ������ˣ����Ҳ�ͭ�������˸�����ͭ����ɢ�赲���������ĵ����ܶȱȽϸߣ��Ӷ�������ԭ���������ͨ�����ˡ�

��Ʒ���Ʊ��������£����Ȳ��ñ��ĵ������ʿ�﹤�����Ʊ�ͭ�����ߣ�������ƺ�ƽ������ͭ�߱������ڣ����������ģӣ�ϣ������У�ͭ�߿��ȴӣ�.���̣��仯�������̣������ϸ��ǣ��������ģӣ�ò���ΪӲ��ģ��Ȼ��ʹ�ÿ���Ϊ���̣�����ģ��ͣ��Σȣ������ӣ��ϣ���Һ����ʪ����ʴ��ȥ����Լ���̣���ͭ�飬¶��ͭ���������ɢ�赲�㣻���һ�㣵�������ģӣ�����ۻ����档����Ʒ�ṹ�൱����ͭ�������г���һ����Լ���̣����ѷ죬���Գ�֮Ϊ�ӽṹ����Ǩ��ʵ�����ھ�Բ����̽��ƽ̨�Ͻ��У�ͭ�����ĵĵ����ܶ�Ϊ��.�����ͣ���������������¶ȷ�ΧΪ���������������档

��Ȼ�������������о��������˵Ĵ�ͳ�£����ṹ�ۣ�-������Щ���ƣ����ӽṹֻ��ͨ��������ͭ�����߿�ʴȥ��һС��ͭ�鼴�ɵõ����ʶ��ܹ�ʹ�ñ��ģ������ �ԣ�Σ��ԣ��ݲ�ͱ��ĺ��ӿ飨�������䣩���ڣ£����ṹ�б�Ӧ���ۣ�-���� �������-���������ܺ��ԣ����������ǵ�Ǩ���뱳Ӧ����ͬ���õĽ�������ڣӽṹ�У��������������ͭ�߷ֱ�����������ܴ�ĺ��ӿ飨�������̣����������̣������������Ҳ�ͭ�ߵ������ˣ���ͭ���뺸�ӿ����������ı�Ӧ�����Ժ��Բ��ƣ���ˣӽṹ�ܹ���ֱ�ӵط�ӳ�ɵ�Ǩ��������������ˡ�

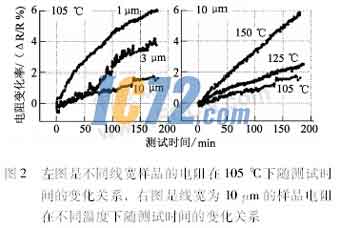

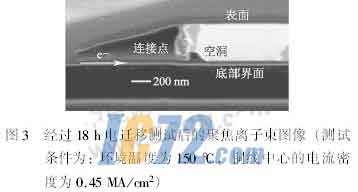

�ڲ�ͬ���������£��ӽṹ��Ʒ�ĵ��������ʱ����仯�Ĺ�ϵ������ͼ����ʾ����ͼ�п��Կ�������ʹ�����û����������£��������¶�Ϊ�������棬ͭ�����ĵĵ����ܶ�Ϊ��.�����ͣ��������������������Сʱ���Ϳ�����������Ʒ�й۲쵽���Եĵ��������¶�Խ�ߣ�����ı仯Խ��ͭ��Խ��������ı仯��Խ�����ԡ����ֻ���ǵ�Ǩ��ЧӦ�����ݹ۲쵽�ĵ���仯�����Լ�����ۣ���-�������ڣ����̣�����ͭ���У�ԭ�ӵ�ƽ��Ư������Ϊ����������裬��ɢ������Ϊ��.����������������֣����ڿ���Ϊ���ͣ��̣���ͭ���У�ƽ��Ư�����ʷֱ�Ϊ�����ͣ���������衣ͬʱ���۽����������ƣɣ£�ͼ������ر����ɵ�Ǩ������Ŀն����ȳ�����ͭ����ɢ�赲����洦��ͼ����������Ҫ���ŵ��߳��ȷ���Ѹ�ٳ�����Щʵ�����������ڣӽṹ������ͭ����ɢ�赲�������������˷dz�������ԭ�ӵ�ƽ��ƫ������Զ������ͬ�ߴ�Ĵ�ͳ�£����ṹ�ۣ����ݡ�

�� ����������

��������ͨ������Ԫ���������������������ʵ������

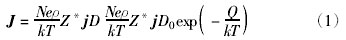

�ֲ�ԭ��ͨ�������ɵ�Ǩ�������������ģ������ɣΣ��������ţ��������̵�������ʾΪ�ۣ���

ʽ�У��δ���ԭ���ܶȣ����ӵ�ɣ壻��������ѣ��������������룻�¶ȣԣ����DZ��۵�Ч���������Ϊ�ֲ������ܶȣ��Ĵ���ԭ����ɢϵ�������ģ�������ɢ���ӣ�������ɢ�����ܡ�

��ά�ṹ��ͭ����ɢ�赲����Ӵ��γɵײ�����Ͳ�ǽ���棬���У�����ͭ����ɢ�赲��ײ�����ľֲ�ԭ��ͨ���ʣɣ���ɱ�ʾΪ�ۣ�-����

ʽ�У��±�ɴ������棻�±������ײ�����ɣ�������ײ����洦�ĵ����ܶȣ��ģ��ǽ���Ŀ��ȣ�����ͭ�ߵĺ�ȣ��ģɣ��������ͨ���ײ��������˵�ԭ��ռ���б�����ԭ�ӵı����ۣ��ݡ�

Ϊ���������ȡ�ʣ���|�ʣ�|��|�ʣɣ��⣨�꣰���ԣ���|��Ϊ����ԭ��ͨ���ĵ�λ�����У꣰�ǣã������ģ�û�е���ӵ�������ĵ����ܶȣ��ԣ��dz�ʼ�¶ȡ�����|��|��|��ɣ���|��|�꣰|�ͦ��ԣ��ԣ��ԣ�����ô�����ԣ����ԣ�ʱ�����ɹ�ʽ�������ͣ������õ�

����ײ�������ɢ����ľֲ�ԭ��ͨ��ɢ�ȣ��ʣ��ɣ��⣬����Ը�����ʽ�ɵ����ݶȣ��꣯�ɣ�����¶��ݶȣԣ������õ��ۣ�����

������ȡ���ʣ��������Ϊԭ��ͨ��ɢ�ȵĵ�λ����ʽ�����������˾ֲ������ܶȷֲ����¶ȷֲ���ԭ��ͨ��ɢ�ȵĹ��ס�

��Ǩ������������������ֲܾ��������¶���������Ȼ����ֱ�Ӳ��������ܶȺ��¶ȵķֲ��Ƿdz����ѵġ����˵��ǣ���ά���ȵ��������Ԫ�����ܹ�ģ�������ϵͳ�ڲ��ĵ���ӵ�����¶ȷֲ��������ܶȷֲ��ļ���ֻ�������̬�������ɣ�Ȼ���¶ȷֲ��������ȴ������ܵIJ�ͬ�������仯��������ѧ����Ҫ���ӵöࡣ������ʵ����Ʒ�Ʊ������в��ɱ���ش��ڲ�ͬ�̶ȵľֲ���Ⱦ�Լ���ͬ����֮��ĸ��Ż�Ӵ���������Щ���ػ�������Ӱ���ȴ������ܣ��Ӷ����¼�ʹ����ȫ��ͬ�IJ��������£�ÿ����Ʒ�ڲ����¶ȷֲ������ܲ�ͬ�����ּ��˵�����ǣ�����״���£��ȴӲ��Խṹ�������ĵ�Ч�ʷdz��ߣ��������ڲ��Խṹ�ڲ������ܳ����κ����Եľֲ��¶ȱ仯�����������������ȵ�

Ӱ����Ժ��ԣ���֮�෴�������������Խṹ����Χ���ϼ���ȴ���ϵ���dz�С����������������������ã��ߵģ£����������Ľ����ȣ������ڣã����������൱����¶��ݶȡ�ʵ��״�����������ּ������֮�䡣

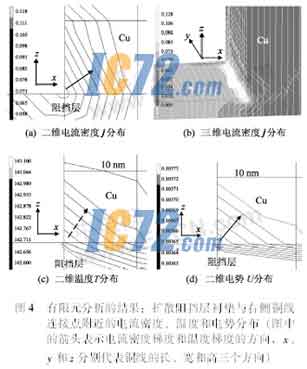

��ɢ�赲��ĵ棨�£̣����Ҳ�ͭ�����ӵ㸽���ĵ������¶ȷֲ���ͼ����ʾ��ģ��������õ�����Ϊ�����Ӵӣ��������ģ£����룱�̣�����������

������ͭ�ߣ�ͭ�����ĵĵ����ܶȵ��ڣ�.���ͣ���������������¶�Ϊ�������棬ȡͭ����ɢ�赲�������Ȧģɡ֣�.������ۣ��ݡ��������ּ��������ͭ���������ӵ���ࣰ.�������������Ԫ��������ڱ������г�����Ȼ�ֲ������ܶ���ͭ������Ϊ��.���ͣ�����������������ڵ���ӵ��ЧӦ���ӱ����ڣ��п��Կ������ھ������ӵ㣰.���������ߴ��.���ͣ����������������Լ����������ʹ�þֲ��ĵ����ܶ��ݶȸߴ.���ͣ����������������������ݹ�ʽ���������������Թ�������������е���ͭ����ɢ�赲��ײ��������˵ľֲ�ԭ��ͨ����ͨ��ɢ�ȡ���ʹ�������¶��ݶȵ����ã�����ӵ��ЧӦҲ���Խ����ӵ㸽����ԭ��ͨ����������

�ӱ��������Կ������������ӵ㸽���ĵ��Ӽ�������ͭ����ɢ�赲��ײ�����������ͭ����ɢ�赲��ײ����洦�ľֲ�ԭ��ͨ��Զ����ͭ���ϱ��洦��ԭ��ͨ������.���ʣ������ټ���ͭ����ɢ�赲���ǽ����Ĺ��ף���ͽ�����Ϊʲô�ڸò��Խṹ��ͭ����ɢ�赲������DZ�ͭ���ϱ������Ч�Ŀ���ԭ������ͨ�������ڽϿ���ͭ�ߣ������뿼���ڵ���ӵ�������ؾ���������ˣ����ڣӽṹ�в�̫���ܼ���

���������۽����ȵ�Ӱ�죬���������Ľ�������Ҫ�����ڣӽṹ�еģ£�����������������ڣ��У��������££����Ҳ�ͭ�����ӵ���¶�Լ���ߣ����ˣ��ֲ��¶��ݶȸߴ���ˣ��̣����ֲ�ԭ��ͨ����ͨ��ɢ�ȶ�ԼΪ����״��ʱ�ģ�������ˣ��ڽ������ּ������֮���ʵ��״���£�ȡ���ڲ��Խṹ���ȴ���Ч�ʵIJ�ͬ�������Ȼ�ʹԭ��ͨ����ͨ��ɢ����������״��ʱ�ģ��������������ӵ��ЧӦ��ȣ������ȼ���������¶��ݶȶ������������ʵ�Ӱ�������ġ��ڿն��γɲ�����Ĺ����У�����ӵ��ЧӦ�ͽ�����ͬʱ�����ò����ǿ�����յ�������ͭ����ɢ�赲����淢���������������ˡ�����ʵ��ͷ�������������߶Ⱦ��ĵ���ӵ���ܹ�Ӱ�����ԭ������ͨ����Ч�ʣ��ڳߴ��С���Ƚ�����ϵͳ�У������������ʹ�����ɿ�������������ء�

�� ��

��֮�������о���һ��ר����ƵIJ��Խṹ�е���ӵ��ЧӦ�Ե�Ǩ�Ƶ�Ӱ�졣����Ԫ�����õ��ĵ������¶ȷֲ����������ڵ���ӵ��ЧӦ�����û��¶������ض�ͨ�����˵ľֲ�ԭ��ͨ������������δ���Ļ���ϵͳ�У���Ϊ�����߳ߴ�ļ�����С����Ӧ�ĵ����ܶȾ�������������Ԥ�ڵ���ӵ��ЧӦ���������������Ե�Ǩ�ƺ��������˵�Ӱ�콫���ܺ��ԡ� |