ժҪ�������˻��ڵ�ɲ����ɱ��������EPLD����VHDL�������ʵ�ֵ�TMS320C5402��SDRAM�Ľӿڵ�·��

�ؼ��ʣ���ɲ����ɱ�������� �����źŴ����� ͬ����̬����洢�� �ӿڵ�· VHDL

�ڶ�ý��Ӧ���У���ý����Ϣ��������Ƶ���ݺ���Ƶ���ݣ������ֻ�����Ƶ���ݺ���Ƶ���ݵ��������Ƿdz��Ӵ�ġ�Ϊ���ܹ���ʱ�����ش���ǰ�˲ɼ������ݣ�һ��ϵͳ�����ø���DSP�ʹ���������洢�����һ���洢��һ��ѡ��ͬ����̬����洢��(SDRAM)������DSP����ֱ����SDRAM�ӿڣ�����SDRAM����ʱ��Ƚϸ��ӣ���˱��Ľ���������õ�ɲ����ɱ��������ʵ��TMS320C5402��SDRAM�Ľӿڡ�

1SDRAM�ṹ������

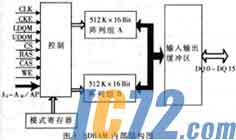

SDRAM��һ�־���ͬ���ӿڵĸ��ٶ�̬����洢��������ѡ�õ���Samsung��˾512K��16Bit��2���KM416S1120D��SDRAM��ͬ���ӿں��ڲ���ˮ�߽ṹ�����洢�ⲿ�������ݣ����ڲ��ṹ��ͼ��ͼ1��ʾ��

SDRAM������������������ϵͳʱ��CLK������ͬ���������������ź�RAS��CAS��WE��ϲ���SDRAM�������������Ŀ����������1��ʾ��

�ھ������SDRAMʱ�����ȱ���ͨ��MRS��������ģʽ�Ĵ������Ա�ȷ��SDRAM���е�ַ�ӳ١�ͻ�����͡�ͻ�����ȵȹ���ģʽ����ͨ��ACT������Ӧ��ַ���飬ͬʱ�����е�ַ��Ȼ��ͨ��RD��WR���������е�ַ������Ӧ���ݶ�����д���Ӧ�ĵ�ַ��������ɺ���PCH�����BT������ֹ����д��������û�в�����ʱ��ÿ32ms������ARF����ˢ������(2048��)����ֹ���ݶ�ʧ��

2FLEX10Kϵ��EPLD�ص�

FLEX10Kϵ��EPLD�ǹ�ҵ���һ��Ƕ��ʽ�Ŀɱ������������Ҫ��Ƕ��ʽ���п�(EAB)�������п�(LAB)�����ٲ���ͨ��(FastTrack)��I/O��Ԫ��ɣ����������ص㣺

(1)Ƭ�ϼ�����ʵ�ֺ꺯����Ƕ��ʽ���к�ʵ����ͨ�����������У�

(2)����10000��250000�������ţ�

(3)֧�ֶ��ѹI/O�ӿڣ�����PCI���߹涨���ڴ�JTAG�߽�ɨ����Ե�·��

(4)�ɿ���Ԥ��������ʱ�Ŀ���ͨ������ʽ���߽ṹ��

(5)���6��ȫ��ʱ���źź�4��ȫ������źţ�

(6)��ǿ���ܵ�I/O���ţ�ÿ�����Ŷ���һ����������̬���ʹ�ܿ��ƣ�����©����·ѡ��

3TMS320C5402��SDRAM�ӿ����

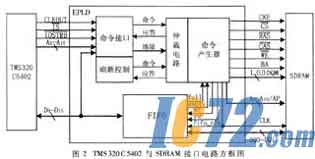

TMS320C5402��SDRAM�ӿڵ�·����ͼ��ͼ2��ʾ��

����ӿ���Ҫ��DSP������SDRAM�ĵ�ַ�Ͳ���������н���(����������1)��ˢ�¿�����Ҫ��SDRAM����ˢ�½��м�ʱ��ȷ��32msˢ��2048�����ݣ��ٲõ�·��Ҫ�Զ�д�����ˢ����������ٲã��ž�ͬʱ��������ֹ���ݶ�ʧ�������������Ҫ������������SDRAM�ĸ���ʱ�����SDRAM�Ķ���д��ˢ�£�ͬʱ����FIFO�Ķ���д������FIFO��DSP��SDRAM֮�������ͨ�������Ϊ256���������dz������SDRAM��ͻ����д���ܣ����ϵͳ�ٶȣ�ͬʱ��DSP������ơ�

3.1����ӿں�ˢ�¿��Ƶ�·���

����ӿڵ�·��Ҫ������Ĵ�����������������SDRAM���е�ַ��������ģʽ�Ĵ�����ɡ���������Ĵ���ӳ��ΪDSP��I/O�ռ�0001H��SDRAM�к��е�ַ�������ֱ�ӳ��ΪDSP��I/O�ռ�0002H��0003H��ģʽ�Ĵ���ӳ��ΪDSP��I/O�ռ�0004H��������������I/O��ַ�������2����3��ʾ��

DSPÿ�ν��ж���д����ʱ����������I/O�ռ�0002H��0003Hд��SDRAM�к��е�ַ��Ȼ����I/O�ռ�0001Hд��������������������������Ĵ����������������ٲõ�·������д����

ˢ�¿��Ƶ�·��Ҫ��1562���������ɡ�����TMS320C5402ʱ��Ƶ��Ϊ100MHz��SDRAMҪ����32ms֮��ˢ��2048�����ݣ���˸ü���������ֵӦС�ڣ�32ms/2048/0.01��s��1562.5��������������1562��ʱ��ˢ�¿��Ƶ�·���ٲõ�·����ˢ��Ҫ��

3.2�ٲõ�·��������������

�ٲõ�·��������ӿ�ģ�����������ˢ�¿���ģ���ˢ���������ʵ��Ŀ����������ˢ����������ȼ��ϸߡ�������DSP�����������ˢ�¿���ģ���ˢ������ͬʱ����ʱ��������ִ��ˢ�²�����Ȼ��ִ������DSP������������Է�ֹSDRAM�����ݶ�ʧ���ɴ˿�֪���ٲõ�·ʵ������һ�����ȼ�ѡ������

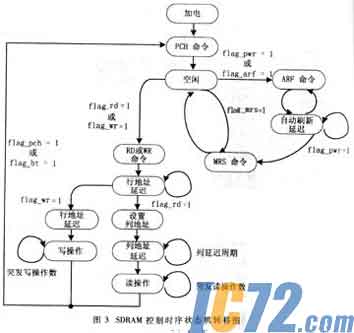

�����������Ҫ����SDRAM����д��ˢ�µĿ���ʱ��(����ʱ��ɼ��ο�����1)�Լ�FIFO�Ķ�д�����źţ����Զ�SDRAM���и��ֲ�������ʵ������һ��Mealy��״̬��������VHDL���Կ��Ժܷ����ʵ�֣���״̬ת��ͼ��ͼ3��ʾ��

3.3FIFO���

FIFO��·��DSP��SDRAM�������ݽ�����ͨ����ͨ��FIFO��·���Ժܺõ�ʵ��DSP��SDRAM�Ķ�д��FIFO��·��ӳ��ΪDSP��I/O�ռ�0000H(����2)��DSP��SDRAM��ÿ�ζ���д������DSP��I/O�ռ�0000H����������DSP������ơ�����FLEX10Kϵ��EPLD�ڲ�Ƕ��ʽ���п�(EAB)�Ͳ�����ģ���(LPM)�����Ժܿ�ع����256��16��FIFO��·��FIFO����ƱȽϼ�VHDL������������(ע���ڳ���ʼ������LPM��)��

FIFO256CSFIFO

GENERICMAPLPM_WIDTH����16��LPM_NUM��

WORDS����256��

PORTMAPdata������LPM_WIDTH-1DOWNTO0��

wreq����wr��rreq����rd��

clock����clk50��clockx2����clk100��

clr����clr��sclr����sclr��

empty����empty��full����full��

q����q��LPM_WIDTH-1DOWNTO0��

����EPLDͨ�á����ټ��������ص㣬��˾��кܺõ�ʵ��Ӧ��ǰ����������������Ҫ���������ٻ���洢���Ķ�ý��Ӧ�á� |