ժҪ���Ƚ������˺��������ݴ洢���к������TMR���ֵ��;���ϵͳ��ԭ����ʵ�������ݿɿ��ԵĹ��ƣ��ڴ˻����������һ�ּ���������ϵͳģʽ������ʵ��Ӧ���и�����Ҫ�л�ģʽ�ľ���ϵͳ��Ʒ�����̽���˸�ϵͳ���ص�����ƣ�����������FPGAʵ�ָ�ϵͳ�Ĺ��̺;��顣

�ؼ��ʣ������ӷ�ת �����롡���ݴ洢�����������롡С����

�ռ��������̫�ջ��������ٵ���Ҫ����֮һ���Ƿ��䡣̫���еĸ��ָ�������(�����������ӡ����ӡ������ӡ������ӵ�)���кܸߵĶ��ܣ�ͨ��ʱ���ܻ�Ӱ��뵼���·����״̬�������뵼�������������������������ӶԵ����������ܲ�����Ӱ���֮Ϊ������ЧӦ�����У����´洢������'0'��'1'֮�䷢���仯�ĵ����ӷ�ת(SEU)�����ر��ܵ���ע��

С���ǵ��з�˼·�����ڶ̡��ɱ��͡������£���˴��������г�������ȡ�õ���ҵ��������������Щ�������и��ܶȡ����ġ��ͳɱ�����չ��ǿ���ص㣬��ͨ��û�о����ϸ�Ŀ�������ԣ�Ҳû�в������ƵĿ����乤�ա����С���ǵĿ�����������Ҫ��ȡ�ۺϴ�ʩ����������������������ȣ����Ծ������ݴ洢����ͨ�����ñ��롢���ݵȷ���������Ϣ������Ӧ��SEU�����������洢��������ϣ�ʵ���������/�������ܵĵ�·����С�������ؼ����ϵͳ�����ݲ�����;���ģ��(Error Detection And Correction, EDAC)��

1 ��������TMR�����Ƚ�

��С���ǵ�EDACģ������У��������ñ���(��Ҫ�Ǻ�����)�����������о�(Triple Modular Redundancy, TMR) �ķ���������ֱ�˵�������ַ��������ԱȽϡ�

1.1 ���Է�����

������������ͨ�ź����ݴ洢����㷺ʹ�õļ��/����������

���Է�������ʹ�úܹ㷺�IJ�����Ʊ��룬����Ϣλ�ͼලλ�Ĺ�����һ�����Դ����������ʾ�� (n,k)���Է�����ı�����ǽ�����m(m��n-k)����������λ�ķ���ʽ���ɵķ����飬���ɴ����Է�����ת��Ϊk��n�����ɾ���G������ʱ����Ϣλ����(kά)�������ɾ���G�����õ���������[Cn-1��C0]����ʽ(1)��

[Cn-1,Cn-2,����Cn-k,Cm-1,��,C0]��[Cn-1,Cn-2,��,Cn-k]��Gk��n (1)

��ʽ(1)��ʾ�ķ���������λ�任�����Եõ���ʽ(2)��ʾ����ʽ���ȳ�Ϊ�ල������ʱͨ���ල����H���������������C�ij˻����-У����S���ж��Ƿ����������������������C����H��õ�һ������������ʾû�г����������ʾ�����ڴ洢֮�����˱仯�����д�������

S��Hm��n��[Cn-1,��,C0]T (2)

��������ijλ(��һλ)��������ʱ����õ�Ψһ�ķ���У����S������������ֻ�����ֳ���λ�õ�ͼ���йأ���������C�ء�

���������ܾ���������������Է����롣���Ӧ��G����Ϊ���������ɾ������ֱ����£���������ܳ���2m-1λ����Ϣλ������2m-m-1λ����(2m-1��2m-m-1)�����롣(2m-1��2m-m-1)�������DZ���Ч����ߵľ��������Է����롣�����ǵ�һ�������洢ϵͳ���ֽ�Ϊ��λ����2m-m-1ͨ������8�ı��������ԶԺ����������չ���Եõ�(12,8)��(22,16)�ȷ�����뷽������Щ��������һЩ�µ��ص㣬����һ��(22,16)����������������������˫������������SEC-DED��[2]��������ͨ����ѡ���õ���Ѽල����H��ʹ�������·��Ϊ�����١�

1.2 TMR

TMR��ԭ���ǽ�ͬһ����Ϣ���������������洢�ռ��С���ȡ��ʱ��Ƚ��������ݣ��������ȫ��ͬ����ȡ����һ�µ�ֵΪ��ֵ����CPUͨ���������ڴ�д������ (�ף���Ч) ʱ��ÿһ��������ͨ����̬��ͬʱд��������Ӧ�ı��ش洢��Ԫ�С����������ڴ��������� (RD��Ч) ʱ������ͬʱ�洢�����ݵ���Ƚ������Ƚ���������ǰ����������������ݼ��Ƿ���2/3�о��ı�ǡ���������Ҫ��·���ؿ��Խ��������ݻ���ÿ�����رȽ�����2/3�о��������������ϣ����߿ɹ������о��ɿ���ʱʹ�á�

1.3 ���ַ����ıȽ�

�Ӵ洢�ռ�ľ��Դ�С�Ƕȿ��ǣ����뷽���������о�����Ҫ��ʡ�����Ĵ洢�ռ䡣�������(22,16)�����룬ÿ1MB��Ч�ڴ���Ҫʵ�������ڴ�1.375MB��������TMR��������Ҫ3MBʵ�������ڴ档

��ϵͳ�ľ����ɿ��ԽǶȿ��ǣ����ȼٶ��ڴ�ĵ����ӷ�ת�¼�(SEU)��������������ַ��ʱ�䶼�Ǿ��ȷֲ��ġ���ÿһ�����ڴ浥Ԫ�ڵ�λʱ���ڷ��������ӷ�ת�ĸ���Ϊ�ҡ���ÿm�����ڴ�ṹ��v���ط���SEU�ĸ���Ϊ��

��(v,m)��Cvm��v(1-��)m-v

����(22,16)�����뷽�����Ծ���ÿ22�����ڴ��е�Ԫ�еĵ����ش�����һ��22���ر����¼��������SEU�Լ�ֻ��һ���ط����ӣţյĸ��ʺͣ���Ϊ�����ڴ浥Ԫ�Ŀɿ��ԡ���ˣ�ÿ22���ص��к������ڴ浥Ԫ�ɿ���Ϊ:

����ham����(0,22)����(1,22)��(1-��)22+22��(1����)21

ÿ22�����е�Ԫ����Ч������16λ����2���ֽڡ��ʶ�����Ч��СΪN�ֽڵĺ������ڴ�ϵͳ����N/2���е�Ԫ���ɡ���ɿ���Ϊ:

��ham������hamN/2��[(1-��)22+22��(1-��)21]N/2

�����ڲ���TMR��һ��3���ص��ڴ�ṹ���ɿ���Ϊ:

����TMR����(0,3)+��(1,3)��(1-��)3+3��(1-��)2

����һ����Ч��СΪN�ֽڵ�TMR�ڴ�ϵͳ����8N��3���ؽṹ��ɣ��ɿ���Ϊ��

��TMR������TMR8N��[(1-��)3+3��(1-��)2]8N

��ʵ�ʺ���Ӧ���У�ͨ��10-9���ң�1010bit-1��s-1��ȡN��4��106(��4���ֽ�)����1�����˦�ȡ��ֵͬʱ�����(1-��)�Ľ��Ƽ����������в����֮�Ȧӣ�(1-��ham)/(1-��TMR)��

��������������ǰ��������Χ�ڣ�����������IJ����Լ��TMR��5�������ң�����ϵͳ�IJ���ʶ���ҵ�ƽ�����Ƴ����ȡ��ɼ���ʹ��ȡ�ڴ�������跨���ͦ��������ϵͳ�ɿ��Ե���Ҫ��ʩ��

ϵͳ��ʱ�������ǿ��ǵ���һ���ؼ����ء��������ڸߴXʮ�յ��ڴ������ϣ�����������Ϊ�����ĺ����뷽�������൱�ľ����ԡ���TMR����ֻ����м�2/3�о���ͨ������ʤ�ο��̵��ڴ����ʱ��Ҫ��

2 �ɱ䷽������

�������ȽϿ��Կ��������ַ����������ƣ��ʺ��ڲ�ͬ�Ļ������������ݰ�ȫ������Ӧ�á������ؼ������ͨ����ҲҪ�����ݴ洢������һ���̶ȵ�����ԡ����ۺ��������ַ����Ļ����ϣ����Ŀǰ���ٷ�չ���ֳ��ɱ����������(FPGA)�����������һ�ֿ��Ը�����Ҫ���߸ı����ã��ֱ�ʵ����������EDAC���������ݴ洢��������

2.1 �ɱ��ڴ�����

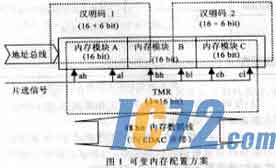

ǰ������EDAC���������ڴ�������Dz�ͬ�ġ�(22,16)������һ�����16bit+8bit���ڴ�оƬ����ʵ�֡���TMR�����3��16bit��оƬʵ�֡���Ҫ֧�����ַ���������Ϊ�洢�����һ���ر���ڴ����÷�ʽ������ģʽ�ɱ�Ļ����ؼ���ͼ1Ϊ�ɱ��ڴ����÷�����

������ݴ洢ϵͳ����3��λ��ͬһ����ַ�����ϵ�16 bit�ڴ�ģ����ɡ�ÿ���ڴ�ģ�黹���Ե���Ƭѡ����ֽڻ���ֽڡ�����ͨ��Ƭѡ�ź�ah��al��bh��bl��ch��cl�Ŀ��ƣ�ʵ������6������Ϊ8bit���ڴ�ģ����Ե������ʡ�48bit(3��16bit)��������ȫ������EDAC����ģ�顣��ϵͳ������TMRģʽʱ��ah��al��bh��bl��ch��cl����ͬ��Ƭѡ�ź�����������������TMR��Ҫ��һ��3��16bit�����ڴ�ռ䡣��ϵͳ�����ں�����ģʽʱ��ah,al��bhһ�飬bl��ch��clһ�飬�ֱ���ͬ��Ƭѡ�ź�����������������������16+8bit�洢�ռ䡣����(22��16)�����룬ÿһ���ռ�ʵ��ʹ��16+6bit�������������£���ַ�ռ��TMRģʽ������һ�������⣬ϵͳ�����Թ������������ģʽ�¡���ʱ��ah��alһ�飬bh��blһ�飬ch��clһ�飬�ֱ���ͬ��Ƭѡ�ź�����������������������16bit �洢�ռ䡣���������µ��ڴ��ַ�ռ��TMRģʽ����������������Щ����ģʽ�У�Ƭѡ�ĵ�ַ���붼��EDAC����ģ������ɡ�

2.2 �ɱ����������ϵͳ�ṹ

һ�����������ڴ����÷�����ģʽ�ɱ����ݴ洢ϵͳ��һ��RAMоƬ����Ϊ�ڴ����塣�ɱ����������ϵͳ�ṹ��ͼ2�������ڴ�ģ���⣬��Ӧ�ð������¹���ģ�飺

(1)TMR��дȡ�о�ģ�顣TMR����ģʽ�£���ɶ�ȡ��д������е������о������ݷ����������ģ��ľ�������Ѿ���1.2������ϸ�����ˡ�

(2)���������ģ�顣�����빤��ģʽ�£������ڴ�д������ʱ��ɱ������㡣

(3)���������ģ�顣�����빤��ģʽ�£��ڴ��ڴ��������ʱ��ɼ���;������㡣(2)��(3)������ģ����㷨ԭ��������1.1���н��ܵķ�����

(4)��ַ��ģ���ģʽ����ģ�顣��ϸ��ֹ���ģʽ��������Ӧ��ģ�鹤���źź���Ӧ���ڴ�Ƭѡ�źţ���ɸ��ӵ�ַ���룬��ȷ����RAM���ݣ�ʵ�ֶ������ڴ�ķ��������

Ϊ�ˣ�����FPGA�����EDACר��оƬ��ʵ������Щģ�飬�����ڴ�ģ�������ӣ�����������ľ���ģʽ�ɱ�����ݴ洢ϵͳ�������ϵͳ�У����д�����ʱ����������ͨ��EDAC-FPGA�Ժ��ʵ���ʽ����RAMоƬ�飻��ɶ�������ʱ��EDAC-FPGA��RAMоƬ������ݶ���������(������о�)�����ϵͳ�����ϡ�

2.3 �ɱ䷽�����õ��ص�

���ݲ�ͬ����ľ����ص㣬�������ݴ���ϵͳ�����ڴ��������������Ҫ��Ҳ������ͬ�������ڴ����ϴ�ָ���������������״̬ʱ��Ҫ�������кܸߵĿɿ��ԣ��������ڴ�������û���ر��Ҫ���ڴ���ijЩ��;��ң��ͼ������ʱ����Ҫ�ϴ���ڴ����������Կɿ��Ե�Ҫ������Ӧ�ϵ͡���ͳ���ڴ�������Ӳ����ɺ���Ѹ��ġ������ȫ������������Ҳ��ʵ���൱�̶ȵ�����ԣ���������������CPU�Ĵ������㸺��ʹ�������������Щ�ò���ʧ��

�ɱ�����������������Ƶ��ڴ�ϵͳ��ȣ�������Ӳ����������һ��FPGA����������������ȫ���ġ����ң����������ݴ���ϵͳ����������������Ҫʹ��FPGA�ij��ϣ����FPGA��������ȫ����ͨ���ۺ���ƣ����ϵ���������������֮���FPGA֮�С�

���⣬�����ڶ�������ģʽ��һ���������ڴ������������һ�µģ���������֮����������ϣ����ؼ����롢���ݶ����ڸö��ڴ�֮�У��Ϳ���ʵ���ڲ��������������ϵͳ��ǰ���¸����ڴ�����������ã����ģʽ�л�����֤ijЩ�ؼ������жϡ�

��֮������FPGAʵ�ֵ�Ӳ���ɱ����÷�������С��Ӳ�����������ۣ��ṩ�������ڴ���������ԣ���������˸��������ҽ�Լ��RAM��Ӳ����Դ���ġ�

3 Ӳ��ʵ��

3.1 FPGA�ı����ʵ��

ͨ����Ŀǰ�㷺ʹ�õ�FPGA�����ķ����ͱȽϣ�ѡ��ʹ���˾��нϸ��Լ۱ȵ�Xilinx Spartanϵ��FPGA����ԭ�����顣��ϵ�в�Ʒ������3.3V��Դ��Ӧ����5V I/O������״̬����������ٶȵ��ص㡣Ϊ����FPGA�����ܵ����ӷ�תЧӦӰ�죬��ʵ�ʵĺ��������У������û�����˿������Actel��˾��FPGA��Ʒ��

��Ӧ�þ��к�ǿ��ģ���ԣ����߲����˱�VHDL�����������ṹ������ͬʱΪ��������ֲ�ṩ�˷��㡣ģ��Ļ��ֻ���ͼ2��˼�룬��ͬʱ���ǵ�VHDLģ���ϰ��Ҫ���Լ�ʵ���еĿ��ۺ��Ժͷ����ԡ��ھ����VHDLʵ�ֹ����У���ϵͳ������VHDLʵ��(entity)ģ����ɣ�

(1)3bitcomp:TMR�ı�������Ԫ��ʵ�ֱ��ؼ�����Ϣ���ݺ;����о���

(2)tmr:TMR����ģ�飬����16��3bitcompʵ��(��Ӧ16λ����)��

(3)hamming�����������/��������ģ�飻

(4)hammeminf:hammingʵ���22λ�ڴ�ӿ���48λ�ڴ�������֮���ת���ӿڣ�

(5)eadc:��߲�ʵ�壬��������4��ʵ��ͱ���������ơ����ݽӿڵȡ�

���ǵĹ�ϵ��ͼ3��ʾ��

ϵͳʹ����Active-HDL�������й��ܷ��棬�ۺ���ʵ�ֶ�ʹ����Xilinx�ṩ��Foundationϵ����������RTL�ۺϹ��������ɵĵ�·ͼ��ע���ʹ��VHDL����˫����̬��ʱ���뱣֤���������¶�ָ����ȷ��״̬��������RTL�ۺϺ������·����ʵ��˫����̬�Ĺ��ܡ�

3.2 ʱ������

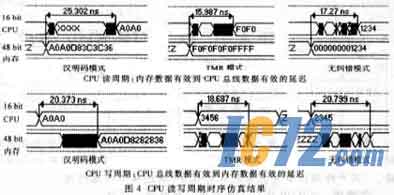

ʱ���������ڴ�ϵͳ�Ĺؼ�ָ�ֱ꣬�Ӿ������ڴ�ϵͳ�Ĺ���Ƶ�ʺ�����OBCϵͳ�������ٶȡ����ڲ�����FPGA�������Ը��ڴ�ϵͳ��ʱ�����Է�������ͨ��FPGAʵ�ֺ��ʱ������������о�����FPGAʵ�ֹ����У�ͨ��Լ���������Ż������������Զ�������ɹ��̡����������Ż�����Xilinx XCS30XL��ʵ�ֺ�ķ�������ͼ4��ʾ�����Կ�����TMRģʽȷʵӵ�нϺõ�ʱ�����ԣ���ʱ�϶̡�����������Ϊ������ģʽ������ʵ�ֹ�����Ϊ���Ż�����ģ����������ʱ�ϵ�������

ͨ���������۷�����ϵͳ��ƺ�Ӳ��ʵ�飬���Կ�����ͨ��FPGAʵ�ֵĿɱ�ģʽ�������ݴ洢������ϵͳ���й������ơ���Ӧ��ǿ��ʹ�����㡢Ӳ����·���ص㡣����FPGA�����Ĺ㷺ʹ�ã�������Ƴ����ܸ�ǿ��ʹ�ø������ר��ϵͳ���Գ������ռ������������Ҫ�� |