1 引言

CMOS图像传感器是近年来发展十分迅速的一种新型固态图像传感器。它将图像传感器阵列、时序控制电路、信号处理电路、A/D转换电路以及接口电路等集成在一体,使其具有体积小、功耗低、集成度高、控制简单、成本低等优点,因此在数字图像采集等方面得到广泛应用。

本文在分析了PB-1024 CMOS APS图像传感器的工作原理和时序要求的基础上,设计了简单合理的时序控制电路。该设计采用复杂可编程逻辑器件(CPLD)作为硬件设计平台,VHDL语言为设计描述方式,并通过Xilinx公司的Foundation软件进行了系统仿真。

2 PB-1024 CMOS APS图像传感器

2.1 特性、结构及原理

PB-10244是美国Photobit公司生产的百万像素CMOS APS图像传感器。其图像分辨率为1024H×1024V,像元尺寸10.0μm×10.0 μm,在主时钟频率为66 MHz时,最大数据传输速率为528 Mbit/s,对应的采样速率为500帧/s,且片内集成了8位A/D转换器。

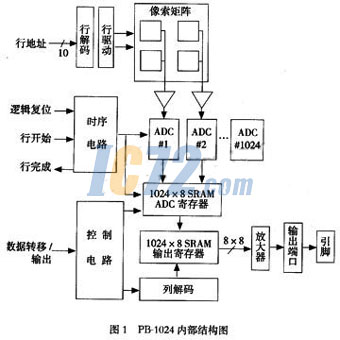

PB-1024 CMOS APS图像传感器将像素矩阵、A/D转换电路及时序控制电路等集成在一起,其内部结构由图1所示的几个功能模块组成。当光照射到像素阵列上时发生光电效应,在像素单元内产生相应的电荷。在时序电路的控制下,行选择逻辑单元根据行地址总线选通相应的行像素单元,行像素单元内的图像信号通过各自所在的列信号总线,传输到对应的模拟信号处理单元和A/D转换器,转换后的数字信号首先被存储在A/D转换寄存器中,然后在输出控制电路的作用下,转移到输出寄存器中,最后8×8位的数字信号经放大后输出。

2.2 时序分析

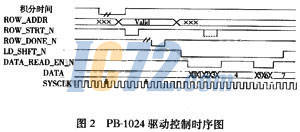

PB-1024 CMOS APS图像传感器所需的时序驱动控制信号主要有:采样开始信号ROW_STRT_N、数据转移信号LD_SHFT_N、数据允许输出信号DATA_READ_EN_N等,其驱动控制时序如图2所示。

在光积分期间,通过10位行地址总线(ROW_ADDR)选通有效的像素行,当采样开始信号有效时(ROW_STRT_N为低电平),开始从有效的像素行中读取模拟信号,经A/D转换后,将数字信号存储在A/D转换寄存器中。完成以后,图像传感器送出数据读取完成信号(ROW_DONE_N为低电平)给驱动控制器,驱动控制器发出数据转移信号(LD_SHFT_N为低电平),此时数字信号从A/D转换寄存器中转移到输出寄存器中。在数据转移信号有效的一个时钟周期后,数据允许输出信号开始有效(DATA_READ_EN_N为低电平),数据从输出寄存器中输出。

3 时序控制电路的CPLD实现

3.1 复杂可编程逻辑器件

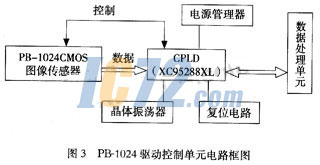

在设计中,由于来自PB-1024图像传感的8×8位数据输出端口要用到64个I/O口、行地址需要10个I/O口、其他控制信号需要45个I/O口,这样共需要119个用户自定义的I/O口。为此选用美国Xilinx公司生产的XC95288XL复杂可编程逻辑器件来实现对PB-1024 CMOS APS图像传感器的驱动控制。XC95288XL共有208个输出端口,其中有168个用户可编程的I/O口,完全可以满足系统设计的需求。基于CPLD的PB-1024 CMOS APS图像传感的驱动控制单元如图3所示。

3.2 驱动电路的VHDL设计

通过对PB-1024 CMOS APS图像传感器的时序分析可见,时序控制电路的设计规模较大、复杂程度较高且速度要求较快,因此为了满足高频帧的时钟要求,设计采用VHDL语言来实现,主要产生PB-1024的输入时钟信号和数据的采集、转移和输出信号。

为保证采集到的图像能够实时地显示在XGA监视器上,系统时钟频率按照XGA监视器的扫描频率75 Hz来确定。由于场消隐期的存在,即每一行的输出信号都会包含一些哑像元,每一场图像的输出也会包含一些哑行,所以在设计时为保证不会采集到消隐电平,使每一个有效像素与每一位有效数据的输出――对应,因此确定一场图像的实际大小为1328×803。这样得到的行频为60.225 kHz,点频为80 MHz,因此用80 MHz的时钟频率作为CPLD内部的全局时钟频率。但由于图像在传输过程中受到低速XGA电缆发送速率75帧/s的限制,所以PB-1024 CMOS APS图像传感的输入时钟频率只能达到10 MHz,这可由一个8分频的计数器完成。

数据的采集、转移和输出的过程为:当全局复位信号RESET=1时,系统停止工作,这时所有计数器清零。当RESET=0时,系统处于采集状态。采集一场图像的过程为:当全局时钟信号VCLK的下降沿来到时,列计数器(HCOUNTB)开始计数,在输出若干个过渡像元后开始有效数据的采集和转移(LD_SHIFT为低电平),在一个全局时钟周期后数据开始允许输出(DATA_READ_EN为低电平),当列计数器计数到1024时,停止数据的转移和输出。当列计数器计数到1327时,行计数器(RSTV-COUNT)加1,列计数器清零,开始下一有效像素行数据的采集、转移和输出。当行计数器计数到768时,完成一帧图像的采集,当行计数器计数到803时,完成一场图像的采集。

3.3 设计验证

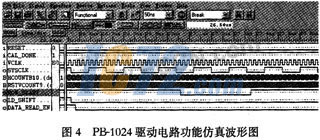

采用Xilinx公司的Foundation软件对时序电路进行仿真,仿真波形如图4所示。通过与图2的比较,可以看出产生的驱动控制信号波形与PB-1024 CMOS APS图像传感器所需时序控制关系基本吻合,能够达到PB-1024 CMOS APS图像传感器的时序要求。

4 结 论

采用CPLD对CMOS APS图像传感器的驱动电路进行设计,使原来复杂的电路设计变成只需一片CPLD芯片就能完成,而且电路成倍简化、体积减小、功耗降低,从而提高了图像传感器的抗干扰能力、可靠性和稳定性。

|