ЫцзХНёЬьФЃЪ§зЊЛЛЦїЕФЪ§ОнзЊЛЛВЩбљЫйЖШНјШыЕНУПУыЧЇезДЮВЩбљ(GSPS)ЃЌЯЕЭГашвЊФмЙЛжЇГжетбљИпЕФзЊЛЛЫйЖШЃЌФЃФтЦїМўБиаыВњЩњКЭЗХДѓИпЦЕаХКХЁЃГ§СЫФЃФтаХКХТЗОЖЭтЃЌЩшМЦЪІашвЊЭъШЋСЫНтВЩбљЪБжгКЭИпБШЬиТЪЪ§ОнЛёШЁЕчТЗЗНУцЁЃаХКХТЗОЖЩшМЦЪІНЋЮЊетСНИіЙиМќЕФЗНУцЬсЙЉНЈвщЗНАИЁЃЯТУцЕФаХЯЂгыашвЊИпадФмADCЕФЯЕЭГНєУмЯрЙиЁЃ

ЪБжгдД

дкИпЫйЪ§ОнзЊЛЛЯЕЭГжавЛИізюживЊЕФзгЯЕЭГЪЧЪБжгдДЃЌетЪЧвђЮЊЪБжгаХКХЕФЪБађзМШЗадПЩвджБНггАЯьADCЕФЖЏЬЌЬиадЁЃЮЊМѕЩйетжжгАЯьЃЌADCЪБжгдДБиаыБэЯжГіЗЧГЃЕЭЕФЪБађЖЖЖЏЛђЯрЮЛдыЩљЁЃШчЙћдкбЁдёЪБжгЕчТЗЪБУЛгаПМТЧЕНетжжвђЫиЃЌЮоТлЧАЖЫФЃФтЕчТЗЛђепADCЕФжЪСПгаЖрИпЃЌЯЕЭГПЩФмБэЯжГіКмВюЕФЖЏЬЌадФмЁЃгХСМЕФЪБжгНЋзмФмдкОЋШЗЕФЪБжгМфИєФкГіЯжЪБжгбиЕФзЊЛЛЁЃЪЕМЪЩЯЃЌЪБжгБпбиЕНДяЕФЪБМфМфЯЖзмЪЧдкВЛЖЯБфЛЏЕФЃЌетжжЪБађЕФВЛШЗЖЈадДјРДЕФНсЙћЪЧВЩбљВЈаЮЕФаХдыБШЛсЪмЕНЪ§ОнзЊЛЛЙ§ГЬЕФгАЯьЁЃ

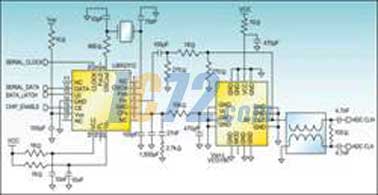

ЭМ1ЃКPLLгыVCOЪБжгЯЕЭГЁЃ

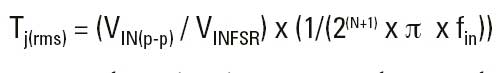

ПЩвдШнШЬЕФзюДѓЪБжгЖЖЖЏЮЊЖЖЖЏдыЩљГЌЙ§СПЛЏдыЩљ(1/2LSB)ЧАЕФЪБжгЖЖЖЏЁЃетПЩвдгУЯТУцЕФЙЋЪНЖЈвхЃК

ШчЙћгХЛЏЪфШыЕчбЙ(VIN)ЪЙжЎЕШгкADCЕФЪфШыЕчбЙЗЖЮЇ(VINFSR)ЃЌФЧУДЖЖЖЏвЊЧѓГЩЮЊADCЗжБцТЪ(NЮЛ)КЭБЛВЩбљЕФЪфШыЦЕТЪ(fin)ЕФвЛИівђзгЁЃ

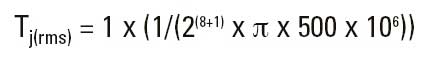

ЖдгкДяЕНФЮПќЫЙЬиЫйТЪ(Ждгк1GSPSзЊЛЛЫйТЪЮЊ500MHz)ЕФЪфШыЦЕТЪЃЌзмЕФЖЖЖЏвЊЧѓЪЧЃК

етИіжЕДњБэСЫРДздЫљгаЖЖЖЏдДЕФзмЖЖЖЏЁЃADCЦїМўБОЩэЕМжТЕФвЛИіЖЖЖЏдДГЦЮЊДАПкЖЖЖЏ(aperturejitter)ЃЌетЪЧЪфШыВЩбљКЭЦїМўЕФБЃГжЕчТЗЯрЙиЕФвЛжжЪБађВЛШЗЖЈадЃЌдкШЗЖЈЪБжгдДдЪаэЕФзюДѓЪБжгЖЖЖЏЪБЃЌашвЊПМТЧетжжВЛШЗЖЈадЁЃ

ЪБжгЕчТЗЖЖЖЏ=(Tj(rms)2-(ADC(ДАПкЖЖЖЏ)2))1/2

вдADC08D1000ЮЊР§ЃЌДАПкЖЖЖЏдкЪ§ОнЪжВсжаИјЖЈЕФжЕЮЊ0.4psЃЌетИіжЕНЋADCЪБжгЕФЖЖЖЏБъзМЯожЦЕН-1.1psЁЃ

ШЛЖјЃЌЕБгУдкЪ§ОнзЊЛЛЯЕЭГжаЪБЃЌНЋеёЕДЦїЕФадФмЪ§ОнгыЙцЗЖвЊЧѓМђЕЅЕиЦЅХфЛђаэВЂВЛзувдЛёЕУЦкЭћЕФНсЙћЁЃетЪЧвђЮЊЦЕТЪЗжСПвВАчбнзХживЊЕФзїгУЁЃвђДЫЃЌгУЦЕЦзЗжЮівЧРДЖдЪБжгаХКХНјааМьВщКмживЊЃЌВЂШЗБЃгыЛљБОЦЕТЪЯрЙиЕФФмСПУЛгадкКмДѓЕФЗЖЮЇФкРЉеЙЁЃбгЩьЕНИќИпЦЕТЪЕФУЋДЬПЩФмКмУїЯдЃЌвВНЋЛсЖдадФмВњЩњжБНгЕФгАЯьЁЃ

ЭМ1ЯдЪОСЫеыЖдADC08D1000ЕФЭЦМіЪБжгЕчТЗЃЌгЩвЛИіЫјЯрЛЗЦїМў(LMX2312)СЌНгЕНПЩБфЕчИабЙПиеёЕДЦї(VCO)зщГЩЁЃPLLКЭVCOЮЌГжДяЕНФЮПќЫЙЬиЪфШыЦЕТЪADC08D1000вЊЧѓЕФаХдыБШ(46dB)ЁЃ

Ъ§ОнЛёШЁ

ЖдаХКХНјааИпЦЕ(1GSPSМАвдЩЯ)ВЩбљвтЮЖзХзЊЛЛЫљВњЩњЕФЪ§зжЪфГіЪ§ОнБиаыДЂДцЦ№РДЃЌЛђепжСЩйПьЫйЕизЊвЦЁЃДІРэУПУыГЌЙ§вЛвкДЮзЊЛЛЕФСНИіЙиМќЮЪЬтЪЧЯЕЭГжаЪ§зжЦїМўжЎМфЕФаХКХЭъећадЃЌвдМАУПИіЪБжгжмЦкЪ§ОнзЊвЦЕФЫйЖШЁЃ

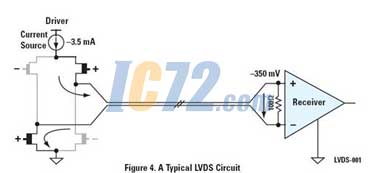

ЮЊЪЙЪ§зжЪфГіаХКХЭъећадзюДѓЛЏЃЌИпЫйADCЪЙгУЕЭЕчбЙВюЗжаХКХ(ЛђепLVDS)ДЋЪф(МћЭМ2)ЁЃ

ЭМ2ЃКЕфаЭЕФLVDSЕчТЗЁЃ

LVDSаХКХДЋЪфЗНЗЈЕФжївЊгХЕуЪЧвдЗЧГЃЕЭЕФЙІТЪдЄЫуЪЕЯжИпЪ§ОнЫйТЪЃЌЖдУПИіНЋЭЈЙ§вЛИіЕчТЗАхЛђепЕчРТДЋЪфЕФЗжРыаХКХВЩгУСНЬѕСЌЯпРДЪЕЯжетжжЕЭЙІКФЁЃУПЬѕЯпЩЯЕФЕчбЙБфЛЏЕФЗНЯђЛЅЯрЯрЗДЃЌЧвгыЯёCMOSЛђепTTLетбљЕФЕЅЖЫаХКХЯрБШаХКХЕФЧПЖШБШНЯаЁ(вЛАуЮЊ350mV)ЁЃетЪЧвђЮЊВюЗжЕчТЗЙЬгаЕФПЙдыЩљФмСІЃЌвђДЫПЩвдЪЙгУЕЭЕчбЙАкЗљаХКХЁЃетЗДЙ§РДвтЮЖзХаХКХЦЕТЪПЩвдИќПьЃЌвђЮЊаХКХЕФЩЯЩ§ЪБМфИќЖЬСЫЁЃ

ЕчТЗАхЩЯДЋЪфВюЗжВЈаЮЕФаХКХЯпгІИУЩшМЦГЩОпга100ІИЕФЬиеїзшПЙ(LVDSБъзМЫљЖЈвхЕФжЕ)ЃЌетаЉЯпдкНгЪеЦїЖЫгУ100ІИЕФЕчзшРДНјааЖЫНгвдгыЯпТЗЦЅХфЁЃЭЈЙ§ЗЂЩфЦїЕчТЗЩЯЕФЕчСїдДдк100ІИЕФЕчзшЩЯСїЙ§3.5mAЕФЕчСїЃЌВњЩњвЛИіаХКХЕчбЙЃЌЬсЙЉ350mVЕФаХКХАкЗљЃЌЙЉНгЪеЕчТЗМьВтЁЃ

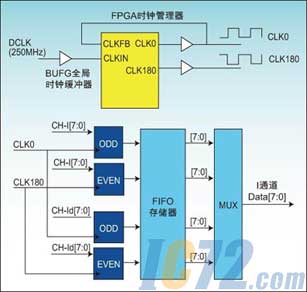

ИпЫйЗЂЫЭЪ§ОнжЛЪЧЮЪЬтЕФвЛАыЃЌЛЙашвЊПМТЧНЋЪ§ОнДцДЂдкДцДЂЦїеѓСажавдзїКѓајДІРэЁЃADCЖдЦфУПИіЭЈЕРЬсЙЉвЛИіНтИДгУЕФЪ§ОнЪфГіЁЃЦїМўВЛЪЧЬсЙЉвЛИідЫаадкЕШгкВЩбљЫйЖШЕФЕЅвЛ8ЮЛзмЯпЃЌЖјЪЧЭЌЪБдкСНИі8ЮЛЪ§ОнзмЯпЩЯЪфГіСНИіСЌајВЩбљЁЃетжжЗНЗЈНЋЪ§ОнЫйТЪМѕАыЃЌЕЋЪЧдіМгСЫЪ§ОнЮЛЪ§ЃЌЖдгквЛИі1GSPSЕФВЩбљЫйТЪЃЌРДздADCЕФзЊЛЛЪ§ОнЪфГіЫйЖШЮЊ500MHzЁЃМДЪЙдкетжжНЕЕЭЕФЫйЖШЯТЃЌДѓЖрЪ§ЗжСЂДцДЂЦїЛђепFPGAФкВПДцДЂЦїдкПЩППЛёШЁетИіЪ§ОнЩЯвВДцдкЮЪЬтЁЃвђДЫЪЙгУDDRЗЧГЃгаРћЃЌвђЮЊDDRдкЪБжгЕФЩЯЩ§КЭЯТНЕбиЖМЪфГіЪ§ОнЁЃОЁЙмЪ§ОнЫйТЪЖдгкDDRаХКХДЋЪфРДЫЕВЛБфЃЌЪБжгЦЕТЪМѕАыЃЌДяЕНИќБугкЙмРэЕФ250MHzЃЌетИіЦЕТЪдкCMOSДцДЂЕчТЗЕФЗЖЮЇФкЁЃдкЪ§ОнФмБЃДцдкДцДЂЦїжЎЧАЃЌашвЊдкЪфШыЕНFPGAЦїМўжаМфВЩгУвЛИіЪ§ОнЫјДцЦїЖдЁЃЕквЛИіЫјДцЦїЪЙгУЭЌВНЪ§ОнЪБжгЃЌЖјЕкЖўИіЫјДцЦїЪЙгУ180ЖШвьЯрЕФЪБжгЃЌЛђепЗДЯђЪ§ОнЪБжг(МћЭМ3)ЁЃ

ЭМ3ЃКFPGAЪ§ОнЛёШЁМмЙЙПђЭМЁЃ

ЮЊМђЛЏетжжЪБжгвЊЧѓЃЌFPGAДјгавЛжжвдPLL(ЫјЯрЛЗ)ЛђепDLL(бгЪБЫјЖЈЛЗ)аЮЪНЪЕЯжЕФЪ§зжЪБжгЙмРэЦїЁЃетаЉЦїМўдЪаэдкФкВПВњЩњЪБжгаХКХЃЌетаЉЪБжгаХКХФмгыЪфШыЪБжгаХКХЫјЖЈЃЌЬсЙЉЯрЮЛбгЪБМфИєЮЊ0ЁЂ90ЁЂ180КЭ270ЖШЁЃетжжЪБжгЙмРэЙІФмдЪаэDDRЪБжгЗНАИЭЈЙ§ЬсЙЉвЛжжОЋШЗЕФ180ЖШвЦЯрЪБжгРДгааЇЙЄзїЁЃетЗДЙ§РДдЪаэЪфШыЪ§ОнгыЯТНЕбиЭЌВНЃЌвдФмПЩППЕиЛёШЁЕНЪ§ОнЫјДцЦїжаЁЃ

дкЫјДцжЎКѓЃЌЪфШыЪ§ОнПЩвдБЛДЋЪфЕНFIFOДцДЂЦїЛђепBlockRAMЁЃдкетРяЃЌЪ§ОнПЩвдвдКмЕЭЕФЫйЖШЧсвзЕиБЛЯЕЭГЮЂПижЦЦїЛёЕУЃЌвдНјааЛёШЁКѓЕФДІРэЁЃ |