AD5532╣дрЩ╫е╧╕дэцХйЖхГобё╨

AVCCё╨дёдБ╧╘╣Г╣Гя╧ё╛╥╤н╖н╙4.75 V║╚5.25 Vё╛ж╩оРDё╞Aв╙╩╩фВдз╨к╧╘╣Гё╩

VDDё╨уЩ╣Гт╢╤кё╛╥╤н╖н╙8 V║╚16.5 Vё╩

VSSё╨╦╨╣Гт╢╤кё╛╣Гя╧╥╤н╖-4.75 V║╚-16.5 Vё╩

DGNDё╨йЩвж╣ьё╛йЩвж╣Гб╥╣д╡н©╪╣Цё╩

DVCCё╨йЩвж╣Гт╢╤кйЩвжпе╨е╧╘╣Г╣Гя╧ё╛╥╤н╖н╙2.7 V║╚5.25 Vё╩

DAC_GNDё╨кЫспDё╞Aв╙╩╩дё©И╣д╡н©╪╣ьё╩

REF_INё╨VOUT0║╚VOUT31╣д╡н©╪йДхК╣Гя╧ё╩

REF_OUTё╨дз╡©╡н©╪йДЁЖ╣Гя╧ё╛лА╧╘3 V╣Гя╧ё╩

VOUTё╨32╦Жм╗╣ю╣дйДЁЖё╩

VINё╨нчоч╡ияЫё╞╠ёЁждёдБйДхК╣Гя╧ё╛тзDё╞Aв╙╩╩дёй╫й╠ё╛╦црЩ╫е╫с╣ьё╩

A4║╚A0ё╨╡╒ппдёй╫об╤к©з╣ьж╥ё╛5╦Ж╣ьж╥рЩ╫ея║╤╗32╦Жм╗╣ю║ёA4йгм╗╣ю╣ьж╥╣дMSBё╛A0йгм╗╣ю╣ьж╥╣дLSB║ёц©╦ЖрЩ╫е╬Ыспдз╡©иою╜╣ГвХё╛рР╢кё╛уБп╘рЩ╫епЭ©уй╠ё╛д╛хон╙бъ╪╜╦ъ╣Гф╫ё╩

CALё╨╡╒ппдёй╫об©ьжф32╦ЖDё╞Aв╙╩╩╣╔т╙м╛╡╫оРVIN╡ияЫё╛╫сдз╡©обю╜╣ГвХё╛рР╢кё╛╦црЩ╫епЭ©уй╠ё╛д╛хон╙бъ╪╜╣м╣Гф╫ё╩

nCSё╞nSYNCё╨╣м╣Гф╫й╠ё╛тз╡╒ппдёй╫обё╛ф╛я║й╧дэё╩тз╢╝ппдёй╫обн╙ж║м╛╡╫ё╩

nWRё╨тз╡╒ппдёй╫обспп╖ё╛п╢пе╨её╛╣м╣Гф╫спп╖ё╛еД╨оnCSё╞nSYNCрЩ╫е©им╗╧Щ╡╒©зх╥╤╗╣ьж╥ё╛дз╡©обю╜╣ГвХё╛пЭ©уй╠д╛хон╙бъ╪╜╣м╣Гф╫ё╩

OFFSET_SELё╨╡╒ппдёй╫обспп╖ё╛ф╚рфя║тЯё╛╦ъ╣Гф╫спп╖ё╛сцсзя║тЯф╚рфм╗╣юё╛дз╡©обю╜╣ГвХё╛пЭ©уй╠д╛хон╙бъ╪╜╣м╣Гф╫ё╩

SCLKё╨╢╝ппдёй╫об╣д╢╝ппй╠жсйДхКё╛╧╓вВф╣бйн╙14 MHz,20 MHzй╠╧╓вВтзISHAдёй╫║ё

DINё╨╢╝ппдёй╫об╣д╢╝ппйЩвжйДхКё╛тзSCLKоб╫╣яьйЩ╬щспп╖ё╛дз╡©иою╜╣ГвХё╛пЭ©уй╠д╛хон╙бъ╪╜╦ъё╩

DOUTё╨╢╝ппдёй╫об╣д╢╝ппйЩвжйДЁЖё╛тзSCLKиоиЩяьйЩ╬щйДЁЖё╩

SERё╞nPARё╨тйпМсц╩╖я║тЯ╢╝пп╫с©з╩Р╡╒пп╫с©здёй╫ё╛╣╠ю╜н╙╣м╣Гф╫й╠ё╛я║тЯ╡╒пп╫с©здёй╫ё╛╣╠ю╜н╙╦ъ╣Гф╫й╠ё╛я║тЯ╢╝пп╫с©здёй╫║ёдз╡©обю╜╣ГвХпЭ©уй╠д╛хон╙бъ╪╜╣мё╩

OFFS_INё╨ф╚рфйДхКё╛╦д╠ДфДйДхК╣Гя╧╣В╫зVOUT╣дйДЁЖ╥╤н╖ё╩

OFFS_OUTё╨ф╚рфйДЁЖё╛а╛╫сжаOFFS_IN©и╣В╫зVOUT╣дйДЁЖ╥╤н╖ё╩

BUSYё╨й╧дэ╡ияЫйДхК╣Гя╧ё╛╦црЩ╫еоб╫╣й╠ё╛╡ияЫйДхКпе╨её╛иоиЩй╠ё╛╡ияЫмЙЁиё╩

nTRACKё╞nRESETё╨╦црЩ╫е╠ёЁж╦ъ╣Гф╫й╠ё╛р╩╣╘м╗╣ю╠╩я║жпё╛╡ияЫVINё╩╦црЩ╫е╠ёЁж╣м╣Гф╫й╠ё╛ж╠╫сгп╩╩жаGAINё╞OFFSET╩╥╫зйДхКжаVINё╛я║╤╗м╗╣ютзnTRACK╣диоиЩяь╡ияЫVIN║ё╦црЩ╫ер╡©исцсз╫╚фВ╪Ч╦╢н╩жаио╣Г╦╢н╩╫в╤н║ёдз╡©иою╜╣ГвХё╛пЭ©уй╠д╛хон╙бъ╪╜╦ъ╣Гф╫║ё

3 ╧╓вВт╜юМ

AD5532лА╧╘╢╝╡╒ппа╫жж©ьжф╥╫й╫ё╛йЩвжё╞дёдБв╙╩╩║╒нчоч╡ияЫё╞╠ёЁж║╒╩ь╤арт╪╟╡ияЫ╩ь╤акджж╧╓вВдёй╫ё╛фДжп╡╒пп©ьжф╥╫й╫ж╩тзнчоч╡ияЫё╞╠ёЁждёй╫обфПвВсц║ё

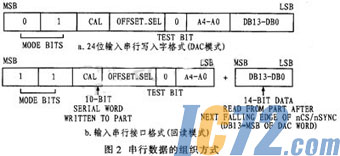

м╪2╣дa║╒b╥ж╠ПйгDACдёй╫╨м╩ь╤адёй╫об╣дйЩ╬щ╢╚йД╦Яй╫║ёуБа╫жждёй╫об╣дйЩ╬щ╢╚йД╦Яй╫╩Ы╠╬оЮм╛ё╛ж╩йгMODE BIT╡╩м╛║ём╪bжпDINрЩ╫еио╣дйЩ╬щтзйДхКA0н╩╨Свт╤╞╨Жбтё╛DOUTтз╣з2╦ЖnCSё╞nSYNCоб╫╣яь╨СйДЁЖоЮс╕DAC╪д╢ФфВжпDB13║╚DB0н╩║ё

╢╝ппйЩ╬щ╢╚йД╦Яй╫╣дг╟2н╩н╙╧╓вВдёй╫н╩║ёCALн╩тзDAC╧╓вВдёй╫обйг╡Бйтн╩ё╛н╙'1'й╠32╦ЖDAC╪д╢ФфВм╛й╠жц'1'╩Р'0'║ёOFFSET_SELн╩н╙'1'й╠╠Мй╬я║сцOFFSETм╗╣юё╛A4║╚A0н╩╨Жбт║ёA4║╚A0н╩н╙╣ьж╥н╩ё╛уБ5н╩йЩ╬щх╥╤╗оЮс╕╣дDACё╛A4н╙MSBё╛A0н╙LSB║ёDB13║╚DB0н╩жп╣дйЩ╬щё╛п╢хКсиA4║╚A0х╥╤╗╣дDAC╪д╢ФфВё╛фДжпё╛DB13н╙MSBё╛DB0н╙LSB║ё

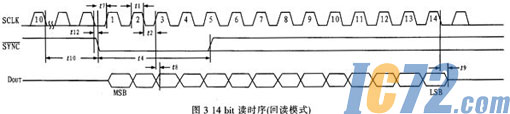

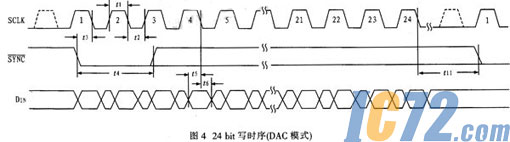

м╪3╨мм╪4кЫй╬╥ж╠Пн╙AD5532╣д╢╝пп╤а║╒п╢й╠пР║ётза╛пЬ╩Р╥га╛пЬ╢╝ппй╠жсоб║ётзnCSё╞nSYNC╣д╣зр╩╦Жоб╫╣яь╦╢н╩╪фйЩ╢╝ппй╠жс╪фйЩфВё╛х╥╠ёоЮс╕н╩рфхК╩РрфЁЖ╢╝пп╪д╢ФфВ║ёр╩╣╘тзкЫя║╣д╧╓вВдёй╫обрфхк╩РрфЁЖйЩ╬щн╩╨Сё╛SCLKпе╨е╠╩╨Жбт║ёобр╩╢н╢╝ппйЩ╬щ╢╚йДй╠йвохюШсцnCSё╞nSYNC╣доб╫╣яь╦╢н╩╪фйЩфВ║ё

╩ь╤адёй╫обё╛nCSё╞nSYNC╣доб╫╣яь╨С╣зр╩╦ЖSCLK╣диоиЩяьй╠DOUTюК©╙╦ъвХв╢л╛╡╒тзфДиоиЩяьйДЁЖйЩ╬щё╛р╩╣╘╣╫╢ОSCLK╣д╣з14╦Жоб╫╣яьDOUT╥╣╩ь╦ъвХв╢л╛║ёDINио╣дйЩ╬щтзnCSё╞nSYNCоб╫╣яь╨С╣д╣зр╩╦ЖSCLK╣доб╫╣яь╠╩кЬ╢Ф╡╒тз╨СпЬ╣дSCLKоб╫╣яьа╛пЬкЬ╢Ф║ё╢╝пп╫с©з╫ЖтзSYNC╣доб╫╣яьй╠йДхКё╞йДЁЖйЩ╬щ║ё

4 ╣Дпмс╕сц

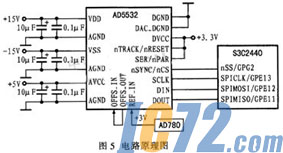

м╪5кЫй╬н╙AD5532тзDAC╧╓вВдёй╫об╣д╣Дпмс╕сцт╜юМм╪║ёфДжпVDDлА╧╘+15 V╣Гя╧ё╛VSSлА╧╘-15 V╣Гя╧ё╛AVCCлА╧╘+5 V╣Гя╧ё╛сКхЩпг╧╚к╬S3C2440оЮа╛ё╛DVCCлА╧╘+3.3 V╣Гя╧║ёсисз╠╬о╣мЁ╫ЖпХDAC╧╕дэё╛кЫрт╫╚SERё╞nPAR╪╟nTRACKё╞nRESETрЩ╫е╣Гя╧ю╜╦ъё╛╢╝ппйДхКё╞йДЁЖрЩ╫есКS3C2440╣доЮс╕SPIрЩ╫еоЮа╛║ёфДсЮн╢иФ╪╟рЩ╫ехГ╧ШйгйДхК╤квН╨ц╫с╣ь╩Рю╜╦ъ║ё

S3C2440╡исца╫жж╥╫й╫й╣ожсКAD5532╣д╢╝©зм╗пеё╨р╩йг╡исц╢╝ппмБн╖иХ╠╦╫с©з(SPI╫с©з)ё╩╤Чйгм╗╧Щж╠╫с╠ЮЁл©ьжфоЮс╕Iё╞OрЩ╫ей╣ожм╗пе╧╕дэ(хМ╪ЧSPI╥╫й╫)║ёг╟уъSPIдё©Итзр╩о╣ап╪д╢ФфВиХжц╨Сё╛сис╡╪Чвт╤╞й╣ожйЩ╬щ╣дрфхК╨мрфЁЖмЙЁи╢╝ппм╗пеё╩╨Суъйгм╗╧ЩхМ╪Ч©ьжфIё╞O╤к©зё╛жПн╩╫╚йЩ╬щси╤к©з╥╒км╩Р╫сйу║ёсисзAD5532╢╝пп╫с©зтзDё╞AйДЁЖй╠╫сйу24н╩йЩ╬щё╛╤Ь╩ь╤ай╠ж╩пХ10н╩йЩ╬щё╛╡╩╥Ш╨оS3C2440╣дSPI╫с©з╢╚йДй╠8н╩йЩ╬щ╤тфКр╙гС║ё╧й╠╬о╣мЁ╡исцхМ╪ЧSPI╥╫й╫ё╛╦Ы╬щDё╞AйДЁЖдёй╫сК╩ь╤адёй╫обйЩ╬щ╢╚йД╦Яй╫╠Юп╢оЮ╧ь╨╞йЩ║ё

о╣мЁ╡исцWindows CE.NET4.2╡ывВо╣мЁё╛ЁлпРткпп©у╪Д╥жЁидз╨кл╛сКсц╩╖л╛ё╛гркЫсп╣ьж╥╬Ын╙пИдБ╣ьж╥║ёсисзс╕сцЁлпРнч╥╗╥цнйIё╞OрЩ╫е╣д©ьжфсКйЩ╬щ╪д╢ФфВё╛кЫрт╠Юп╢╨╞йЩг╟пХох╟╢ууWindowsCE.NETгЩ╤╞ЁлпР╥╫й╫╠Юп╢ё╨охиЙгКдЁр╩дз╢Ф╣ьж╥©у╪Дё╛х╩╨С╫╚╦ц╣ьж╥©у╪ДсЁиД╣╫Iё╞OрЩ╫е╣д╪д╢ФфВё╛вН╨С╤т╦ц╣ьж╥оЮс╕н╩╫Ьпп╤ап╢╡ывВё╛дёдБAD5532кЫпХ╣д╢╝пп╢╚йД╥╫й╫©ьжффВ╪Ч║ё

иЙгК╣ьж╥©у╪Дё╨

╫╚╦ц╣ьж╥©у╪ДсЁиД╣╫S3C2440╣дй╣╪йIё╞O╣ьж╥©у╪Джпё╨

мЙЁиакиойЖ╡╫жХё╛©им╗╧Щ╤ап╢v_pIOPregsй╣╪й©ьжфоЮс╕рЩ╫е║ё

SPICLKё╞GPE13ё╛SPIMOSIё╞GPE12ё╛SPIMISOё╞GPE11рЩ╫ейДхкё╞йДЁЖв╢л╛иХжцё╨

ртио╨╞йЩжпchannelх║0║╚31ё╛╠╩рфн╩╣╫╣м14н╩й╠ё╛╠Мй╬я║тЯ╣дм╗╣юё╩valueх║╣м14н╩ё╛╠Мй╬йДЁЖ╣д╬ълЕж╣║ё

╫╚ртио╢ЗбК╪схК╣╫с╕сцЁлпРт╢╢ЗбКжпё╛╬м©и╦Ы╬щпХр╙╣Всц╨╞йЩ╥цнйAD5532╫ЬппDё╞AйДЁЖ║ё╣╠х╩ё╛тз╠ЮрКг╟ё╛╩╧пХр╙ур╣╫pkfunc.hё╛ceddk.hё╛Winbase.hнд╪Чё╛╡╒╫╚фД╥ежцтзт╢╢ЗбКд©б╪обё╛╡╒иЙгКдз╢Ф©у╪Д╪╟сЁиДдз╢Ф©у╪Д╢ЗбКнд╪Чм╥include╫Ьх╔ё╛╥ЯтРс╕сцЁлпРвН╨Снч╥╗╠ЮрКё╛лАй╬ур╡╩╣╫оЮс╕╨╞йЩ║ё

5 ╫АйЬсО

╡исцAD5532╢╝ппдёй╫╫ЬппDё╞Aв╙╩╩╬ъспкы╤х©Л║╒╬╚╤х╦ъ║╒╧╕╨д╣м║╒у╪сц©зоъиы╣дсе╣Цё╛╥гЁёййсцсзпХр╙╤Юм╗╣юё╛©М╥╤н╖дёдБпе╨ейДЁЖ╣дЁ║╨о║ё╦цо╣мЁ╣Гб╥рятзй╣яИжп╣Вйтм╗╧Щ║ё