日前在美国华盛顿特区(Washington D.C.)举行的国际电子器件会议(International Electron Devices Meeting,IEDM)上,知名厂商展示了最新技术。

CEA-LETI的研究人员采用纳米线(nanowire)作为堆栈架构中的沟道,在纳米线周围布置部分或布满门以实现对其最大程度的控制。通过采用这一架构,当有漏电流流经晶体管的细微通道时,就会导致晶体管截止。

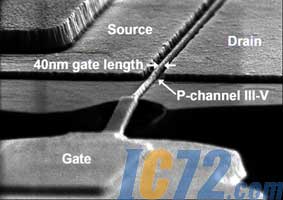

在去年的IEDM上,Intel首次展示如何将制造工艺成熟的硅作为搭载平台与高性能III-V量子集成。本年度Intel研究人员将展示一款低功耗、P型压缩应变QWFET,其最高截止频率与之前报道过的一款III-V P沟道器件相同,为140 GHz。图中所示为闸门长度40-nm、InSb-p沟道压缩应变的QWFET在SEM电子显微镜下的图片。该器件适用于RF领域。

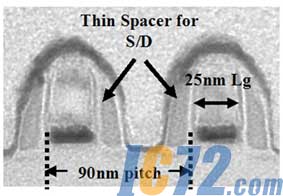

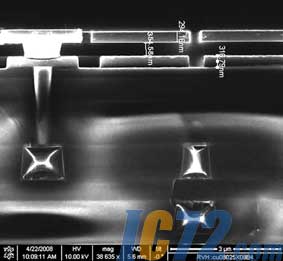

来自IBM的研究人员将展出采用高K介质和金属材料作为栅极、体积最小、功能最丰富的SRAM存储单元。该存储单元可采用22-nm工艺生产,静态噪音容限为220 mV@0.9V。图中所示为已填充STI和栅极优先金属电路布线(patterning)的0.1 μ2 6T-SRAM单元,通过电子显微镜全局扫描所得,其中垂直线为栅极电极。

奇梦达研究人员对三种形式的炭材料进行了评估---纳米管、导电炭和绝缘炭---并发现绝缘炭最有可能实现高密度存储器的低功耗运行。TEM电子显微镜下的图片给出了预期的存储效应。

IMEC研究人员将8μ x 8μ SiGe微镜芯片阵列直接置于6层CMOS电路,制成尺寸为10 cm2的集成芯片。研究人员对SiGe微镜芯片是否优于采用铝材料制成的微镜芯片进行了研究。他们实现了11百万像素分辨率,适用于高端工业使用,如无掩模光刻。该SiGe微镜芯片亦支持单独寻址。

|