具有鲁棒性的低电压、低功率嵌入式闪存技术 |

| 时间:2005/11/1 9:08:00 作者: 来源:ic72 浏览人数:1543 |

|

| |

| |

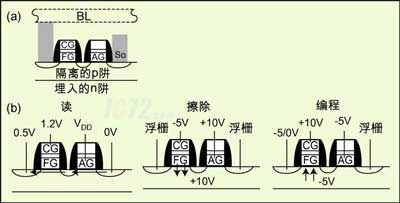

飞利浦半导体公司开发出0.18微米、三阱(triple-well)工艺的嵌入式闪存技术。这种技术采用2T单元、FN-FN编程/擦除和片上电荷泵(用于产生编程/擦除电压),其工作电压范围是1.2~2V。通过优化设计技术、闪存单元和工艺生产出能够在宽泛的操作条件范围内工作且具有高持久性的鲁棒产品。

用于已选定和未选定单元的编程/擦除电压条件针对鲁棒性进行了优化。广泛的可靠性研究表明,数据在位干扰(Bit Disturb)、持久性以及数据保持等几个关键方面的性能都可达到期望值。本文还将简要介绍这种方法的系统优势、应用以及未来的技术发展路线。

在过去十年里,嵌入式非易失性存储器得到了巨大的发展,变得无处不在,并成为微控制器的典型特征。随着片上存储器规模的增加,嵌入式程序变得更加复杂,因而经常需要修改以便纠错和增加新功能。这种修改必须就地实现,因为进行现场升级的成本通常很高。这些趋势迫使业界从EPROM快速转移到片上闪存,从而将使片上闪存成为微控制器的标准特性。

用户和系统对嵌入式闪存的要求

通常,嵌入式闪存的主要驱动力是成本,但并不仅仅是采购成本,而是总拥有成本,包括寿命可靠性、写/擦除周期的持久性、面积效率、编程时间、擦除时间、功耗、工作电压范围、性能和良品率等因素。对所有这些方面进行优化是个复杂的问题,因为许多工作相互抵触。用户普遍希望所有的因素都得到优化。

另一个重要的折衷领域是如何将嵌入式闪存与现有的库和工艺整合。通常,闪存技术落后于数字逻辑工艺大约一代左右。对于嵌入式闪存技术而言,维持与数字和混合信号模块的完整库兼容性是至关重要的。 另一个重要的折衷领域是如何将嵌入式闪存与现有的库和工艺整合。通常,闪存技术落后于数字逻辑工艺大约一代左右。对于嵌入式闪存技术而言,维持与数字和混合信号模块的完整库兼容性是至关重要的。

由于建立新库需要增加开支,这使得有必要在现有逻辑工艺中添加闪存工艺步骤。在掩膜费用方面,这通常会比给独立的闪存添加逻辑更昂贵,但最终结果是得到一种库、工艺和设计流程兼容的技术,这是我们选择的方法。通过大量分析后所作出的其它选择包括:

a)基本的闪存单元设计:在权衡低功耗、持久性、可靠性的要求以及进行风险分析之后,我们决定采用2-T闪存单元。基本原理稍后将深入解释。这种单元比1-T单元大,但更小尺寸的电荷泵等因素可以抵消面积增大的负面影响。

我们相信不论是从成本还是从安全性的角度来看,对于技术故障会导致很高成本的嵌入式应用来说,超出1-T单元的可靠性和鲁棒性优势都是很重要的。选择2-T单元的另一个原因是可以增加EEPROM功能,而没有任何工艺影响。

这种FN-FN单元可靠性很高,而且写入和擦除电流非常低,可以在很大程度上实现编程和擦除的并行操作,其结果是在系统级获得同CHE-FN一样快的平均编程和擦除时间。

b)冗余、修整和纠错:我们决定利用行冗余以及存储在闪存中的信息使良率达到最大化。此外,我们还测量了电荷泵的高电压输出和存储在闪存中的修整数值,以优化单元和感应放大器操作。因为这是一种新技术,而且对于获得可靠和鲁棒的闪存单元来说非常重要,所以我们将8位汉明纠错码(Hamming ECC)添加到128位字存储器中以实现单位纠错。

技术描述

基于以上早期的选择与折衷考虑,我们获得了0.18微米、三阱嵌入式闪存技术。这种基本技术采用2T单元、FN-FN编程/擦除以及片上电荷泵,工作电压范围在1.2V到2V之间。它使用了5或6个金属层与一个本地互连层。单元的大小为0.78平方微米,存取时间(依据阵列大小与VDD范围不同而有很大变化)通常在50ns的范围内。

电荷泵在用户编程控制下打开或关断,并定义了一个编程接口允许应用程序在实际的闪存编程被调用之前控制到行数据锁存器的预写入(整个行可以同时编程;一个实例的大小可以为4Kb),并控制写保护和无保护扇区写状态,这将把错误执行代码而导致扇区意外变化的可能性降到最小,并防止电源故障改变扇区内容(即变成不是被写入的内容)。

2-T单元方法的几个优势:

1. 采用一致的沟道FN隧道进行写入和擦除。在浮栅下没有偏置结,这样大大减少了进入隧道氧化物的空穴注入,提高了保持力以及与应力导致的漏电流相关的持久性。

2. 2-T不象主流的1-T NOR闪存那样需要预擦除编程。这减少了总的编程/擦除时间,而且将持久性有效提高了两倍。 2. 2-T不象主流的1-T NOR闪存那样需要预擦除编程。这减少了总的编程/擦除时间,而且将持久性有效提高了两倍。

3. 2-T单元不会受到过度擦除的影响。过度擦除会使位线电流改变,以至单元不能再被读取。

4. 因为读取栅提供了大的读电流,该单元可以在低电压(1.2V)下被读取。这样控制栅不必在读期间被充电。这是一个主要的优势,因为在用于代码存储的嵌入式闪存中,每个时钟周期都可能发生读操作,而这项优势消除了电荷泵噪声和额外功率。低的控制栅电压还意味着未选定单元的读干扰最小。

可靠性研究

飞利浦半导体在2.7Mb阵列(典型的嵌入式尺寸)上进行了持久性研究。我们执行了两百万个周期,以收集数据。持久性性能明显超过10万周期,显示这个鲁棒设计达到目标。在这些周期之后,我们通过测量栅应力来评估数据保持性,以观察SILC效应。栅应力并没有发现显著变化,受SILC影响的读扰动和数据保持力也如此。

10,000个周期之后,在16Mb演示模块上没有发现因窗口关闭而导致的失败。在120个16Mb样本上获得了长达10万周期的固有持久性。

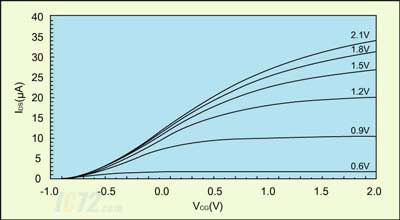

对存储在150℃下的279个样本进行1000小时保持力测试,结果显示没有样品失效。保守推断,经过10年连续读操作和150℃最差条件下的10K持久性考验后的比特失效水平为7ppm的值。图3显示在不同读取栅电压(VDD)下测得的读电流。在1.8V时,读电流标称值为30微安[1],在1.2V时下降到20微安。

一个页的写入时间为1ms(例如,一页的大小可以是512字节长),一个扇区的擦除时间为400ms,因此很容易满足用户的系统需求。该闪存支持自定时和外部定时的读操作,因而允许根据系统周期时间选择适当的读方法来优化功率(自定时在低时钟速度下节省功率;外部定时在高时钟速度下更快)。

目前,飞利浦已经开发出各种尺寸和配置的库模块,并应用在公司不同的嵌入式控制器项目中。扇区尺寸、行和字宽度可以指定以获得最佳系统性能。飞利浦开发的存储器控制器能提供全部JTAG测试功能和连到ARM7 CPU的接口。一个引导加载程序被加入到晶片的专用扇区,然后允许用户程序加载到闪存中,并通过连接到用户程序的闪存编程接口进行升级。

工作硅片已经过验证,而且还规划了许多基于这种技术的使用ARM及其它内核的低成本低电压产品。这种技术有望成为一种大批量的主流嵌入式存储工艺。

|

|

|

|

| |

|

|

|