本文介绍了SATA的新特性及其新的应用模型,包括第1i/2i代和第1m/2m代SATA物理层规范、外部SATA特性以及使用端口多路器的连接模式。作者详细分析了SATA的设计挑战以及高速差分信号和避免阻抗不匹配的PCB设计规则。

作为PC、服务器和消费电子产品中重要的硬盘驱动器接口,串行ATA(SATA)发展迅猛并日益盛行。随着基于磁盘的存储在所有电子市场领域中变得越来越重要,系统设计工程师需要知道采用第一代SATA(1.5Gbps)和第二代SATA(3.0Gbps)协议的产品设计中的独特挑战。此外,系统设计工程师还需要了解新的SATA特性,以使其用途更广,功能更强,而不仅仅是简单地代替并行ATA。充分利用这些新特性并克服设计中存在的障碍,对成功推出采用SATA接口的产品非常关键。

PCB设计挑战和建议

日趋复杂的PCB布局布线设计对保证高速信号(如SATA)的正常工作至关重要。由于第一代和第二代SATA的速度分别高达1.5Gbps和3.0Gbps,因此铜箔蚀刻线布局的微小改动都会对电路性能造成很大的影响。SATA信号的上升时间约为100ps,如此快的上升时间,再加上有限的电信号传输速度,所以即使很短的走线也必须当成传输线来对待,因为这些走线上有很大部分的上升(或下降)电压。

高频效应处理不好,将会导致PCB无法工作或者工作起来时好时坏。为保证采用FR4 PCB板的SATA设计正常工作,必须遵守下面列出的FR4 PCB布局布线规则。这些规则可分为两大类:设计使用差分信号和避免阻抗不匹配。

高速差分信号设计规则包括:

1.SATA是高速差分信号,一个SATA连接包含一个发送信号对和一个接收信号对,这些差分信号的走线长度差别应小于5mil。使差分对的走线长度保持一致非常重要,不匹配的走线长度会减小信令之间的差值,增加误码率,而且还会产生共模噪声,从而增加EMI辐射。差分信号线对应该在电路板表层并排走线(微带线),如果差分信号线对必须在不同的层走线,那么过孔两侧的走线长度必须保持一致。

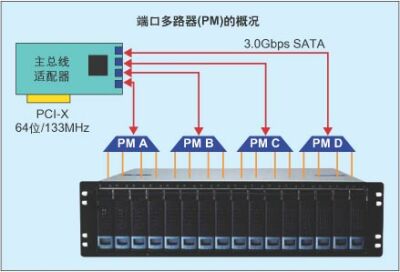

图1: 带4个SATA硬盘驱动器的端口多路器。

2.差分信号线对的走线不能太靠近,建议走线间距是走线相对于参考平面高度的6至10倍(最好是10倍)。

3.为减少EMI,差分对的走线间距不要超过150mil。

4.SATA差分对的差分阻抗必须为100欧姆。

5.为减少串扰,同一层其它信号与差分信号线对之间的间距至少为走线相对于参考平面高度的10至15倍。

6.在千兆位传输速度的差分信号上不要使用测试点。

避免阻抗不匹配的设计规则包括:

1.注意避免不正确的走线宽度和走线相对于参考平面的高度,走线宽度和走线相对于参考平面的高度决定走线阻抗。

2.保持完整的参考平面。在高速信号走线两侧,走线相对于参考平面高度10倍距离范围内,参考平面不应被切断或有挖空的区域。

3.采用宽度过窄以致无法可靠蚀刻的走线,经常会导致走线的宽度或高度发生变化,从而产生问题。最小的走线宽度和走线相对于参考平面的高度应为4mil。

4.采用0402封装的10nF电容,尽量减少走线宽度与电容焊盘宽度的差别。

5.尽可能在同一层走线,如果一定要改变走线层,则必须保证走线层改变后仍有合适的回流路径。

6.注意避免与线路阻抗不匹配的连接器阻抗设计。千兆位信号需要经过特殊设计、与受控阻抗相匹配的连接器。

7.尽可能用表面安装元件来替代通孔插装元件。使元件引脚长度尽量短,切短过长的引脚应作为PCB制作工艺的一部分。

8.尽量保证高速信号走线与同一层其它走线或电路板组成部分(如板边缘、安装孔等)之间的间距不小于走线相对参考平面高度的10倍。

9.不要在高速信号走线上放置测试点(小焊盘或过孔)。

10.确保PCB制作过程中不在高速信号走线相对于参考平面10倍距离内增加取样点(Thieving)。

遵循上述通用规则有助于确保设计获得成功。

SATA的新特性及使用模型

前面介绍了如何进行SATA应用的PCB设计,下面将讨论最新的SATA特性以及这些特性新的使用模型。

1. 第1i/2i代和第1m/2m代SATA物理层规范和外部SATAi 到目前为止,有关第一代SATA的物理层(PHY)速度(1.5Gbps)和第二代SATA的物理层速度(3.0Gbps)的著述和讨论很多,然而,关于物理层规范中的“i”和 “m”部分则关注较少。

第1i代和第2i代串行 ATA 中的“i”代表应用于桌面和移动PC的这两代SATA的速度,分别为1.5Gbps和3.0Gbps。SATA 1.0a规范中定义的一米电缆和连接器都适用于这两种速度,大多数SATA半导体器件都是针对第1i代或第2i代规范而设计的。

大多数人不知道还有第1m代和第2m代SATA规范,这些规范针对外部SATA应用定义,支持两米电缆。从设计角度来看,第1m/2m代应用与第1i/2i代规范是兼容的,但也有些不同。为适应此类应用中信号衰减的增加,它们提高了最小发射信号电平幅度,降低了最小接收幅度。为实现外部ATA应用,主控制器必须兼容第1m代或第2m代SATA。Silicon Image公司的SATA芯片设计考虑了外部SATA应用,所有芯片都包含有可满足第1m代和/或第2m代规范要求的物理层技术。

2. 外部SATA 用于外部SATA的电缆和连接器已有详细定义,可从SATA国际组织的网站(http://www.sata-io.org)下载有关规范。需要着重指出的是,遵循第1m/2m代规范的外部SATA电缆和连接器,与用于主板和内部硬盘驱动器的内部SATA连接器是不同的。针对外部应用的电缆和连接器必须有电磁干扰(EMI)和静电释放(ESD)保护,并且要足够结实,能够经受大量的插/拔操作。因此,外部SATA连接器被刻意设计成与内部SATA连接器不相兼容,以防使用者在外部应用时不小心使用无屏蔽的内部SATA电缆。

这种外部ATA电缆和连接器的意义在于SATA硬盘驱动器现在可以直接用于外部应用。一般来说,并行ATA被视为机箱内部接口,作为并行ATA的继任者,大多数使用者期望SATA也是机箱内部接口,如果需要外部存储,也可能采用其它诸如USB、Firewire/1394或SCSI的接口。

然而,使用采用第1m代(1.5Gbps)或第2m代(3.0Gbps)物理层兼容解决方案的外部SATA电缆和连接器,现已可实现比USB(480 Mbps)或Firewire(400Mbps)速度快得多的外部存储。目前,使用者定期备份80GB硬盘以及将数千兆文件拷贝到外部硬盘的情况并不少见,接口速度成为这类应用的瓶颈。SATA是目前可供普通使用者使用的成本效益最好的高速接口技术之一。

3. 端口多路器

。

图2: 连接一个主机的四个端口多路器的连接示意图

端口多路器(PM, port multiplier)是活动主机与多个设备连接并进行通讯的一种设备。它可看成简单的多路复用器,将一个活动主机的连接复用到多个设备连接上。端口多路器只支持一个活动主机连接,但它可以扩展设计到支持多达15个设备连接,从而利用到主机连接的全带宽。

第二代SATA规范的速度为3.0Gbps,大约相当于300MBps的吞吐能力。当顺序读写数据时,SATA硬盘驱动器目前可支持大约50-60MBps的吞吐能力。因此,利用速度为3.0Gbps的第二代SATA接口的最有效方法,是允许多个设备共享同一电缆所提供的带宽。

为使这种工作能正常进行,需要一个支持端口多路器规范的主机控制器和一个充当多个设备复用器的端口多路器。端口多路器在所有类型的帧信息结构(FIS)中使用4位,即所谓的PM端口字段,来路由主机和相应设备之间的FIS。利用PM端口字段,端口多路器可以将FIS从一个主机路由到多达15个SATA设备。对于从主机端到设备端的FIS,PM端口字段由主机设置为FIS将被路由到的最终设备的端口地址。对于从设备端到主机端的 FIS,PM端口字段由端口多路器设置为发送FIS设备的端口地址。为能使用所有连接到端口多路器上的设备,主机必须拥有用来设置所有发送的FIS中PM端口字段的机制。

图1中,四个SATA硬盘驱动器连接到同一个端口多路器,Silicon Image公司的测试显示,当主机同时访问所有四块硬盘,顺序读写速度超过220MBps。

在图2,一个支持端口多路器的控制器(如Silicon Image公司的SiI 3124-2 PCI-X到4端口SATA II主控制器)通过四个端口多路器连接16个硬盘驱动器。Silicon Image公司展示了一种既简单又具成本效益的方法,即通过服务器或NAS头端的单个PCI-X插槽直接连接16块硬盘。这种采用SATA协议连接SATA硬盘驱动器的直接连接存储方式,能够以尽可能低的价格点为使用者提供易于使用的高速存储。

本文小结

采用SATA接口的设计,要求开发团队中每位成员有新的思考方式。为设计出创新的应用,产品规划师和架构师必须了解SATA的功能特性。设计工程师则必须知道,在进行千兆位串行接口设计时遵循设计规则是至关重要的。尽管设计工程师还要经历一段曲折的学习过程,但最终结果是将带来振奋人心的崭新应用。这些应用将使存储变得更加容易使用并更加具有成本效益,从而广泛地应用于数据中心、办公室和家庭中。

串行ATA已成主流存储接口技术

互联网推动了新一代数据密集型存储应用,这些应用要求存储架构必须是一种可扩展的网络资源,能快速提供容量和数据,串行ATA便是适合此类应用的一种高速连接方式。它采用点对点架构,每台设备可以独享整个带宽,消除了并行ATA的主/从之分,可以和总线上的任何设备直接通讯。

作为并行ATA物理存储接口的替代技术,串行ATA技术能解决如数据传输、散热、可靠性和可管理性等诸多问题。它在性能上的提升主要表现在:

1)数据传输速度高,第一代串行ATA的传输速度已达150MBps,而第二代、第三代串行ATA速度将分别达到300MBps和600MBps,彻底消除了并行ATA的速度瓶颈。

2)采用8b/10b串行传输编码在串行电缆上传输数据,消除了并行ATA数据传输可能产生的串扰及其它一些问题。

3)具备更强的纠错能力,能对传输指令(不仅仅是数据)进行检查,如果发现错误会自动矫正,提高数据传输的可靠性。

4)串行ATA的电缆很细,并可以延伸至1米,使得在大型系统上安装设备和布线变得非常容易。

5)支持热插拔,功耗低。

虽然串行ATA与并行ATA在软件上是兼容的,但串行ATA缺乏与已有ATA设备的无缝兼容。当用户从并行ATA移植到串行ATA系统时,需要对硬件驱动器、电缆和接口进行硬件改造。此外,随着光纤通道(FC)磁盘、SAS(Serial Attached SCSI)等技术的发展,串行ATA在分级存储业务面临竞争和选择。但它仍将携其经济的成本效益、不逊的性能表现和广泛的应用范围,在网络存储应用中大有所为。比如,据IDC预测,到2005年,串行ATA会占有ATA硬盘驱动器市场的全部份额。 |