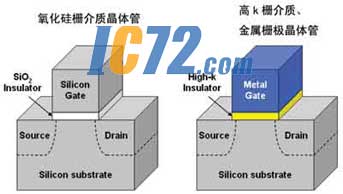

采用氧化硅制造晶体管栅介质已有40余年,随着氧化硅被加工得越来越薄,晶体管性能也稳步提高。然而,从90nm到65nm,再到45nm,氧化硅栅介质厚度的缩小也使栅介质的漏电量越来越高,导致了高能耗和不必要的发热。晶体管栅漏电与不断变薄的氧化硅栅介质有关,这一点已成为过去10年来摩尔定律面临的最大技术挑战之一。

近日,英特尔公司在45nm晶体管栅介质中采用厚度更高的铪基高k(Hafnium-based high-k)材料取代氧化硅,有效的将漏电量减少了十多倍。

由于高k栅介质与目前采用的硅栅电极不兼容,还需要采用金属作为栅极材料。英特尔将在其晶体管栅电极中采用不同金属材料的组合,但具体成分尚未公开。

图:氧化硅栅介质晶体管与高k栅介质、金属栅极晶体管

在英特尔45nm制程技术中,高k栅介质与金属栅极的组合使驱动电流或晶体管性能提高了20%以上,同时,也使源极-漏极漏电降低了5倍以上,大幅提高了晶体管的能效。 |