ժҪ �������������ķ�չ�������Ѿ���Ϊ�ִ������ģ���ɵ�·����е�һ����Ҫ���Լ��.��������ƶ�����Э��MPCPģ���У����ò����ſ�ʱ����һ�����Խ���оƬ����.��Բ����ſؼĴ�����ɲ��Ժ��ѿ���������⣬��ȡ����������ǰ�������Ƶ�ķ�������������ڲ����ſ�ʱ�Ӷ��Կɲ�����ɵ�Ӱ��.���ʹ��SMIC��0.25um CMOS���գ�����Synopsys��power complier���й����Ż����ﵽ�˺ܺõ�Ч��.

�ؼ��� �ſ�ʱ�ӣ����ģ��Ĵ������伶

1������

���ɵ�·��20���ͷ�չ���������˸�����ҵ֮һ���Դ�1958��Texas Instrument��Jack Kilby��������һ�鼯�ɵ�·�𣬼��ɵ�·��ҵһֱ�����ž��˵ķ�չ�ٶȡ�����Intel�Ĵ�ʼ��֮һGordon Moore��ʿ��Ԥ�Եģ�ÿ14��18���£�оƬ�Ͽɼ��ɵľ������Ŀ������һ������������оƬΪ�������ɵ�·�Ĺ�ģ�Ѿ���1971��Intel 4004��2300������ܷ�չ�����ڵ�130nm�Ƴ�Banias���ĵ�7700��������24.5W�����ɢ�ȹ��ʣ�TDP��Thermal Design Power����90nm�Ƴ�Dothan���ĵ�1.4�ڸ������21W�����ɢ�ȹ���[1]��

��CMOS���ֵ�·�У����ĵ���Դ��Ҫ�о�̬���ĺͶ�̬�������������[2]������

��̬����Pstatic������Ԫ�ڷǻ״̬�²����Ĺ��ģ���Ҫ�ɴ�������ɢ���ͳĵ�֮���PN��й©�����Լ�ֱ�������������𣻶�̬����Pdyamic��Ҫ��������Դ������Ԫ��cell������˸��ص��ݳ�ŵ�����Ŀ��ع��ģ�Net Switching Power���͵��ݳ�ŵ��ڼ�������Ԫ�߽紦�������ڲ����ģ�Cell Internal Power��������������PMOS����ܺ�NMOS�����֮���˲���·���������Ķ�·���ġ����ң�

����Pswitching�ǿ��ع��ģ�PSC���ڲ����ġ����Կ�����оƬ�Ķ�̬���ĺ��ص���CL�����ػ�Ԧ���ת��Ƶ��favg����Դ��ѹVDD�͵�ѹ�ڷ��йأ�����оƬ�ֵĹ��Ķ�������ת���ڼ��·�е��ݵij�ŵ�����ģ�Ϊ�˿���ͨ�����ٵ�·�������״̬��ת��ʹ���������·��Ԫ����δ�����״̬�������ġ������ſ�ʱ�ӣ����������˵�·��ʱ������Ŀ��ػ�ԣ�ͨ���ڿ���״̬���뿪ʱ��Ԫ����ʱ�����������ٹ��ģ��������Ϊ��һ�ֽ��Ͷ�̬���ĵ���Ч����[3]��

�������Ƚ������ſ�ʱ�ӵĻ���ԭ����Ȼ������ſ�ʱ�ӵ�ʵ�ַ�ʽ���ڻ�������RTL�����ǰ���£�����Synopsys��˾��Power Compiler��������������ʹ��VCS���з��棬ȡ���˺ܺõ�Ч����

2���ſ�ʱ�ӵĻ���ԭ��

�ſ�ʱ����RTL�������ĵ�һ����Ч�ֶΣ�����ü��ڸ߲�ģ��ʱ���϶�����ÿ������������������ʱ�����붼Ҫ�ſأ�ÿ�������������������ſػ������������ʱ�Ӳ��Գ��Ժ�������Ƶĸ��Ӷȡ�ʱ�ӵ������ĵ�80��������ʱ�����IJ��������ſ�ʱ�������ϴ����Ĵ����������������Լ���ʱ�����ĵ��ݣ�ͬ��Ҳ���Լ��ٱ��ſصĴ��������������ĵ������ġ��ſ�ʱ���ܽ�Լ���ܵĶ���ȡ���ڱ��ſصĴ��������������������Լ��ſ�ʱ��ʹ���ź���Чʱ��ij��̡�

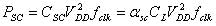

���濴һ���ſ�ʱ�ӵ����ӣ���ͼ1��ʾ����ͬ������ʹ���ź�EN��״̬0ʱ���Ĵ����鴦�ڽ�ֹ״̬����ʱ��ͨ����·���������Ĵ���������Q�����ȶ�״̬����EN����״̬1ʱ���Ĵ����鿪ʼ������ͨ��D����˲��ϻ�ȡ��ֵ��

ͼ1 ���ж�·���ù��ܵ�ͬ���Ĵ���

����ڶ�ʱ�������ڲ���EN=0������£���Ĵ������ϵؼ�����ͬ��ֵ���Ĵ����������ʱ���������Ĺ��Ķ��Ĵ������ֵ�������仯����ʱ��·������Ҳ���Ĺ��ģ�����ʱͨ�����ƼĴ������ʱ���źţ�����������������ʱ�����ڼ��ڼĴ����������ֵͬ����Ҫ���ڼĴ������ʱ�������������ʱ�ӿ��Ƶ�·����������Ҫ��ʱ�ӻ�ԣ���ͼ2��ʾ���ڼĴ�����ʱ�������ϲ���һ��2��������ţ����2�����������ѡ�����ֹ��ʱ�ӱ��أ���ֹ���ſ�ʱ���ź�ȥ�����Ĵ�������С�˵�·�д��ڵ�����Ŀ��ض������Ӷ���������Ϊ�Ĵ���ֵ�������仯�������Ķ���ġ�

ͼ2 ʹ���ſ�ʱ�ӵĻ����������ļĴ���

�ڵ�·�м����ſ�ʱ�ӷdz����ף�����ֱ���������н���������Ҳ����ͨ���ۺϹ����Զ����룬������Synopsys��Physical Complier�����ϣ���ʹ��elaborate����ʱ��ͨ��ʹ��ѡ��-gate_clock���ſ�ʱ�Ӿͻ��Զ��ش����Ͳ���������ʱ�������ϡ�

3. �ſ�ʱ�ӵĵ���ʵ��

ϵͳ��оƬ����ư����ڶ�ļĴ��������������һһ�����Ż���Ȼ�Dz���ʵ��[4]��ʹ��Synopsys��˾��Power Compiler�����Ż����ߣ�������������Physical Compiler������Ż���Ϊ�˲����ſ�ʱ�ӵĹ���ֱ����Physical Compiler�Ľű��ļ��н��У�����������ۺϲ����й����Ż��Ľű���

/* ���ſ�ʱ�����ʱ��Ҫʹ�õı���*/

set power_preserve_rtl_hier_names true /*����RTL����и��������Ϣ*/

set hdlin_no_group_register true

set_clock_gating_style -sequential latch �Cminimum_bitwidth 3 -control_point before -control_signal scan_enable -max_fanout 8 -no_sharing

analyze -f verilog ./mpcp/mpcp_block.v

���� ����

elaborate mpcp_block -gate_clock

hookup_testports -verbose

current_design mpcp_block

link

uniquify

propagate_constraints -gate_clock

Ϊ���õط�������ƣ�ʹ������analyze��elaborate��������read����Դ�����ļ�����Ϊ�������������ſ�ʱ�Ӷ�ʱ���Ӱ����С�������ſ�ʱ�ӵ�����һ��ѡ�������͵ģ������������ض����������������ǵ��Ĵ�����������ܴ�����ͬ��ʹ���źţ��ſ�ʱ��ͨ���趨һ����С��λ���������������ſ�ʱ�ӵ���С�Ĵ�����Ŀ��һ��أ���ͨ��������飬�������Ե�����ֵ��

�ſ�ʱ�ӵIJ��룬�����˵�·�ĸ��Ӷȣ���Ȼ�����ƵĿɲ������һ����Ӱ�졣����ͨ��״���£���ɨ��Ĵ����飬�ſؼĴ����IJ������ɲ��Ժ��ѿ��ƣ�����ɨ������һ�㲻�˲����ſ�ʱ�ӡ������ɨ������û�мĴ����Ļ����Ĵ������������˵Ŀɲ��Ծ�û�취���ƣ��������ڵĴ������ƶ������ڶ���ſؼĴ������ɴ�ʹ����ƵĹ��������������С��Ϊ�����һ���⣬��������������ǰ�������Ƶ㣬ѡ�-control_point before����ʾ����������ǰ�������Ƶ㣬ѡ�-control_signal scan_enable����ʾ���Ƶ��źŲ��õ�scan_enable��ģʽ�����Ƶ��ź���scan_enable��test_mode����ģʽ��һ������£�ǰ�߱Ⱥ����ܹ��ṩ���ߵĹ��ϸ����ʣ�ǰ�߽�����ɨ��ģʽ�Ǽ���ģ������������������ڼ䶼���ڼ���״̬������������в���Ĭ�ϵ�scan_enableģʽ��ֵ��ע����ǵ�����test_modeģʽʱ������ʹ��ѡ�-observation_point���͡�-observation_logic_depth���������ƵĿɹ۲��ԡ����⣬ѡ�-max_fanout��ָ����RTL���ſص�Ԫ������ȳ�������ʹ�����ѡ���ʱ��hdlin_no_group_register�� �������뱻����Ϊtrue��ʹPower Compiler���������ϵ�ͬ���ſص�Ԫ�ļĴ����顣

4. �����Ż���ʱ��������

�����Ի���EPON��ONU�������е�MPCPģ��Ϊ��������SMIC ��0.25um CMOS���տ⣬����֤�ſؼ������Ż������

ʹ��Physical Compiler�����ۺϣ���1��ʾ��ʹ��ʱ���ſ�ǰ��Ĺ��ı��档�ӱ����п��Կ����������ſ�ʱ�Ӽ������Ľ�����Լ70�����������㿪�ع����½���68������й©���Ľ��½���6.5%������Ԫ��Ŀ������6.4%����Ԫ���Ҳ������2�����ɴ�˵���ſ�ʱ�ӵIJ��룬����ʹ��̬���������½������Ҷ�����Ԫ�����Ҳ��һ�����Ż���

���⣬�����ſ�ʱ�ӣ���Ϊʱ��ƫ�clock skew���Ĵ���,��Ӧ��ʱ������Ҳ�ᷢ��һ���ı仯��Ϊ����֤��Ƶ���ȷ�ԣ������ʹ��primetime ���о�̬ʱ�������STA��Static Timing Analyze�����Լ���ſ�ʱ�ӵĽ����ͱ���ʱ���Ƿ����㣬�ڶԽ���ʱ�����ʱ�����ʱ���ź�Ҫ���ʱ�䣨data required time����������źŵ���ʱ�䣨data arrival time�����ſ�������ʱ��ӯ��Ϊ����slack(MET)��,�������VIOLATED��������෴�Ա���ʱ�����ʱ�����ʱ��data required time����С��data arrival time�ſ���ʹʱ��ӯ��MET����2Ϊ�����ſ�ʱ�Ӻ������µ�һ��setup��ʱ����Ľ����

�����ſ�ʱ���Ż����һ��·����setupʱ��

Startpoint: ex33/ex_burst/StartTime_reg_reg[0]

(rising edge-triggered flip-flop clocked by my_clk)

Endpoint: ex33/ex_burst/stopTime_reg[31]

(rising edge-triggered flip-flop clocked by my_clk)

Path Group: my_clk

Path Type: max

Point Incr Path

---------------------------------------------------------------------------

clock my_clk (rise edge) 0.00 0.00

clock network delay (ideal) 1.50 1.50

���� ���� ����

data required time 32.89

data arrival time -23.87

-------------------------------------------------------------------------

slack (MET) 9.02

5. ����

�ſ�ʱ�Ӽ�����Ŀǰʵ�ֵ��ĵ�һ����Ҫ����������Ҫ�����ڲ��ſؼĴ����Ϳ��������ϵĹ��ģ���������ʹ�úͲ��õĹ����ء�������MPCPģ������У������ſ�ʱ�ӽ��й����Ż�������ʱ������Ϳɲ��Ե�Ӱ�죬������Ч��С�˹��ģ��������Ҳ�����½����ɼ��ڼ��ɵ�·��ģ��������������£��ü�����һ�ֺܺõĽ����ĵķ��������ڿ���Ƭ��ϵͳоƬ�Ĺ������Ź㷺��Ӧ��ǰ����

�������ߵĴ��µ�����ͨ���ӿ��������������Ϊ�ſ�ʱ�Ӳ������ɵIJ��Ժ��ѿ��Ƶ����⡣ |