“э —‘

ЇмЌв ”∆µі¶јнѕµЌ≥ «µд–Ќµƒ µ ±–≈Ї≈і¶јнѕµЌ≥£ђЊя”– эЊЁЌћЌ¬ЅњіуЇЌ‘ЋЋг√№Љѓґ»ЄяµƒћЎµг£ђ“ї∞г”…Ќ®”√DSP µѕ÷Єі‘”µƒ ”∆µі¶јнЋгЈ®°£ƒњ«∞ЄяґЋЌ®”√DSPµƒ÷ч∆µ“—іпµљ600 MHz“‘…ѕ£ђƒЏ≤њЉѓ≥…ґаЄц‘ЋЋгµ•‘™£ђ‘ЋЋгƒ№Ѕ¶њ…“‘¬ъ„гіуґа ”∆µі¶јнЋгЈ®µƒ“™«у°£µЂ «“ї∞гµƒЌ®”√DSP÷ї”–“їћх эЊЁ„№ѕя£ђ эЊЁЌћЌ¬ƒ№Ѕ¶µЌ£ђ±Ў–л‘ЏDSPЌв≤њљш–– эЊЁ д»лїЇ≥еЇЌ д≥цїЇ≥е£ђ–и“™DSPƒЏЇЋ≤ќ”л’ыЄц эЊЁЌћЌ¬єэ≥ћ£ђ’вЊЌіуіуѕч»хЅЋDSPµƒ‘ЋЋгƒ№Ѕ¶£ђЌђ ±‘цЉ”ЅЋѕµЌ≥єєЉ№µƒЄі‘”ґ»£ђ“тіЋ£ђ эЊЁЌћЌ¬≥…ќ™їщ”ЏЌ®”√DSPµƒЇмЌв ”∆µі¶јнѕµЌ≥µƒ„оіу∆њЊ±°£

BlackfinѕµЅ–DSP„®√≈’лґ‘ЄяЋў эЊЁЌћЌ¬Љѓ≥…ЅЋ≤Ґ––ЌвќІљ”њЏ£®PPI£©£ђ‘ЏіЂЌ≥µƒ эЊЁ„№ѕяµƒїщі°…ѕ‘цЉ”ЅЋ“їћх эЊЁЌћЌ¬Ќ®µј°£PPIљ”њЏ£Ї1£©ƒ№“‘„оЄя66 MHz µƒ∆µ¬ љ” ’ эЊЁ£ђ“‘„оЄя60 MHz µƒ∆µ¬ д≥ц эЊЁ£ї2£©≤ї‘ў–и“™ґоЌвµƒ эЊЁ д»л/ д≥цїЇ≥е£ђ÷±љ”Ѕђљ”ЄяЋўAD/DA д»л д≥ц эЊЁ£ї3£©ƒ№єї д»лїт д≥цITU-R601/656 Єс љЇЌіш––≥°Ќђ≤љ ±÷”µƒRGBЄс љµƒ э„÷ ”∆µ°£ є”√PPIљ”њЏ д»л д≥ц эЊЁ£ђЄ®“‘«њіуµƒDMAЅчЅњњЎ÷∆ЇЌЄяЋўSDRAM£ђ єBlackfinDSPµƒƒЏЇЋґјЅҐ”Џ эЊЁЌћЌ¬єэ≥ћ£ђ≥дЈ÷ЈҐї”∆д√№Љѓ‘ЋЋгƒ№Ѕ¶£ђ≤ҐЉтїѓЅЋѕµЌ≥єєЉ№£ђ‘ЏЇмЌв ”∆µі¶јнЌ®”√ƒ£њй÷–»°µ√ЅЋЅЉЇ√µƒ”¶”√°£

ЇмЌв ”∆µі¶јнЌ®”√ƒ£њй эЊЁЌћЌ¬Ј÷ќц

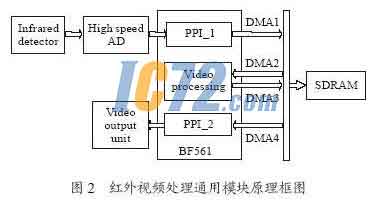

“їЄцЌ®”√µƒЇмЌв ”∆µі¶јнЅч≥ћ»зЌЉ1Ћщ Њ£ђјы”√ЄяЋўAD≤…Љѓћљ≤в∆ч д≥цµƒƒ£ƒв–≈Ї≈£ђ–ќ≥…‘≠ Љ ”∆µ эЊЁЅч£ђ‘ўЊ≠єэ ”∆µі¶јнµ•‘™µƒ µ ± ”∆µі¶јн£ђ“‘ћЎґ®µƒ ”∆µЄс љЄяЋў д≥ц°£

ЇмЌв ”∆µі¶јнєэ≥ћ «“їЄцЄяЋў эЊЁЌћЌ¬ЇЌ√№Љѓ‘ЋЋгµƒ≤ҐЈҐєэ≥ћ°£µ± ”∆µі¶јнЋгЈ®Єі‘” ±£ђ ”∆µі¶јнµ•‘™ґа”…Єя–‘ƒ№Ќ®”√DSPєє≥…°£DSPљ” ’AD д≥цµƒ‘≠ Љ ”∆µ эЊЁ « эЊЁ–і»лµƒєэ≥ћ£ђDSP д≥ці¶јнЇу ”∆µ « эЊЁґЅ≥цµƒєэ≥ћ£ђDSPљш–– ”∆µі¶јн‘ЋЋг÷Ѕ…ў–и“™“їіќ эЊЁґЅ≥цЇЌ“їіќ эЊЁ–і»л£ђ“тіЋ эЊЁ–і»л°Ґ эЊЁґЅ≥цЇЌ÷–Љдµƒ ”∆µі¶јн»э’яЌђ ±љш––£ђ÷Ѕ…ў∞ьЇђЅљіќ эЊЁґЅЇЌЅљіќ эЊЁ–і°£“ї∞гµƒЌ®”√DSP÷ї”–“їћх эЊЁ„№ѕя£ђќёЈ®≤Ґ––љш–– эЊЁЌћЌ¬ЇЌ ”∆µі¶јн‘ЋЋг£ђЋщ“‘Ќ®≥£‘ЏЄяЋўADЇЌDSP÷ЃЉд°Ґ‘ЏDSPЇЌ ”∆µ д≥цµ•‘™÷ЃЉд£ђ‘цЉ”FIFO°ҐЋЂњЏRAMїтЋЂ∆ђSRAM ¬÷її£ђєє≥… эЊЁїЇ≥еїЈљЏ£ђ”…DSPƒЏЇЋњЎ÷∆ эЊЁїЇ≥еєэ≥ћ°£’в єµ√ѕµЌ≥єєЉ№±дµ√Ј«≥£Єі‘”£ђґш«“ эЊЁїЇ≥еєэ≥ћ’Љ”√ЅЋDSPƒЏЇЋљш–– эЊЁ‘ЋЋгµƒ ±Љд£ђіуіуљµµЌЅЋDSPµƒ–І¬ °£

±Њќƒїщ”ЏAnalog DeviceєЂЋЊBlackfinѕµЅ–BF561–ЌЌ®”√DSP£ђјы”√∆дћЎ”–µƒPPIљ”њЏ£ђћб≥ц“ї÷÷ЇмЌв ”∆µі¶јнЌ®”√ƒ£њйµƒєєЉ№£ђ °¬‘ЅЋ эЊЁїЇ≥еїЈљЏ£ђ є эЊЁЌћЌ¬єэ≥ћґјЅҐ”ЏDSPƒЏЇЋ£ђїщ±Њ≤ї’Љ”√DSPљш–– эЊЁ‘ЋЋгµƒ ±Љд£ђ≥дЈ÷ЈҐї”ЅЋDSP√№Љѓ‘ЋЋгµƒ”≈ ∆°£ѕµЌ≥єєЉ№»зЌЉ2Ћщ Њ°£

BF561 ƒЏ≤њЉѓ≥…ЅЋЅљЄцЌк»ЂѕаЌђµƒBlackfinDSPƒЏЇЋ£ђє≤”–ЅљЄцPPIљ”њЏ£ђЈ÷±р”лЄяЋўADЇЌ ”∆µ д≥цµ•‘™÷±љ”љ”њЏ°£‘≠ Љ ”∆µ эЊЁ°Ґ„о÷’ д≥цµƒ ”∆µ эЊЁЇЌ ”∆µі¶јнµƒ÷–Љд эЊЁ£ђ»Ђ≤њіжіҐ‘ЏЄяЋўSDRAM÷–°£Ќ®єэ4 ћхґјЅҐµƒDMAЌ®µјЇЌBlackfinDSPћЎ”–µƒDMAЅчЅњњЎ÷∆£ђє≤ѕнSDRAMЄяіп133MHz°Ѕ16ќїµƒішњн°£DSPƒЏЇЋ÷ї–и“™≥х ЉїѓDMAµƒє§„ч≤ќ э£ђЊяћеµƒ эЊЁЌћЌ¬”…DMAњЎ÷∆∆чґјЅҐЌк≥…£ђ≤ї‘ў–и“™DSPƒЏЇЋЄ…‘§°£ќ™љш“ї≤љЋхґћ эЊЁµ»іэ ±Љд£ђћбЄяDSPµƒ‘ЋЋг–І¬ £ђЋщ”–µƒ эЊЁґЅ–іґЉ…и÷√ќ™ішЅчЅњњЎ÷∆µƒ∆є≈“≤ў„ч£ђ µѕ÷ЅЋ‘ЏDMAЌћЌ¬ эЊЁµƒЌђ ±љш–– ”∆µі¶јн‘ЋЋг£ђ„оіу≥ћґ»…ѕЈҐї”ЅЋDSPµƒ√№Љѓ‘ЋЋгƒ№Ѕ¶°£

PPIљ”њЏ≈д÷√

PPIљ”њЏ «“ї÷÷њ…“‘≈д÷√≥…8°Ђ16 ќї эЊЁњнґ»µƒґає¶ƒ№≤Ґ––Ќђ≤љ„ЉЋЂѕтљ”њЏ£ђ∞ьј®»эћхЌђ≤љ–≈Ї≈ѕяЇЌ“їЄцЅђљ”µљЌв≤њ ±÷”µƒ ±÷”ѕя£ђЌ®єэ–ёЄƒѕа”¶µƒЉƒіж∆ч…и÷√PPIљ”њЏЄч÷÷є§„чƒ£ љ°£

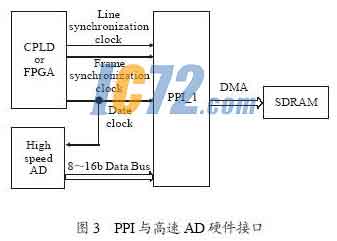

PPI”лЄяЋўAD”≤Љюљ”њЏ

»зЌЉ3 Ћщ Њ£ђ“‘CPLDїтFPGA µѕ÷њЎ÷∆ ±–т£ђќ™ЄяЋўADЇЌPPI_1 ћбє© эЊЁ ±÷”£ђЄщЊЁћљ≤в∆ч д≥цµƒ––Ќђ≤љ ±÷”ЇЌ≥°Ќђ≤љ ±÷”£ђЊ≠єэ“їґ®±дїї£ђћбє©ЄшPPIљ”њЏ£ђЌ®єэDMA£ђPPIљ”њЏЄщЊЁ»эЄц ±÷”–≈Ї≈љЂAD д≥цµƒ8°Ђ16ќї эЊЁ–і»лSDRAM°£±Њљ”њЏ÷І≥÷8°Ђ16 ќї≤Ґ–– д≥цµƒЄяЋўAD£®јэ»зAD9240£©£ђ эЊЁ ±÷”„оЄя66 MHz°£

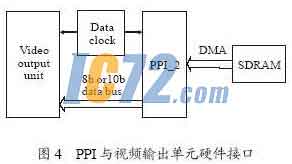

PPI”л ”∆µ д≥цµ•‘™”≤Љюљ”њЏ

»зЌЉ4 Ћщ Њ£ђЌ®єэDMA£ђPPI_2 ґЅ»°SDRAMƒЏµƒ ”∆µ эЊЁ£ђЄщЊЁ эЊЁ ±÷”£ђ“‘ITU-R656 Єс љ£ђ д≥цµљƒ£ƒв ”∆µ±а¬л∆ч£®јэ»зADV7171£©£ђ“‘PALїтNTSC ÷∆ љ д≥цµљЉа ”∆ч°£

PPIљ”њЏЉƒіж∆ч…и÷√

PPIљ”њЏњ…“‘…и÷√ќ™ITU-R656 д»лƒ£ љ£ђITU-R656 д≥цƒ£ љ£ђЌ®”√ д»лƒ£ љЇЌЌ®”√ д≥цƒ£ љ°£√њ÷÷є§„чƒ£ љ÷–”÷њ…“‘…и÷√ эЊЁњнґ»£ђЌђ≤љ ±÷”є§„чЈљ љЇЌ эЊЁіт∞ь/љв∞ьµ»ґа÷÷є§„чћхЉю°£Ќ®єэ–іPPI_CONTROL°ҐPPI_DELAY ЇЌPPI_COUNT »эЄцЉƒіж∆ч…и÷√PPIљ”њЏµƒє§„чƒ£ љ°£

PPIљ”њЏњЎ÷∆Љƒіж∆ч£ЇPPI_CONTROL

PPIљ”њЏњЎ÷∆Љƒіж∆чЄчќїє¶ƒ№ґ®“е»зЌЉ5 Ћщ Њ£ђ”лЄяЋўAD д»лЇЌ ”∆µ д≥цѕаєЎµƒ…и÷√»зѕ¬£ђ

1£©…и÷√Ќђ≤љ ±÷”ЉЂ–‘ЇЌ…и÷√ эЊЁ ±÷”ЉЂ–‘£ЇFS1&FS2polarity£ђDatAclk polarity —°‘сЌђ≤љ ±÷”ЇЌ эЊЁ ±÷”…ѕ…э—Ўїт «ѕ¬љµ—Ў”––І°£

2£©…и÷√ эЊЁњнґ»£ЇDatAbuswidth …и÷√ эЊЁ„№ѕяњнґ»£ђ„о–°8 ќї£ђ„оіу16 ќї°£

3£©…и÷√ эЊЁіт∞ь/љв∞ьƒ£ љ£ЇPacking modeenable…и÷√ «Јс єƒ№ эЊЁіт∞ь/љв∞ьƒ£ љ£ђ»ф єƒ№£ђµ±PPIљ”њЏі¶”Џ8 ќї д»лƒ£ љ£ђ‘тљЂ д»лµƒЅљЄц8 ќї эЊЁіт∞ьќ™1 Єц16 ќї эЊЁіжіҐ£їµ±PPIљ”њЏі¶”Џ8 ќї д≥цƒ£ љ£ђ‘тљЂ1 Єц16 ќї эЊЁ∞іµЌќї‘Џ«∞Єяќї‘ЏЇуµƒЋ≥–тљв∞ь д≥ц£їµ±PPIљ”њЏќ™8 ќї эЊЁњнґ»£ђ эЊЁіт∞ь/љв∞ьƒ£ љƒ№єїљµµЌ1 ±ґ эЊЁіжіҐњ’ЉдЇЌљµµЌ1±ґ эЊЁ д»лішњн°£

4£©…и÷√Ќђ≤љ ±÷”є§„чƒ£ љ£ЇPortconfiguration—°‘с д»лїт д≥цƒ£ љѕ¬Ќђ≤љ ±÷”є§„чƒ£ љ£ђ”лЄяЋўADљ”њЏ д»л‘≠ Љ ”∆µ эЊЁ–и“™ЅљЄцЌђ≤љ ±÷”£ђ”лƒ£ƒв ”∆µ±а¬л∆чљ”њЏ д≥цITU-R656Єс љ э„÷ ”∆µ£ђ≤ї–и“™Ќђ≤љ ±÷”°£

5£©…и÷√ д»лїт д≥ц„”ƒ£ љ£ЇTransfer type”лЄяЋўADљ”њЏ д»л‘≠ Љ ”∆µ эЊЁ ±£ђ є”√Ќ®”√ д»лє§„чƒ£ љ£ї”л ”∆µ д≥цµ•‘™љ”њЏ д≥ц ”∆µ эЊЁ£ђ є”√≤їішЌђ≤љ ±÷”µƒ д≥цє§„чƒ£ љ°£

6£©—°‘с д»лїт д≥цЈљѕт£ЇPort direction”лЄяЋўADљ”њЏ д»л‘≠ Љ ”∆µ эЊЁ ±£ђ—°‘с д»лƒ£ љ£ї”л ”∆µ д≥цµ•‘™љ”њЏ д≥ц ”∆µ эЊЁ£ђ—°‘с д≥цƒ£ љ°£

7£©∆фґѓPPIљ”њЏ£ЇEnablePPI∆фґѓPPIљ”њЏЇу£ђ‘Џ д»лƒ£ љ ±£ђµ±PPIљ”њЏљ” ’µљ’э»ЈµƒЌђ≤љ ±÷”–≈Ї≈≤≈њ™ Љ д»л эЊЁ£ї‘Џ д≥цƒ£ љ ±£ђµ±ѕа”¶µƒЌђ≤љ ±÷”њ™ Љє§„чЇу≤≈њ™ Љ д≥ц эЊЁ°£

PPIљ”њЏ—”≥ўЉƒіж∆ч£ЇPPI_DELAY

‘Џ––Ќђ≤љ ±÷””––ІЇу£ђ—”≥ўPPI_DELAY Єц эЊЁ ±÷”£ђPPIљ”њЏњ™ Љ д»лїт д≥ц––ѕсЋЎ°£

PPIљ”њЏЉ∆ эЉƒіж∆ч£ЇPPI_COUNT

‘Џ––Ќђ≤љ ±÷””––І∆ЏƒЏ£ђPPIљ”њЏ д»лїт д≥цPPI_COUNT Єц––ѕсЋЎ°£

PPIљ”њЏDMA…и÷√

DMAЅчЅњњЎ÷∆

DSPƒЏЇЋ…и÷√PPIљ”њЏDMAµƒ≥х Љє§„ч≤ќ эЇу£ђ”…DMAњЎ÷∆∆чґјЅҐЌк≥…PPIљ”њЏґЅ»°ЇЌ–і»лSDRAMµƒ≤ў„ч°£SDRAM эЊЁ„№ѕяішњнќ™133 MHz°Ѕ16 ќї£ђµЂ÷ї”–“їћх эЊЁ„№ѕя£ђ≤Ґ«“ЇмЌв ”∆µі¶јнєэ≥ћ÷– эЊЁ–і»л°Ґ эЊЁґЅ≥цЇЌ÷–Љдµƒ ”∆µі¶јн»э’я–и“™Ќђ ±љш––£ђ÷Ѕ…ў∞ьЇђЅљіќ эЊЁґЅЇЌЅљіќ эЊЁ–і°£»зєы∞і ±Љдљш≥ћµ•»ќќсѕя–‘∞≤≈≈PPIљ”њЏDMAґЅ–іSDRAMµƒ≤ў„ч£ђ≤їƒ№≥дЈ÷јы”√SDRAMµƒішњн£ђќёЈ®Ќк≥…≤ҐЈҐґЅ–іSDRAM µƒ“™«у°£ќ™ЅЋ≥дЈ÷јы”√SDRAM µƒішњн£ђ±Ў–л є”√BlackfinDSPћЎ”–µƒDMAЅчЅњњЎ÷∆°£

≤…”√DMAЅчЅњњЎ÷∆ ±£ђDMAњЎ÷∆∆ч „ѕ»Ј÷ќцЋщ”– єƒ№µƒDMAЌ®µј£ђћбЄя”л’э‘Џ‘Ћ––µƒDMAµƒґЅ–іЈљѕт“ї÷¬µƒDMAЌ®µјµƒ”≈ѕ»Љґ£ђјэ»зµ±«∞DMA’э‘ЏґЅSDRAM£ђƒ«√іЋщ”–ґЅSDRAM µƒDMAЊщ±»–іSDRAM µƒDMAµƒ”≈ѕ»ЉґЄя£ђЋщ”–ґЅSDRAM µƒDMA∞ієћ”–”≈ѕ»Љґ≈≈Ѕ–іќ–т°£“‘‘§÷√µƒЅчЅњ ±ѕґќ™÷№∆Џ£®јэ»з10 „÷љЏ£©£ђ∞і133 MHzµƒ„оіуЋўґ»£ђ√њіќЈҐґЅ10 „÷љЏ эЊЁµљµ±«∞DMAЌ®µјµƒFIFO ƒЏ£ђ¬÷їїµљѕ¬“їЄцDMAЌ®µј°£µ±Ћщ”–ґЅSDRAM µƒDMA÷і––Ќк“ї±йЇу£ђ¬÷їїµљ–іSDRAM µƒDMA£ђ÷і––ѕаЌђєэ≥ћ°£’в—щ£ђљµµЌЅЋЄƒ±дSDRAM ґЅ–іЈљѕтЇƒЈ—µƒ ±Љд£ђЌђ ±√њЄц єƒ№µƒDMAЌ®µј‘Џ…иґ®µƒ÷№∆ЏƒЏґЉ“‘„оіуЋўґ»¬÷її÷і––ЅЋ“ї±й£ђ±£÷§ЅЋ“їґ® ±ЉдƒЏґ‘SDRAM µƒ≤ҐЈҐґЅ–і≤ў„ч£ђ≥дЈ÷јы”√ЅЋSDRAM љ”њЏµƒ„оіуішњн°£

∆є≈“≤ў„ч

”…”ЏЇмЌв ”∆µі¶јнєэ≥ћ÷– эЊЁ–і»л°Ґ эЊЁґЅ≥цЇЌ÷–Љдµƒ ”∆µі¶јн»э’яЌђ ±љш––£ђЋщ“‘µ±«∞DMAґЅ»°їт–і»лµƒ эЊЁ£ђЊЌ «DSPƒЏЇЋїт∆дЋыDMA“—Њ≠–і»лїтљЂ“™ґЅ»°µƒ эЊЁ£ђ’в «“їЄцЉґЅ™µƒ“тєыѕµЌ≥°£»зєыµ±«∞DMA’э‘ЏґЅ–іµƒ эЊЁ‘Џ ±Љдїт“тєыєЎѕµ…ѕ”лDSPƒЏЇЋїт∆дЋыDMAЈҐ…ъ≥еЌї£ђЊЌїбµЉ÷¬ эЊЁµ»іэїт эЊЁінќу°£

ќ™љµµЌ эЊЁµ»іэ ±Љд≤Ґ±№√в“тєыінќу£ђґ‘√њЄцDMA≤ў„ч£ђ‘Џƒњ±кіжіҐ«шƒЏґЉњ™±ўЅљЄцїЇ≥е«ш£ђ…иќ™BufferAЇЌBufferB°£µ±«∞DMA’э‘Џ≤ў„чµƒ…иќ™BufferA£ђ’в «ґј’Љ–‘≤ў„ч£ђ≤ї‘ –н∆дЋыDMAїтDSPƒЏЇЋЈ√ќ °£µ±«∞DMA“—Њ≠≤ў„чЌк±ѕµƒ…иќ™BufferB£ђњ™Ј≈Єш∆дЋыDMAїтDSPƒЏЇЋЈ√ќ °£µ±«∞DMA≤ў„ч‘ЏBufferAЇЌBufferB÷ЃЉд«–її£ђЌ®єэ–≈Ї≈Ѕњ±к÷Њґј’Љ«шЇЌњ™Ј≈«ш£ђ”Џ «‘Џ»ќ“ї ±Љд£ђµ±«∞DMAґЉ”–“їЄцњ…є©∆дЋыDMAїтDSPƒЏЇЋЈ√ќ µƒ«ш”т£ђ’в—щЊЌљµµЌЅЋ эЊЁµ»іэ ±Љд£ђ≤Ґ±№√вЅЋ“тєыінќу°£

љб ¬џ

±Њќƒ‘Џљй…№ЅЋPPIљ”њЏ–‘ƒ№ћЎµгµƒїщі°…ѕ£ђћб≥цЅЋ“ї÷÷ЇмЌв ”∆µі¶јнЌ®”√ƒ£њйµƒєєЉ№£ђ °¬‘ЅЋ эЊЁїЇ≥еїЈљЏ£ђ є эЊЁЌћЌ¬єэ≥ћґјЅҐ”ЏDSPƒЏЇЋ£ђћбЄяЅЋDSPµƒ‘ЋЋг–І¬ °£ |