ժҪ������SDRAM����Ҫ�����źźͻ�������ʱ�����һ��Ӧ���ڽ⸴�õ�֧�ֶ�·��д��SDRAM�ӿ���ƣ�Ϊ��Ҫ�������洢���ĵ�·����ṩ����˼·��

�ؼ��ʣ�SDRAM �⸴�� �ӿ�

�洢���Ǵ��������ݴ�����·����Ҫ��ɲ��֡��������ݴ��������Ľ�һ����չ�����ڴ洢�������������������Խ��Խ�ߵ�Ҫ��ͬ����̬����洢��SDRAM(Synchronous Dynamic Random Access Memory)����������д�ٶȿ졢֧��ͻ��ʽ��д����Ե����ļ۸���õ��˹㷺��Ӧ�á�SDRAM�Ŀ��ƱȽϸ��ӣ���ӿڵ�·����ǹؼ���

�������Ƚ���SDRAM����Ҫ�����źźͻ������Ȼ����ܽӿڵ�·��SDRAM����Ҫ����·�����������̣�Ӧ���ڽ⸴�õ�SDRAM�ӿڵ�·����Ʒ�������������ʵ�ֽ����

1 SDRAM����Ҫ�����źźͻ�������

SDRAM����Ҫ�����ź�Ϊ��

��CS:Ƭѡʹ���źŢ��͵�ƽ��Ч��

��RAS:�е�ַѡͨ�źţ��͵�ƽ��Ч��

��CAS:�е�ַѡͨ�źţ��͵�ƽ��Ч��

��WE:дʹ���źţ��͵�ƽ��Ч��

SDRAM�Ļ��������Ҫ�����źż���1��

���еIJ��������źš�����������ݶ����ⲿʱ��ͬ����

2 �ӿڵ�·��SDRAM����Ҫ����·������������

һ���걸��SDRAM�ӿںܸ��ӡ����ڱ��ĵ�SDRAM�ӿ�Ӧ���ڽ⸴�ã��������¼������˵�Ƚϼ�������Լ���ƶ���Ӱ�����ܡ��ӿڵ�·��SDRAM����Ҫ�����ɷ�Ϊ����ʼ����������������д�������Զ�ˢ�²�����

(1)��ʼ������

SDRAM�ϵ�һ��ʱ�������ʼ�������ſ��Խ��������������̡���ʼ����Ҫ���Ԥ��硢�Զ�ˢ�º�ģʽ�Ĵ��������á�����������ͼ1��ʾ��

(2)�����

��д������Ҫ�����SDRAM�����ݽ�����������������ͼ2��ʾ��д����������ͼ3��ʾ��

(3)ˢ�²���

��̬�洢��(Dynamic RAM)������ˢ�����⡣������Ҫ�����Զ�ˢ�·�ʽ��ÿ��һ��ʱ����SDRAM��һ��ˢ�����ˢ�¹�����ͼ4��ʾ��

3 �ӿڵ�·�����

(1)�⸴�õ�·

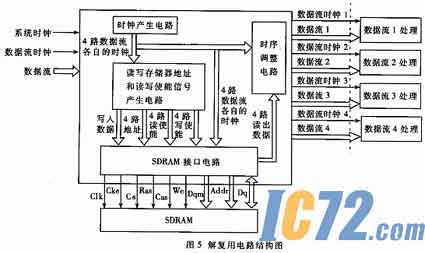

���⸴�õ�·��Ҫ��ɽ�1·�����������⸴��Ϊ4·����������ṹ��ͼ��ͼ5��ʾ��1·����������⸴��������SDRAM���壬�⸴��Ϊ4·��������

����Ҫ�⸴��Ϊ4·��������Ϊ�˳������ʱ϶��������ٵ�Ҫ����4��bank��SDRAM,��·���ݻ����Ӧ��ͬ��bank��Ϊ����ƣ�������1�Ļ�������Ϊbank0,������2�Ļ�������Ϊbank1,������3�Ļ�������Ϊbank2,������4�Ļ�������Ϊbank3������ÿ·����ʵ�������Ը����ʼ���д�룬Ȼ���Ե����ʾ��ȶ�����

���ڽ��е��ǽ⸴�ã����д�������ֻ��1·�������п���4·����ͬʱ��Ҫ���������Զ���4·�����������д��ַ�Ͷ�дʹ���ź��Ƿֿ��ġ�

(2) SDRAM�ӿڵ�·��ʱ�����

����������������Ϊ3M�ֽ�/�룬���õ�ϵͳʱ��Ϊ20�����ֽ�ʱ�ӡ�����SDRAM��ʱ��Ϊ60MHzϵͳʱ�ӡ���һ���ֽ�ʱ���ڶ�SDRAM�IJ��������5��(1�ζ���4��д)������Ϊ������ˢ�µ�Ҫ��ÿ���ֽ�ʱ�ӽ���һ��ˢ�²���������SDRAM��ʱ��Ҫ�������IJ���������ʵ�ֵġ����Ҫͨ����bank��������������ʱ�ָ�����ʵ�֡�ͼ6��������һ���ֽ�ʱ��������������1���ж�д����������3·���ݽ��ж���������������ʱ��ͼ�����Կ���ͨ����bank������ʱ�ָ��ã���20��ϵͳʱ�ӽ���������Ķ�д��������պúܽ��յ��ſ���

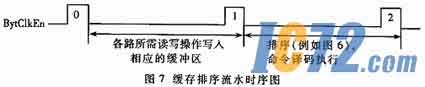

һ���ֽ�ʱ���ڶ�SDRAM��д����������ģ������������ĸ��ñ����йء�Ϊ������ʱ���������˵������Ҫ��һ���ֽ�ʱ�������ڶ�SDRAM�������������Ȼ�����źõ�˳��ִ�������������Ҫ��һ���ֽ�ʱ�������ڶ�SDRAM�IJ������л��棬Ȼ������һ���ֽ�ʱ�������ڽ���������SDRAM�������Ӧ�����������������Ӧ�Ŀ����ź��ߣ���ɲ������������������ͼ7��ʾ��

ע����������Ľ����ͼ6��

(3)SDRAM�ӿڵ�·

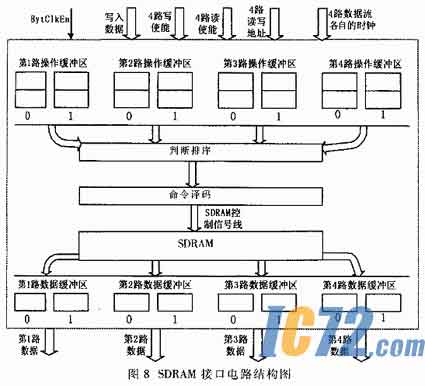

SDRAM�ӿڵ�·����Ҫר�Ų����������洢һ���ֽ�ʱ�������ڵIJ������Ա���һ�ֽ�ʱ�ӵ�����Ϊ�˷��㴦������ÿ·���ݵĻ����������(�����д)����һ���������������������������ԣ������ͬʱ��Ȼ���в���Ҫ�����ÿ·�IJ������ݻ�������Ϊ���顣��һ�黺����д��ʱ��������һ�黺�����еIJ������ݣ������������롢ִ�С������ֽ�ʱ���л��Ի������Ķ�д���Ӷ������ͻ�����ڴ�SDRAM���������ݣ�ÿ·����д����Ӧ�Ķ������ݻ�������ͬ��ÿ·�Ķ������ݻ�����Ҳ��Ϊ���飬�����ֽ�ʱ���л���д��

����һ���ֽ�ʱ�������ڣ�ÿ·����IJ��������2�Σ�ÿ·�IJ������ݻ�����ֻ��������Ԫ(ÿ����Ԫ�洢�˴˴εĶ�дʹ���źš�д�����ݡ���ַ)���ɡ����ڶ������ݻ�����������һ���ֽ�ʱ��ÿ·�������ִ��һ�ζ����������Զ������ݻ�����ֻ��Ҫһ���ֽڡ����������������С�����ȫ���üĴ�����ʵ�֣����Ƽ�

�����ӿڵ�·�Ľṹ��ͼ��ͼ8��ʾ��

4 SDRAM�ӿڵ�ʵ�ֽ��

���MT48LC8M8A2��SDRAM������ͬ����Ʒ�������Verilog HDLӲ���������Խ���ģ�ͣ��ӿڵ�·�Ѿ�����ͨ������ģΪ2100��(NAND)�������⸴�õ�·Ҳ�Ѿ�����ͨ���� |