ժҪ��������ATMEL��˾�͵�ѹAT29LVϵ�д洢���Ľṹ���ص㼰���ܡ�ͬʱ���TI��˾DSPоƬTMS320VC5402�IJ���װ�ط�ʽ��������AT29LV256��ʵ��Ӧ���е�Ӳ��ԭ��ͼ�����߱��ע�������������Ƴ���Ϊ����������AT29LV256���߱�̵Ĺؼ�����

�ؼ��ʣ�

Flash�洢����һ�ָ��ܶȡ�����ʧ�ĵ�ɲ�д�洢���������й��ĵ͡��������ٶȿ���ص㣬���ҵ�λ�洢���صļ۸�ȴ�ͳ��eProMҪ�ͣ��������Ӧ���������źŴ���ϵͳ�С�Flash �ɷ�Ϊ����Flash�ʹ���Flash������Flash����ΧоƬ���Ӽ��ɽ�Լӡ�ư�ռ䣬���洢����Խ�С�ҳɱ��ߡ�ͬʱ����ͨ���ٶȽ��������Ҳ�Ƚϸ��ӡ�����FlashоƬ����д洢�����ٶȿ졢ʹ�÷�����ŵ㡣aTMel��˾������aT29lVϵ�е͵�ѹ�洢������һ�ֲ��С������ܡ���֧��3V���߱�̵�Flash�洢������Flash��̳��˿��Բ���ר�õ�Ӳ��������ѳ��������д��Flash���⣬��������DsP�Ŀ���ϵͳͨ�����������ʵ��ͬ���Ĺ��ܡ�

TMs320VC5402(���¼��C5402)����������������˾(TI)�Ƴ���һ���Լ۱ȼ��ߵĶ��������źŴ�����(DsP)����оƬ����4k��16BITƬ������ʽroM(F000��FFFF)������4kB roM��Դ�������BooTloaDer����C5402��BooTloaDer��ϵͳ�ӵ�ʱ����ⲿԴ�����͵��ڲ��洢�����ڲ�����ռ䡣��������������ⲿ�����Ĵ洢�����������У�������������ٵ�DraM�洢�������У��Ӷ�����С�˶�C5402�ڲ���Ĥ����Ҫ�������˵�·����Ƴɱ���

�����ڱ���ʵ��ʹ�þ���Ļ����ϣ���ϸ������aT29lV256��C5402��������װ��ģʽ�µ�������̼����������˲���װ�ص���������ϵͳ��Ӳ����ƣ���������Ƴ���Ϊ�������˶�aT29lV256���ʱ�ľ��岽�輰������

1 aT29lV256��̼���

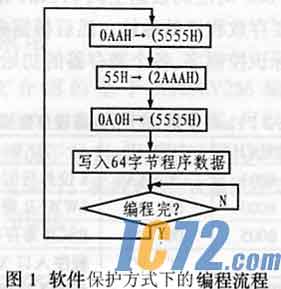

aT29lV256��aTMel��˾����������Ϊ32k��8BIT����֧��3V��ϵͳ��̵�Flash�洢����aT29lV256���洢�ռ�ֳ�512��������������ÿ��������64���ֽڣ�����a6��a14����ѡ��������ַ��a0��a5ѡ���ֽڵ�ַ��ÿ�������ı�̲������Ҫ20Ms�������������һ���sraM��ͬ��ʱ��Ϊ70ns ��aT29lV256�ڱ��֮ǰ��Ƭ�ڶ�Ӧ�������Զ��������������Ҫ����IJ������ͬʱ��оƬ���ṩ������������������������ɶ���Ƭ�IJ���������Ƭ�����������1���С�

��1 AT29LV256ȫƬ��������

| �� �� |

1st |

2nd |

3rd |

4th |

5th |

6th |

| �� ַ |

5555H |

2AAAH |

5555H |

5555H |

2AAAH |

5555H |

| ������ |

5555h |

AAh |

2AAAh |

55h |

5555h |

90h |

aT29lV256�ı�̲�����������Ϊ��λ���еġ����ڲ���64�ֽڵ����ݻ����������д�뻺�������ֽ�������64�ֽڣ�����ʱ�Զ���δд����ֽڲ���ΪFFh��һ��ijһ�����е��ֽڱ�װ�룬��Щ�ֽڽ�ͬʱ���ڲ����ʱ����б�̣���ʱ��������װ�룬��������ȷ�������ݡ�ÿһ����װ�ص�������Ҫ����̣�������we�ɸߵ��͵����䣬��һ������Ҫ��150��s����ɣ��������150��s���������Զ����������ڲ���̷�ʽ��Ϊ�˷�ֹ����ı�̲�����aT29lV256�ṩ������������̹��ܣ��ڶ�Flash ��ÿ���������б��ʱ�������Ƚ�3����������ȷ��д�뵽��Ӧ�ĵ�ַ��Ԫ��Ȼ�������Ƭ�ڱ�д�����ڶ�ÿһ���������֮ǰ����Ҫִ����ͬ�����ֽ�ָ�����У���������������̵ľ���������ͼ1��ʾ��

ͨ��aT29lV256�ṩ����Ӳ��������ʶ��оƬ��ϵ�кź��ͺš�����ͼ2˳��д������ֺ��ɶ�����Ʒʶ����1F������ʶ����BC������ʶ����ɺ����迪ʼ��д������Ӧ�˳�����ʶ�𣬲���ʱ20Ms��Ϊ�˼�С��̵ĵȴ�ʱ�䣬aT29lV256������������ּ���������Ƿ�����ķ�ʽ��

(1) ѭ����ⷽʽ���÷�ʽ���ȶ���д�뱾�������һ����Ԫ�����ݣ�����I/o7λ��д��õ�Ԫ��ʵֵ�ķ��룬������������û�н�������Ϊʵ��ֵ���������̽�����

(2) ���I/o6��ʽ���÷�ʽ����������ڼ佫�����������ⵥԪ��ַ�����ݣ���I/o6����������ʱ״̬��һ����˵�����û�н���������ͬ���������������Ѿ�������

2 C5402��������װ��ģʽ

C5402�ϵ��ͨ�����ȼ��MP/MC���ŵ�״̬�����Ϊ�ߵ�ƽ��˵��DsP��������������ģʽ����ʱ��ɴ��ⲿ����洢��0FF80h��ַ����ʼִ���û�������Ϊ�͵�ƽ��˵��DsP������Ϊ�����ģʽ����ʱ���Ƭ��roM��0FF80h��ַ��ʼִ�г������⣬��C5402��0FF80h��ַ�������һ����ת��0F800h��ִ��DsP��������װ��(BooTloaDer)�����ָ�

��C5402ִ��BooTloaDer����ʱ�����ᰴhPI����װ��ģʽ������eeProM����װ��ģʽ����������װ��ģʽ�������п�����װ��ģʽ��I/o������װ��ģʽ��˳��ѭ����⣬�Ծ���ִ����������ģʽ��

C5402�IJ�������װ��ģʽ�ǽ�����������ݴ����eeProM��Flash����ӦDsP����Ѱַ���м��ص�Ƭ��DaraM��ϵͳ����չ�洢��sraM�ڡ�����C5402��������Ѱַ��Χ���Ϊ64k �� ����ˢ��ڲ����б�дBooTloaDer���������£���������װ��ģʽ���ֻ��װ��32k�ֵij�������ݡ����������ݴ���32kʱ���ɽ��Լ���д�IJ���װ���ں˳���ͨ��Ƭ��װ�س����͵�Ƭ��DraM�У�Ȼ��������ת���ں˳����Խ�����32k�ֵij��������͵�Ƭ��sraM�С�

�����ò���װ��ģʽ�Գ�����м��أ���Ӧ���ݲ���װ�صĸ�ʽ������Flash�ij������ݴ洢�ռ䡣������DsP��Ӧ�����ݿռ�FFFeh��FFFFh��ַ��д��Ҫ��ų���ĵ�ַ��Ȼ����ݲ���װ�ص�����������ʶ�����֡������Ĵ����ij�ʼ��ֵ��װ�غ����ʼ���е�ַ������εĴ�С��װ�ص�ַ����д��Flash�Ĵ�ų����ַ�У������д������д�ij���2������Flash�еIJ�������Դ�����������������εĴ�С�Լ���ʼ���е�ַ�ɸ���ϵͳ����ʱ���ɵģ�MaP�ļ���ȷ����

��2 Flash�еIJ�������Դ����������

| ��������ַ��H�� |

���ݣ�H�� |

�� �� |

| 8000 8001 |

08 AA |

8λ����������־ |

| 8002 8003 |

88 06 |

SWWSR�Ĵ�����ֵ |

| 8004 8005 |

00 00 |

BSCR�Ĵ�����ֵ |

| 8006 8007 |

00 00 |

�������XPC |

| 8008 8009 |

00 80 |

������ڵ�ַ |

| 800A 800B |

00 0B |

������ |

| 800C 800D |

00 00 |

���Ŀ��XPC |

| 800E 800F |

00 80 |

���Ŀ���ַ |

| 8010 8011 |

F6 BD |

�������1 |

| ���� |

���� |

���� |

| 801F 801F |

FC 00 |

�������N |

| 8020 8021 |

00 00 |

����������־ |

| ���� |

���� |

���� |

| FFFE FFFF |

80 00 |

����洢��ַ |

3 ����aT29lV256��DsP��Ӳ�����

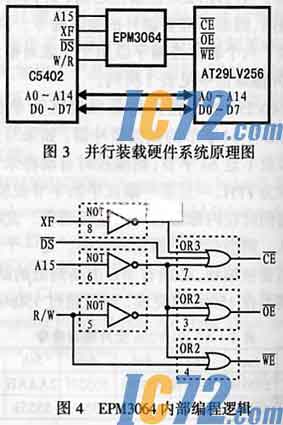

������aT29lV256��C5402��ɵ�Ӳ��ϵͳΪ����Flash�ڲ���װ��ģʽ�е�Ӧ�ý�����ϸ˵������Ӳ��ϵͳԭ����ͼ��ͼ3��ʾ����ΪaT29lV256Ϊ32k��8BIT�洢������˲���Ҫ��չ�ⲿsraM����ϵͳ����alTera��˾��ePM3064�����C5402��aT29lV256֮�����ת����ePM3064�ڲ��ı������ͼ4��ʾ��

��C5402�ϵ縴λװ��ʱ������BooTloaDer�����ڳ�ʼ��ʱ����F������Ϊ�ߵ�ƽ����ˣ�C5402����ͨ��ePM3064�ܵ�������aT29lV256 08000h��0FFFFh��Ԫ�е����ݶ���C5402��Ӧ��0000h��3FFFhѰַ����Ƭ��DaraM�С���ϵͳ���벢������װ��ģʽ��C5402�������ѰַΪ0FFFFh�ĵ�Ԫ(a15��1��ѡ��Flash)�ж�ȡ��Ҫ����ij���洢������ַ��Ȼ��ӳ���洢��ַ������ʶ�����֡������Ĵ����ij�ʼ��ֵ��װ�غ����ʼ���е�ַ������εĴ�С�Լ�װ�ص�ַ����װ�ص�Ƭ��DraM�С���ePM3064��������ʹ�ã�F��Ϊ����BooTloaD֮���ͷ�Flash��ռ�õ����ݿռ䡣������������ĵ�һ�����ΪrsB�� ��F��Ҳ�����ã�F����Ϊ�͵�ƽʱ��Ce�����Ƭѡ��Ч�źţ��Ӷ������ó����ݿռ䡣

4ϵͳ�������

��ϵͳ������̵ĺ������ڰ��ղ���װ����������ʽ��Flash���б�̡���������aT29lV256��дһ�������Ƴ���Ϊ����˵����Flash�����������ʱӦע�������ؼ����衣

�������£�

��MMregs

��DaTa

kaIshI: ��worD 08aah,7FFFh,8806h,0000h,0080h,000Bh,0000h,0080h ;����װ���������еĸ����ݲ���

��gloBal_C_InT00

��Te��T

��C��InT00: �����ﻹӦ�б�Ҫ�ij�ʼ��

sTM #100h,ar1

sTM #0FFFeh,ar2 ����8000��ڵ�ַд��FFFeh��FFFFh��

sT #8000h,*ar1

Call Prog0 ����ʼ��д��Ҫ��д��������

Call Prog1 ����16λ���ݷֳ�����8λ��д��Flash��

sTM #kaIshI,ar1 ��������������������д��8000h��ʼ�ĵ�Ԫ

sTM #8000h,ar2

sTM #07h,BrC

rPTB looPa

Call Prog1

looPa: noP

sTM #qq,ar1 �������Ƴ������ݽ��Ų��в�����д��Flash��

sTM #0Bh,Br �������СΪ0Bh

rPTB looPB

Call Prog1 ����Ϊ�ܹ���дû����64�ֽڣ���˲���ִ��������

loooPB: noP��Prog0Ϊ��������ģʽ��д�������ӳ���ÿ���64�ֽ�ִ��һ��

Prog0: sTM #0D555h,ar3

sT #0aah,*ar3

sTM #0aaaah,ar3

sT #55h,*ar3

sTM #0D555h,ar3

sT #0a0h,*ar3

reT�� Prog1Ϊ16λ���ֳ�8λ������д�ӳ���

Prog1: lD *ar1,��8,a

anD #0FFh,a

sTl a,*ar2��

lD *ar1��,a

anD #0FFh,a

sTl a,*ar2��

reT������һС��Ϊ���Ƴ���ͨ�����ã�F���ŵĸߵ͵�ƽ��ʹ����˸��

��seCT ��Cheng������

qq�� rsB�� ��F

rPT #0FFFFh

noP

ssB�� ��F

B qq

reT

��enD

5��������

���Ľ��ܵĻ���aT29lV256��̼�����TMs320VC5402��������װ�ط�����������û��ר����д��������¶�Flash���б�̣��Ӷ�ʵ����DsP���ѻ��������С�ʵ����������ϵͳ�ȶ��ɿ������нϸߵ�Ӧ�ü�ֵ�� |