������

�ԣͣӣ������֣ã����������������������¼�ƣ֣ã����������ǣԣɹ�˾�Ƴ���һ��˫�˶���ģӣ�оƬ����ӵ�������ģӣ���ϵͳ��ÿ����ϵͳ����һ���ģӣкˣ����Ҿ��ж��������ݺͳ���洢�ռ䣬���Խ�������֮���ͨ�ţ�����������ϵͳ����һ��Ƭ�����ߡ����⣬ÿ����ϵͳ����ӵ�У��� ���������ֵ�Ƭ�ڣңϣͣ����洢�У£��������������ģӣ�оƬ�ϵ��λʱ�������ģӣк˿ɷֱ��������������ģ£���������������ʵ���û�������ϵ��Ծ١�

˫�ˣģӣ��������͵��ˣģӣ���������ʵ�ַ����нϴ�IJ����һ���ڣģӣ�ϵͳ�������Ҫ�ر�ע�⡣���Ķ�˫�ˣģӣ�оƬ�֣ã�������������ģʽ����������ķ������о���������ʹ�ã���λ��������ģʽ����˫�ˣģӣ�������ʵ�ַ�����

�� �ԣͣӣ������֣ã��������ģ£���ģʽ

�֣ã����������ṩ����λ������������λ���������ʹ��УţţУңϣ����������֣£���ģʽ��ʵ���û�������ϵ��Ծ١�

���У���λ��������ģʽ��ͨ��Ƭ��洢���ӿڣ��ţͣɣƣ��ԣģͣ���ʽ������ӣ����������ֿ���Ƭ�����ݴ洢�����Ƶ�Ƭ�ڳ���洢�ռ䣻

��λ��������ģʽ����ͨ��Ƭ��洢���ӿڣ��ţͣɣƣ��ԣģͣ���ʽ������ӣ��������ֿ���Ƭ�����ݴ洢�����Ƶ�Ƭ�ڵij���洢�ռ䣻

�����УţţУңϣ�����ģʽ��Ҫ��ͨ����ͨ�����崮�ڣ����ͣ�£ӣ� ���������豸�а��ƴ��벢ʵ���ϵ��Ծ١�

�ͣ���ϵ��������оƬ��ͬ���ǣ��֣ã�������Ƭ�ڣңϣ��еģ£�������������֧�֣ȣУɡ����Уɣ��Ϻͱ�����ģʽ����������ʽ��������֧�ֵ����֣����ģʽ�У�����λ��������ģʽ����õġ����Ķ�����ģʽ���������������������ʹ�ø�ģʽ����˫�ˣģӣг��������ķ�������ͨ��ʵ����֤�˸÷�������ȷ�ԡ�

������ ��������ģʽ��ѡ��

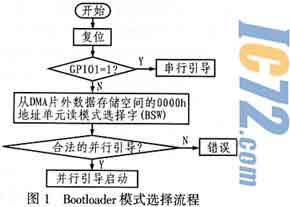

�֣ã��������������ģӣк��ڣģӣ�оƬ�ϵ��λʱ������������ģʽʵ���ϵ��Ծ٣���Ҫ�������˵Ĺ������ţأɣϺ��ԵģǣУɣϣ����ңϣͣţΡ��ǣУɣϣ����ž��������أɣ�Ϊ�����͵�ƽ��ʱ�������ӣңϣ�������Ҳ����˵������ʹ�ã֣ã�������Ƭ�ڣңϣ��еģ£�������������ʵ���ϵ������������ãȣУ�ģʽʵ���ϵ��Ծ٣����أɣ�Ϊ�����ߵ�ƽ�����ǣУɣϣ����ңϣͣţ�Ϊ��ʱ����ʹ��Ƭ��洢�����û��Լ���д�ģ£�������������ʵ���ϵ��Ծ٣����أɣ�Ϊ���� �ǣУɣϣ��ңϣͣţ�Ϊ���� �ǣУɣϣ�Ϊ����ʱ�����ֱ�ʹ�ò��л��ߴ�������ģʽʵ���ϵ��Ծ١���ˣ���ʵʩ��Ӧ���ϵ��Ծ�ǰ�����뽫����״̬������ȷ���Ա�֤�£�������������Ԥ����ģʽִ�С��£����������ģʽ��ѡ�����̼�ͼ����

���£����������������������ģʽʱ�������ԣģͣ���ʽ��Ƭ�����ݴ洢���ģ��������赥Ԫȡ��ģʽѡ���֣��£ӣף�����һ�������ǣ�λ���ǣ���λ�IJ�������ģʽ��������������ζ��ѡ���ˣ���λ��������ģʽ�������ѡ��λ��������ģʽ��ȡ���������ֽڽ��ǣ�����ͣ����衣֮�����գ£��������м��ء�

������ ����λ��������ģʽ�ģ£�����

�£�������������Ҫ���ƵĴ��������֯��һ���ĸ�ʽ������ǣ£�����������λ��������ģʽ�ģ£�������������С�

��1 16λ���е�ģʽBoot��

���⣬��Ҫע����ǣ������ڶ��������ж�����תָ���ѭ��ָ����ԣ��£������еij�����ڵ�ַ����ͳ���ģ�����ļ��з���ĵ�ַ����һ�£�Ҳ����˵�����ڣãã��н��е���ʱ���������̣��䵽���������裬�£������еij�����ڵ�ַ��Ӧ���ǣ��������衣

������ �£�����������

�£��������ɣ�����������ʽת���������ɣ�Ҳ�����Լ���дһ���ļ���ʽת���������ѣ�������ļ�ת����������ļ���ʽ�������ͨ����дһ���ã�������������������ļ�ת���ɣ������ļ���Ȼ�������ļ��Ŀ�ʼ��������Ӧ�ı�־λ�ͼĴ��������֣��Ӷ��γ������ģ£�������

�� �֣ã�������Ƭ�����߳�ͻ�Ľ������

���ڣ֣ã���������˫�ˣģӣУ�ÿ�����и��ԵĴ洢�ռ�ͣ£����������������˹���һ��Ƭ�����ߺ�һ���أɣ����š������������˵ĸ�λ���ţ��ߣңӺͣ£ߣң�ͬʱ�յ���λ�͵�ƽ�ź�ʱ����ͬʱ����Ƭ�����ߵĿ���Ȩ��������������Ƭ�����ߵij�ͻ�����ң£����������������Ǽ��ú���û��Ƭ�����ߵĿ���Ȩ�����û�У���ѭ�����ֱ��ȡ��Ƭ�����ߵĿ���Ȩ��Ϊ�˱�����������ķ�����Ӧ���Ժ�����˳����������ϵ硣

���ڣ֣ã��������У��˴�����������ʱ��Ƶ�ʵ������·������Ӧ���ȶԣ��˽��и�λ�����������ˣ�Ȼ�����ã��˵��û����������ƣº˵ĸ�λ����ʵ�������˵�������

����ϵͳ��Ҫ�������ʹ�ã�������ṫ˾�ģãУ̣�оƬ���������ֿ����źš����·����ʾ��ͼ��ͼ����ʾ�����˵ĸ�λ�źţ��ߣң��ɣãУ̣�оƬֱ�Ӹ���������ϵͳ�ϵ��λ��ͬʱ�ԣ��˽��и�λ�����º˵ĸ�λ�źţ£ߣң���ͨ���ãУ̣�ӳ�䵽�ģӣеģɣ��Ͽռ䣰���������ַ��Ԫ�ĵڣ�λ���º˸�λ����λ����ϵͳ��λ��ֵΪ������ͼ����ʾ���ڣ���������ͨ���û�����д�£ߣң�λ��Ϊ�º��ṩ��λ�źš�

�� �֣ã��������IJ�����������������

������ �û�����İ���

�����ģӣк�Ҫ��ɸ��ԵĹ��ܣ�ִ�е��û������Dz�����ͬ�ģ����ң��˵��û�����Ҫ���ƣº˵ĸ�λ����������ģӣк˵ģ£����������Dz�ͬ�ġ��ɣģͣ���ʽ�ڲ��洢��ͼ��֪������ռ�ĵڣ�ҳ�͵ڣ�ҳ���ڣ��ˣ��ڣ�ҳ�͵ڣ�ҳ���ڣºˡ���ˣ���Ҫע����ǣ����£�����������������û�����ʱ�����˵��û�����Ҫ�����Ƶ��ڲ�����ռ�ĵڣ�ҳ�ϣ����º˵��û�������Ҫ�����Ƶ��ڣ�ҳ�ϡ����ǣºˣ£������еij�����ڣأУú�Ŀ�ģأУ�Ӧ�����óɣ��������衣

������ �£������ķ���

��ϵͳ�ã��ͣ���������������������ƣ̣��ӣ������ӣӣԣ����֣ƣ���������ΪƬ�����ݴ洢����ҳѡ�ź��ɣģӣ�ͨ���ãУ̣ĸ���������ӳ�䵽�ģӣ��Уɣ��Ͽռ�ģ����������ַ��Ԫ�ĵͣ�λ��ϵͳ��λ��λ��Ϊ�������ڣ�ҳ������ͼ����ʾ�����⣬�˵�ַ��Ԫ�ĵڣ�λ���ãƣ�λ���ǿ��ƣƣ̣��ӣ�ӳ�������λ�����ãƣ�Ϊ��ʱ���ƣ̣��ӣȱ�ӳ�䵽�ģͣ�Ƭ�����ݿռ�ģ��������裬��ʱ���£�����������������ԣģͣ���ʽ�ӣƣ̣��ӣ��а������ݲ����������������ãƣ�Ϊ��ʱ���ƣ̣��ӣȱ�ӳ�䵽�ãУ�Ƭ�����ݿռ�ģ��������裬����������£�����ͨ��������ƣ̣��ӣ�����д���ݡ���ˣ���һλ��ϵͳ�ϵ��λ�����óɣ�����ʹ�����ܹ�˳��������

���������ģӣк˵ģ£��������ݲ�ͬ����Ӧ�ӣ£������Ĵ�С���������£������ŵ��ƣ̣��ӣȵIJ�ͬҳ�ϣ��Ա�������˷ֱ�ʵ������������ƽ����˵ģ£������ŵ��ڣ�ҳ�����º˵ģ£������ŵ��ڣ�ҳ��

������ �����߿���Ȩ���ͷ�

��ͼ����ʾ���ڣǣУɣϿ��ƼĴ�������ַ���ã裩�У��أɣϣߣǣң��Σ�λΪ��������Ӧ�ģģӣк�ȡ����Ƭ�����ߵĿ���Ȩ�����ڻ�û��ȡ�ÿ���Ȩ���أɣϣߣǣң��Σ�λΪ������������Ƭ�����ߵĿ���Ȩʱ����Ӧ�ģأɣϣߣңţ�λӦ��Ϊ�����ãϣңţߣӣţ�λ���ڱ�ʾ�������ĸ��������У����ڣãУ� ��������ʱ�������˵ģǣУɣϿ��ƼĴ����ģãϣңţߣӣţ�λ�����ص�������������ͬһ�������ڣãУ� ��������ʱ�����º˵ģǣУɣϿ��ƼĴ����ģãϣңţߣӣţ�λ�����ص����������йأǣУɣϿ��ƼĴ������������λ�����ʱ�ɲ����йصIJο����ף���

������ �ƣ̣��ӣȵ���д

���߸��ݣӣӣԣ����֣ƣ������������ϱ�д��һ���ģӣг��ó����ͬʱ�����˵ģ£�������д���ƣ̣��ӣȵĵڣ�ҳ�������º˵ģ£�������д���ڣ�ҳ��

��ϵͳ�ϵ��λ���������������ģ£���-����������ʱ�ƣ̣��ӣȵĵڣ�ҳӳ�䵽�ģͣ�Ƭ�����ݿռ�ģ����������ַ��Ԫ��������������ִ���û������û��������Ƚ�ҳѡ���óɵڣ�ҳ���������ƣ̣��ӣȵĵ�һҳ����ӳ�䵽�ģͣ�Ƭ�����ݿռ�ģ��������裻Ȼ�����ͷ�Ƭ�����߿���Ȩ�������º˷�����λ�źţ���ʱ����ֻ�Уº˸�λ���ң������ͷ�Ƭ�����ߵĿ���Ȩ����ˣ��º˽����뵽Ƭ�����߿���Ȩ��ͬʱִ�У£����������������������������ģӣ�������������������������ͼ��ͼ����ʾ�������ǣ��˵��������Գ�����룺

*���������

*�������� ��������̣ţģ���

*������� ������

*�������

��������������������������

����� ����� ������������,������������ ;����ҳѡ�ź�

������� �����������,������

����� ������

����� �����������,����� ;�ͷ�Ƭ������

����� ������ ; ����Ȩ

����� ���������������������������� ;���º˸�λ�ź�

������� ������������,���������� ������

����� ��������������,������������

������� ������������,������

������: ����� ��,���� ;�����������

����� ������

����� ��,���� ;�����������

����� ������

�� ������

;���������ӣ������������ ���� ������ ���� ������ ������壭������

������: ����� ������,���

�����: ����� ������������,���

�����: ����

����� �����,�����

����� �����,�����

����

�� ʵ����֤

������У��ڣģӣеģ��ߣأƺͣ£ߣأƽ�������������������ܣ�ͬʱʹ�����ص��û�����ͨ��ѭ�������ã����������������ʹ��������������Բ�ͬ��Ƶ����˸���Դ�����֤�û������Ƿ�ɹ����ء�ϵͳ�ϵ����������������Ⱥ��Բ�ͬ��Ƶ�ʿ�ʼ��˸��˵���ģӣеģ��ˡ��º˾��ɹ���ʵ�����ϵ��Ծ١�

|