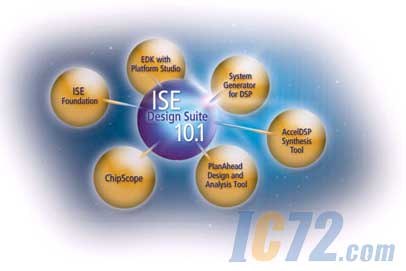

Xilinx,推出其ISE Design Suite10.1版。这一统一的整体解决方案为FPGA逻辑、嵌入式和DSP设计人员提供了赛灵思的整个设计工具产品线,其中的设计工具具有完全的互操作能力。ISE Design Suite 10.1版以平均运行速度快两倍的特性极大地加快了设计实施速度。因此设计人员可以在一天时间里完成多次反复设计。今天的发布另外一个重要意义就是新版本采用了SmartXplorer 技术, 这一技术专门为解决设计人员所面临的时序收敛和生产力这两大艰巨挑战而开发。SmartXplorer技术支持在多台Linux主机上进行分布式处理,可在一天时间里完成更多次实施过程。通过利用分布式处理和多种实施策略,性能可以提升多达38%。SmartXplorer技术同时还为用户利用独立的时序报告监控每个运行实例提供相应的工具。

PlanAhead Lite和基于策略的实施方法实现终极生产力

ISE Foundation中PlanAhead Lite工具的应用,为用户提供了屡获殊荣的PlanAhead设计和分析工具所拥有的强大布局规划和分析功能的一个子集。免费提供的PlanAhead Lite采用了革命性的PinAhead技术。这一直观的解决方案旨在简化管理目标FPGA和PCB之间接口的复杂性。PinAhead技术支持在设计较早阶段智能实现引脚定义,从而避免了通常在设计后期发生的与引脚布局相关的修改。这种修改过去通常必须通过交互式引脚布局才能完成设计规模检查。在PinAhead工具中,引脚分配完成后,还可以使用逗号分割值(CSV)文件或通过VHDL或Verilog头文件输出I/O端口信息。

ISE Design Suite10.1的推出还进一步简化了确定最优实现设置的过程。现在设计人员还可规定和设置自己独特的设计目标,可以是性能最大、优化器件利用、降低动态功耗、或者是实施时间最短。利用这一资源面积优化策略,逻辑资源利用情况平均可节约10%。

广泛联合提供更好的验证能力

ISE Design Suite 10.1还同时受益于赛灵思公司与业界领先的EDA供应商之一Mentor Graphics公司的联合协作。通过使用IEEE IP加密模型,ISE Design Suite 10.1的运行速度最快可达原来的两倍。新的性能优化BRAM, DSP和 FIFO仿真模型进一步将RTL仿真运行时间缩短了一倍。

第二代XPower提供更强的功率分析和优化功能

业界研究表明,满足功率预算是FPGA设计人员面临的一项越来越大的挑战,特别是工艺几何尺寸的不断缩小进一步加剧了这一问题。ISE Design Suite 10.1为用户提供了在设计过程中尽早分析功率要求的功能,同时还可以在设计过程中优化动态功率。

第二代XPower功率分析工具提供了改善的用户接口,按照模块、结构层次、电源轨和使用的资源分析功率更为容易,因此进一步增强了功率估算功能。信息可以文本和HTML报告格式给出。与其它逻辑供应商提供的静态估算网页相比,这是一项巨大进步,同时在提供准确的功耗信息方面是一个飞跃。

ISE Design Suite 10.1提供了便捷全面的功率优化功能。利用集成的"功率优化设计目标"功能,用户可以简单地一步完成功率优化流程。通过映射和布局布线算法的改进,对于采用65nm Virtex-5器件和Spartan?-3 Generation FPGA的设计动态功率平均可降低10%和12%。

嵌入式设计和DSP设计工具集成

为帮助用户更快速地实现优化嵌入式和DSP设计,ISE Design Suite 10.1 还对赛灵思嵌入式和DSP工具进行了进一步的易用性改进。例如统一的互操作性保证了用户可以在ISE Design Suite 10.1 容易地增添System Generator模块。EDK 和 System Generator for DSP技术之间不同工具的集成得到进一步增强,从而能够为同时涉及嵌入式和信号处理的更复杂FPGA SoC设计提供支持。

价格和供货情况

ISE Design Suite 10.1 包括 ISE Foundation、嵌入式开发套件 (EDK)、System Generator for DSP、 AccelDSPs综合工具、ChipScope Pro 分析仪和ChipScope Pro Serial I/O 工具、 PlanAhead设计和分析工具以及ISE仿真器。用户可以通过购买DVD或网络下载方式安装领域专用的DSP、嵌入式和逻辑设计产品。利用电子交付流程做为主要的产品提供方法,因此用户不仅可以获得所购买的产品,还可以快速获得赛灵思其它设计工具的评估版本。

ISE Design Suite 10.1中的所有产品立即可以提供,价格从495美元至 2495美元不等。

|