ASIC和SoC器件成本的逐步上升迫使半导体供应商必须进一步开拓各个器件的市场以寻求满意的投资回报。

日益增长的软件使用为此提供了有效的机制,因为增加的软件内容等同于更多的功能和软件变化提供了特定市场产品的差异化。这种趋势致使上百万行软件代码在ASIC或SoC中出现也就不足为奇了。多内核的使用增长致使在这些器件中使用的软件数量大幅飚升,也提高了它们的复杂性。那么,软件含量增多的趋向对整个设计过程意味着什么呢?

软件复杂度的提高意味着如果想要实现产品的上市时间目标就必须更早地着手软件开发。由于软件复杂度对全新应用来说非常高,开发过程可能超过18个月,因此要在芯片量产前就着手软件的开发,如果等到硬件开发出来就为时已晚。

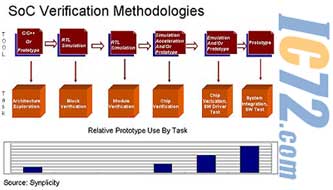

基于FPGA的原型是一种理想的软件开发平台,因为它们运行软件的速度至少要比模拟和仿真等其它验证技术快10倍。虽然各种可供选择的验证技术在验证流程中都占有各自的位置(见图1),但只有FPGA原型才具备足够快的速度训练非常复杂的软件程序和操作系统。最佳的系统集成和软件测试要求速度在10MHz-50MHz以上,100MHz则更佳。而只有FPGA原型方案能达到这样的速度,这也是它们应用越来越广泛的原因。

具备更低成本是FPGA原型设计使用增长的另一个关键原因。如今,一个复杂的SoC需要投入100-200个软件开发人员已经是很常见的事。由于FPGA原型既是低成本又是可部署的,因此可分配给软件开发小组的各位成员。这意味着软件开发小组的大部分成员无论身在何处都可以比其它方法提前几个月组织并运转起来。

软硬件的集成是一个艰辛的过程。设计小组必须确保所有规格按原计划得以执行。而这通常要等硬件设计通过彻底的测试并确信没有程序错误才可以开始。然而,即使经过了大量验证,当软硬件集成到一起时,那些难以查找的程序错误最终还是会出现。复杂SoC中的程序错误会深藏在系统中,并以不确定的方式表现出来,这是因为硬件和软件之间存在复杂而无法预料的相互作用。简单地检测这些缺陷需要特别长和耗时的测试序列,这对于较慢的验证方法是不切实际的。而且,一旦问题出现,实际的设计调试也需要花费大量的时间和精力。新的原型调试方法,如Synplicity公司的TotalRecall完全可视技术,可以通过捕获针对难以查找的程序错误而开发的测试平台而充分简化这些工作,以致能在仿真器中重现这些程序错误。

图1:SoC验证方法论的主要相关任务以及在每项任务范围内原型设计的使用率。

FPGA原型还有一个有趣而强大且与设计验证无关的应用,就是它们可以在设计初期用于架构探究(architectural exploration)。例如,架构设计师可能想要探究DSP或图形算法以观察使用不同算法或不同实现方式时候系统性能的变化。在这种情况下,为了评估架构变化对视频图形算法的影响,需要一定的硬件性能。使用FPGA原型设计,架构师就可以在设计早期就完成架构探究,以确保在实现SoC性能之前作出有效的选择。

通过与用户和供应商的交流以及对用户的调查,Synplicity公司估计有超过90%的SoC和ASIC在用FPGA做原型。对ASIC和SoC原型的这种需求正在呈两位数增长,而且据市场调研公司Gary Smith EDA对业界多内核使用的预测,这一趋势将会继续下去。

尽管有这些优点,但FPGA原型设计并不能替代其它验证方法,而是对一些现有技术的重要补充。事实上,更好地集成全套验证技术将成为未来开发的主要方法。Synplicity公司利用TotalRecall技术集成了原型调试和仿真就是在这一方向上迈出的第一步,但还有更多的事情要做。例如,还需要加快原型开发并使它易于修改。最终目的是建立一个能让设计师快速工作、快速调试、无时延更改的环境。在这个新时代,FPGA原型设计将与其它验证技术一样重要。“实速”(at-speed)运行能力,即以硬件一样快的速度执行测试,将是SoC验证不可或缺的一部分。只有这样,设计师才能应对不断提高的器件和软件复杂性所带来的新兴挑战。

|