╧Хп╬ф╛╪╪йУ╣дЇикыЇ╒у╧╦ЬSOCиХ╪фЄЬюЄпб╣днё╩З║ён╙ак╠ёЁж╡ЗфЇ╣д╬╨уЫаі,пб╣дм╗пе╡ЗфЇ║╒оШЇя╡ЗфЇ╨м╪фкЦ╩З╡ЗфЇиХ╪ф╠ьпКтз╧ідэ║╒©и©©пт╨мЄЬ©МЇҐцФспотжЬтЖЁє,ІЬтзЁи╠╬╨м╧і╨дЇҐцФспотжЬ╣добҐ╣║ё

сКЄкм╛й╠,п╬ф╛иХ╪фхкт╠цФаы╣дя╧аійгтзхурФ╪Уиы╣дй╠╪ДдзиХ╪ф©╙Ї╒╦ЭІЮ╣д╦Єтсс╡╪Чо╣мЁ║ёЁЩЇгр╣ҐГтзSOCиХ╪фЇҐцФ╡их║р╩жж╦Э╪ссппї╨м╦Э╪саИ╩Н╣дЇҐЇ╗,ЇЯтРмІвй╩ь╠╗уо╟ґІтпМІЮ╡ЗфЇюЄк╣╬м╪Рж╠л╚╦ъак║ё╟К╣╪лЕиХ╪ф╨м╣Гвс╡ЗфЇЇ╒цВ╣дх╚гРпт╡ҐЇ╔Ґ╚╩АЇе╩╨║ё

SOCиХ╪фмеІс╩АцФаыр╩о╣апяо╬Ч╣длТуҐё╨

иХ╪фЇҐцФ╣де╛аіё╨Ітсз╧ФдёесЄС╣дSOC,тзиХ╪фЇҐцФкЫ╦ІЁЖ╣де╛೥╚йг╬чЄС╣д║ёкФвеиХ╪фдё©И╠Д╣ц╦Э╪с╦Єтс,╩ЫсзVerilog╨мVHDL╣дбъ╪ґиХ╪фҐ╚╩А╣ґЁЖжВаВиХ╪фЇҐЇ╗║ё

яИжєЇҐцФ╣дюїдяё╨╣Дпмбъ╪ґдё©И╣д╦ЄтсІх╠хцейЩ╣дтЖЁє╩А╦Э╪ся╦кы,рРЄкиХ╪фжпг╠тз╣дх╠ощйЩа©р╡╩Ая╦кылА╦ъ║ёиХ╪фмеІс╣д╠╗╦Ф╠МцВ70ё╔╣д©╙Ї╒й╠╪ДсцсзІткШцг╣диХ╪фҐЬппяИжє║ё

ееЁЩиХ╪фх╠ощ╣дЁи╠╬ё╨иХ╪фмеІстҐЄС,NREЇясцтҐ╦ъ,юШхС╨мйпЁ║ЇщІНкПйї╬мтҐЄС,уБІ╪й╧╠эцБиХ╪фх╠ощ╣дЁи╠╬╠Д╣ц╡╩©ихлйэ║ё

с╡╪Ч/хМ╪Ч╪╞Ёий╠╪Джм╨Сё╨вВн╙о╣мЁ©╙Ї╒╧ЩЁл╣двН╨Ср╩╡Ґ,хМ╪Ч╪╞Ёим╗Ёёй╧╣цуШ╦Ж©╙Ї╒╪ф╩╝ясЁы║ёІтсзпб╣д╡ЗфЇ©╙Ї╒╧єЁлІЬят,с╡╪Ч/хМ╪ЧяИжє╣джм╨Сйгр╩╦Ж╪╚ЄСЇГоу║ё

╠Йв╪╣д╠Д╩╞╪╟фД╦Єтсптё╨р╣ҐГ╠Йв╪╠Д╩╞╣дЄнйЩ║╒╦ЄтсІх╨мЇясц╠╛у╗пт╣дтЖЁєй╧╣цожсп╣диХ╪фЇҐЇ╗╨мдё©И╧╧Ґ╗╪╪йУ╠Д╣ц╧Щй╠ак║ёр╩п╘пб╣д╦Єтс╠Йв╪р╙гС╦ЭЄС╣д╪фкЦмлмба©║ё

╬║╧эм╗сцЄіюМфВдэ╧╩ЄіюМпМІЮхннЯ,╣╚йгкЭцгм╗Ёёх╠иыжЄпп╦ЄтсйЩ╬щЄіюМхннЯкЫпХр╙╣дЄЬ©М,юЩхГмЬбГйЩ╬щ╟ЭЄіюМ║╒йсф╣ЄіюМ╨м╪сцэ║ёп╬ф╛иХ╪фхкт╠©ймШм╗╧Щс╡оъбъ╪ґюЄй╣ожуБп╘╧ь╪Э╧ідэ║ё

діІШІ╗би = ╩З╩А + ЇГоу

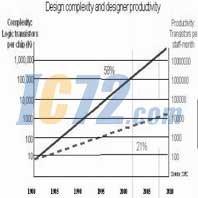

╦Й╣гдіІШтз1965дЙтЬтє╡Б╣Ґ╪╞Ёи╣ГбЇ╣дцэІхҐ╚ц©ЄСт╪р╩╣ҐаҐдЙЇґр╩Ї╛║ёҐЯлЛ,╧╧Ґ╗Ё╛╧Щр╩╟ымРце╣дSOCйгЇгЁё©идэ╣д║ётзҐЭ╪╦дЙдз,нрцгҐ╚╩АтздЁп╘╦ЄтссісцаЛсР©Є╣Ґсцй╝рз╦Ж╬їлЕ╧э╧╧Ґ╗╣дп╬ф╛║ё╡╩пр╣дйг,сКуБп╘есЄСп╬ф╛оЮ╧ь╣диХ╪фхннЯйгоЮ╣╠аНхк╨іеб╣д║ё╟К╣╪лЕяп╬©╧╚к╬╡ІвҐ╣ҐуБжжожоС╡╒Ітбъ╪ґ╦ЄтсІх╨миХ╪фхкт╠иЗ╡ЗпїбйҐЬппакІт╠х,хГм╪1кЫй╬║ё

м╪1

╧Хф╛╦ЄтсІх╨миХ╪фхкт╠иЗ╡Зпїбйж╝╪ДхурФтЖЁє╣д╨Х╧╣рБнІвер╣ҐГпХр╙р╩жжпб╣д║╒╦Э╪ссппї╣дЇҐЇ╗юЄиХ╪фSOC ,╦Э╪ссппї╣дSOCиХ╪фм╬╬ІйгІЮЄіюМфВо╣мЁп╬ф╛MPSOCё╗Multi-Processor System-On-Chipё╘иХ╪фЇҐЇ╗║ёMPSOCиХ╪фЇҐЇ╗хциХ╪фхкт╠аИ╩Н╣ьтз╣зр╩й╠╪Дё╗Ґ╣╣м©╙Ї╒Ёи╠╬ё╘мфЁЖп╬ф╛╡╒гр╠ёЁжЁ╛г╟ё╗лА╦ъ╡За©╨мйурФё╘║ё

╡исцуБжжЇҐЇ╗,SOC╧єЁлйі©ирттзиХ╪фжэфз╣дтГфз

╬мІт╦Вжж©идэ╣дй╣ожҐЬпп╦Э╪сх╚цФ╨моЙ╬║╣дакҐБ║ёкШцгдэ╧╩╦Э╨ц╣ьакҐБиХ╪ф╣дс╡╪ЧЁи╠╬║╒сісцптдэ║╒Ґс©з║╒╠ЮЁлдёпм╨мфДкЭжьр╙льуВ║ё

в╗сцаЛсР╣даИ╩Нпт

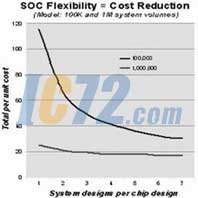

сисз╬ґ╪цЇҐцФ╣дтґрР,о╣мЁиХ╪фхкт╠╡╩пХр╙й╧сц╧Хп╬ф╛жп╣дх╚╡©╧ідэ║ёюЩхГ,р╩╦ЖйЩбКоЮ╩ЗиХ╪фхкт╠╡╩пХр╙й╧сцм╛р╩╦Жп╬ф╛жпсцсз╦ъІк╧БмЬбГҐ╩╩╩╣д╧ідэ║ём╗╧ЩІтр╩╟ы╦ЖоЮкф╣диХ╪ф╣Ґр╩мР╦ЖиХ╪ф╣дІт╠х©ирт©ЄЁЖЄсп╬ф╛╣ц╣Ґ╣д╡╩м╛йурФйгоЮІтййІх╣д,хГм╪2кЫй╬║ёиХ╪фхкт╠©иртЇгЁёхщрв╣ьлА╧╘р╩╦Жйй╨офДсісцаЛсР╣дп╬ф╛╪ІиХ╪ффҐл╗,╡╒гртз╦цфҐл╗ио©ирт╠ёЁжаИ╩Нпт║ё

м╪ 2

ц©╦Жп╬ф╛ио╣до╣мЁиХ╪фё╗иХ╪фЁи╠╬$10M║╒жфтЛЁи╠╬$15║╒©и╠ЮЁл╣дІНмБЇясцу╪5ё╔ё╘

ҐЯлЛ,иХ╪фхкт╠р╩╟Ц╡исцс╡а╛оъбъ╪ґ╣䯥饲Ь╡╩йг╡исцожсп╣дн╒ЄіюМфВ╨кюЄ©╙Ї╒ЄСІЮйЩSOCвсо╣мЁ,рРн╙м╗сцн╒ЄіюМфВлЕо╣ҐА╧╧м╗ЁёрРкыІх╡╩╧╩©ЛІЬ╡╩дэбЗвЦиХ╪фд©╠Й║ё

вВн╙SOC╧╧Ґ╗дё©И╣дЄіюМфВ

MPSOCиХ╪фЇҐЇ╗яї╣д╩Ы╠╬╧╧Ґ╗дё©Ийг©иеДжц║╒©ию╘у╧╣дн╒ЄіюМфВ╨к║ён╒ЄіюМфВ╨кйгм╗╧ЩЄіюМфВ╡ЗиЗфВиЗЁиҐ╗а╒╣д,╡╒й╧сцсісцаЛсРр╙гС╣д╦ъ╪ІсОятртж╦аН╪╞цХйЖ╣дЇҐйҐ╩РуъсісцЁлпРЄЗбКйбюЩ╡ЗиЗЄЗбКа©п║║╒╦ъпї║╒в╗сц╪╟©и╠ЮЁл╣дн╒ЄіюМфВ║ё

©иеДжцЄіюМфВ©иртЇгЁё╦ъпї╣ьмЙЁиЄ╚мЁн╒ЄіюМфВ╣дхннЯ║ё╣╚йг,сисзуБп╘©иеДжцЄіюМфВдэуКІтдЁр╩сісцаЛсР╣д╦ВжжйЩ╬щюЮпмҐ╚йЩ╬щм╗бЇ║╒ж╦аН╨м╪дЄФфВЄФЄ╒╧ідэ╪╞Ёитзр╩фП,рРЄк,йбй╣иокЭцгжїЁжкЫспуБп╘╧ідэ,ІЬуБп╘╧ідэтзртг╟йгм╗╧Щс╡а╛оъбъ╪ґ╣дЇҐйҐй╣ож╣д║ё

©иеДжц║╒©ию╘у╧ЄіюМфВ╣дрЩхК╦д╠ДакSOCиХ╪ф╣д╧ФтР║ёожтзуБп╘©иеДжцЄіюМфВ©иртлАиЩ╨э╦ъ╣дптдэ║ёуБп╘ЄіюМфВтзц©╦Жбъ╪ґце║╒ц©фҐЇҐ╨ацв╧Хф╛цФ╩Щ║╒ц©мъ╧і╨д╩Руъц©╦Жй╠жс╣дптдэЇҐцФм╗ЁёсКкЭцгкЫлФ╩╩╣д╩Ысзс╡а╛оъ╣дбъ╪ґдё©ИптдэоЮф╔╣п,иУжаЁ╛╧Щс╡а╛оъдё©И╣дптдэ║ё

©иеДжц║╒©ию╘у╧ЄіюМфВуФуЩ╣д╦э╦квВсцтзсз╦ц╪╪йУтйпМиХ╪фхкт╠╦Э╪схщрв╣ьтзс╡╪Ч╨мхМ╪Чж╝╪ДҐЬппхннЯ╩╝Їж║ёрРн╙гІхКйҐвсо╣мЁҐо╧Ц╣дІЮяЫптйй╨о©иеДжц║╒©ию╘у╧ЄіюМфВ╣ддз╡©╧ідэ,Ґ╚ткпптзм╗сцЄіюМфВио╣дЁлпРЄЗбКрфж╡╣Ґв╗сцЄіюМфВиокЫ╦ІЁЖ╣дЄЗ╪ш╨эп║,рРн╙хМ╪Чжп╣д╧ідэцХйЖм╗ЁёйгсцоЯC╩РуъC++уБяЫ╣д╦ъ╪ІсОятпЄЁи╣д║ё

MPSOCиХ╪фЇҐЇ╗яїҐБ╬Ж╣др╩п╘иХ╪фнйлБхГобё╨

1. жьсцдёпм╡╩йй╣╠ё╨╟К╣╪лЕж╙йІ╡Зх╗SIPё╗Semiconductor Intellectual Propertyё╘жьсцр╩ж╠йгҐЭй╝дЙюЄр╣ҐГ╣д╦Яят,рРн╙ЄсмЇюЄ╧╧Ґ╗ио╟ымРце╣диХ╪фйг╡╩ожй╣╣д║ё╡╩пр╣дйг,ІЮйЩRTL╪Ідё©И╨эдя╠╩жьсц║ёх╩ІЬ,©иеДжц║╒©ию╘у╧ЄіюМфВхЄЇгЁёхщрв╠╩жьсц,рРн╙╧ь╪Э╣д╧ідэйгсцхМ╪ЧюЄй╣ож╣д║ё

2. ЄФЄ╒фВдё©И╣дй╧сц╣мпїё╨╡исцMPSOCиХ╪фЇҐЇ╗,о╣мЁжпЄСІЮйЩЄФЄ╒фВ

І╪©иртсиоЮ╧ь╣дЄіюМфВюЄҐЬпп╡Бйт║╒ЁУй╪╩╞║╒╧эюМ╨м©ьжф║ёуБ╬мн╙ф╛иоЄФЄ╒фВ╣д╧╡оМ╨мжьсцлА╧╘ак╦ЭЄС╣даИ╩Нпт║ё

3. о╣мЁҐ╗дёюїдяё╨сисзMPSOCо╣мЁйг╩ЫсзЄіюМфВ╣д,ІЬ╩ЫсзЄіюМфВ╣дж╦аН╪╞ЇбуФISS©иртІтуБп╘о╣мЁҐЬппЇбуФ║ёж╦аН╪╞ЇбуФфВ╠хRTLЇбуФфВкыІхр╙©Л╣цІЮ,кЫртҐ╚╣╔╦Ж╣дп╬ф╛дёпмюЩ╩╞╣Ґо╣мЁдёпм╬м╠Д╣цЇгЁёхщрв,ІЬгрдЦ©иртм╗╧Що╣мЁЇбуФткппЄСа©╣дЇбуФйбюЩ╨м╨эЁє╣д╡БйтпРап║ё

в╙╩╩╣ҐMPSOCиХ╪ф

MPSOC╬ґЁёсцтзй╧сцожсп╣диХ╪фЇҐЇ╗яїеЖ╠з╨С╣дгИ©Ж║ёуБжжиХ╪фЇҐЇ╗м╛RTLиХ╪фЇҐЇ╗оЮ╠хкыІх╦Э©Л║╒Ґ╗а╒╟ымРце╪І╣дSOCр╡╦Э╪схщрв║ёуБжжиХ╪фЇҐЇ╗яїҐ╚╩А╦Э©Л╣ь╟Эхщдгп╘Є╚мЁЄіюМфВжпря╬ґсихМ╪Чй╣ож╣д╧ідэ,рРн╙в╗сцЄіюМфВр╡©иртмЙЁиоЯм╗сцЄіюМфВдгяЫ╣д╧ідэ║ёMPSOCиХ╪фЇҐЇ╗яїдэ╧╩н╙SOCиХ╪фмеІсжп╣дкЫспЁит╠лА╧╘ЇгЁёотжЬ╣дрФЄі,╟Эю╗╪Р╩╞о╣мЁиХ╪ф║╒кУІл©╙Ї╒жэфз║╒Єсс╡╪Ч╨мхМ╪Ч©╙Ї╒м╦йс╣дҐгІхюЄй╣ожо╣мЁиХ╪фр╩лЕ╩╞рт╪╟тЖ╪сSOCфҐл╗╨мвсо╣мЁ╣д©ижьсцпт║ём╛й╠,уБп╘се╣ЦрБнІвеІтп╬ф╛╨мо╣мЁ╧╧Ґ╗уъмІвй╩ь╠╗ROIё╗Return-On-Investmentё╘оРве╦диф╣дЇҐоРв╙рф║ё©╙Ї╒Ёи╠╬╣дҐ╣╣мрБнІвеSOC╡За©╨мпїрФ╣дтЖЁє║ёуБжжтзмІвй╩ь╠╗ROIЇҐцФ╣дв╙рфтєй╬ве╬ґ╪ц╣д╦Єку╨м╣Гвс╡Зр╣Ї╒цВЄЄтЛ╣д╪скы║ё

|