кФвепео╒©фя╖╣д╥икы╥╒у╧ё╛йЩ╬щ╡и╪╞╨м╢Ф╢╒╪╪йУ╧Ц╥╨с╕сцсзюв╢О║╒м╗пе║╒рё╡Брё╦п╣хаЛсР║ётз╦ъкыйЩ╬щ╡и╪╞о╣мЁжпё╛сиADCв╙╩╩╨С╣дйЩ╬щпХр╙╢Ф╢╒тз╢Ф╢╒фВжпё╛ты╫ЬппоЮс╕╣д╢╕юМё╛╠ёж╓©Лкыв╪х╥╣дйЩ╬щ╢╚йД╢╕юМйгй╣ож╦ъкыйЩ╬щ╡и╪╞╣др╩╦Ж╧ь╪Э║ёсисз╦ъкыADC╣дв╙╩╩бй╨э╦ъё╛╤Ь╢Схща©RAMоЮ╤тADCйДЁЖкы╤х╫обЩё╛╠ёЁж╦ъкыйЩ╬щ╢Ф╢╒╧ЩЁл╣д©и©©пт║╒й╣й╠птйгр╩╦Ж╠х╫о╪╛йж╣днйлБ║ё╤тсзйЩ╬щ╡и╪╞о╣мЁжп╣д╢Схща©╦ъкы╤хйЩ╬щ╢Ф╢╒║╒╢╚йДё╛╠╬ндлАЁЖр╩жж╩ЫсзFPGA╣д╤Юф╛RAMй╣ож╦ъкыйЩ╬щ╣д╢Ф╢╒╨м╢╚йД╣д╥╫╟╦ё╛╡╒с╕сцсз1GS/sйЩ╬щ╡и╪╞о╣мЁжпё╛й╣ожакрт╣мЁи╠╬RAMмЙЁи╦ъкый╣й╠йЩ╬щ╢Ф╢╒о╣мЁ╣диХ╪ф║ё

╥╫╟╦я║тЯ

╦ъкы╣дйЩ╬щ╡и╪╞кы╤хйг╠ёж╓йЩ╬щ╡и╪╞╬╚╤х╣д╠Йв╪ё╛╣╚мЫмЫтзйЩ╬щ╢╕юМй╠╡╒╡╩пХр╙ртм╛яЫ╣дкы╤хю╢╫Ьппё╛╥ЯтР╤тс╡╪Ч╣дпХгСл╚╦ъё╛Ёи╠╬р╡╫о╦ъ║ёуБ╬мпХр╙спр╩╦ЖйЩ╬щ╩╨╢Ф╣╔т╙ё╛╫╚йЩ╬щспп╖╣ь╢Ф╢╒ё╛ты╦Ы╬що╣мЁпХгС╫ЬппйЩ╬щ╢╕юМ║ё

м╗Ёё╧╧Ёи╦ъкы╩╨╢Ф╣д╥╫╟╦спхЩжж║ё╣зр╩жжйгFIFO(ох╫ЬохЁЖ)╥╫й╫║ёFIFO╢Ф╢╒фВ╬моЯйЩ╬щ╧э╣юр╩яЫ,йЩ╬щ╢с╧э╣ю╣др╩м╥аВхКё╛╢саМр╩м╥аВЁЖё╛ох╫ЬхК╣дйЩ╬щохаВЁЖ║ёFIFO╬ъспа╫лвйЩ╬щоъ╤Ьнч╣ьж╥оъё╛©итзфДр╩╤кп╢╡ывВ╤ЬтзаМр╩╤к╤а╡ывВё╛йЩ╬щтзфДжпкЁпРрф╤╞ё╛рР╤Ьдэ╧╩╢О╣╫╨э╦ъ╣д╢╚йДкы╤х╨мп╖бйё╛грсисзй║х╔ак╣ьж╥оъ╤ЬспюШсзPCB╟Е╡╪оъ║ёх╠╣Цйгж╩дэкЁпР╤ап╢йЩ╬щё╛╡╩рваИ╩Н©ьжфё╛╤Ьгр╢Схща©╣д╦ъкыFIFO╥гЁё╟╨╧С║ё

╣з╤Чжжйгк╚©зRAM╥╫й╫║ёк╚©зRAM╬ъспа╫лв╤юа╒╣дйЩ╬щ║╒╣ьж╥╨м©ьжфвэоъё╛рР╤Ь©и╢са╫╦Ж╤к©зм╛й╠╤ап╢╤Ь╩╔╡╩╦ихеё╛╡╒©и╫╚╡ияЫйЩ╬щ╢ср╩╦Ж╤к©зп╢хКё╛╤Ьси©ьжффВ╢саМр╩╦Ж╤к©з╤аЁЖ║ёк╚©зRAMр╡дэ╢О╣╫╨э╦ъ╣д╢╚йДкы╤хё╛╡╒гр╬ъспкФ╩З╢Фх║╣дсе╣Цё╛х╠╣Цйг╢Схща©╣д╦ъкык╚©зRAM╣д╪ш╦Я╨э╟╨╧С║ё

╣зхЩжжйг╦ъкыRAM">SRAMгп╩╩╥╫й╫║ё╦ъкыRAM">SRAMж╩спр╩лвйЩ╬щ║╒╣ьж╥╨м©ьжфвэоъё╛©им╗╧ЩхЩл╛╩╨ЁЕце╥ж╠П╫с╣╫A/Dв╙╩╩фВ╨м©ьжффВио║ё╣╠A/D╡ияЫй╠ё╛RAM">SRAMсихЩл╛цегп╩╩╣╫A/Dв╙╩╩фВр╩╡Юё╛ртй╧╡ияЫйЩ╬щп╢хКфДжп║ё╣╠A/D╡ияЫ╫АйЬ╨Сё╛RAM">SRAMтысихЩл╛цегп╩╩╣╫©ьжффВр╩╡Ю╫Ьпп╤ап╢║ёуБжж╥╫й╫╣дсе╣ЦйгRAM">SRAM©икФ╩З╢Фх║ё╛м╛й╠╫о╢Схща©╣д╦ъкыRAM">SRAMспожЁи╣д╡Зф╥©и╧╘я║тЯ║ё

╢с╫╣╣мЁи╠╬ио©╪бгё╛╡исц╣зхЩжж╥╫й╫й╣ож╢Схща©йЩ╬щ╢Ф╢╒╧╕дэ║ё╫А╨о1GS/sйЩ╬щ╡и╪╞о╣мЁ╣др╙гСё╛╢Ф╢╒иН╤хн╙4MB║ёя║тЯISSI╧╚к╬╣д╬╡л╛RAMё╛си8ф╛IS61LV25616╧╧Ёи4MB╡БйтйЩ╬щ╣д╢Ф╢╒ё╛о╣мЁ╫А╧╧хГм╪1кЫй╬║ё

м╪1йЩ╬щ╢Ф╢╒т╜юМ©Рм╪

йЩ╬щ╢Ф╢╒иХ╪ф

║ЯйЩ╬щаВ©ьжф

ADCн╙к╚м╗╣ю500MS/s╣дв╙╩╩бйё╛8bit╣д╢╧ж╠╥ж╠Фбйё╛в╙╩╩йЩ╬щ╣дйДЁЖйгц©м╗╣юI║╒Qа╫╦Ж╥╫оРио╡Н╤╞йДЁЖё╛тз╡Н╤╞й╠жс500MHz╣дгЩ╤╞обё╛©иртй╣ож1GS/s╣дй╣й╠╡ияЫбйё╛сиADCйДЁЖ╣д4б╥в╙╩╩йЩ╬щаВйДЁЖ╥ж╠Пн╙250MS/s║ё╤ЬIS61LV256о╣апRAM╣дкы╤х╪╤╠Пн╙10ns╩Р12nsё╛уБяЫйЩ╬щ╠ьпК╬╜╧ЩFPGA╫Ьпп╩╨╢Фрт╨Сё╛╡е©иртты╢н╢ФхКRAM║ё

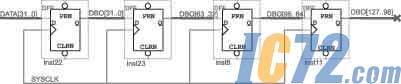

IS61LV25616о╣апRAMп╬ф╛сп16н╩йЩ╬щоъё╛18н╩╣ьж╥©М╤хё╛м╛й╠╩╧╟Эю╗йЩ╬щ╤аRD║╒п╢WR╪╟ф╛я║CS╣х©ьжфпе╨е║ё╫╚8ф╛RAM╡╒ппа╛╫с╣╫FPGAиоё╛вИЁийЩ╬щ╡и╪╞╣д╢Ф╢╒╣╔т╙║ё

╫╚╢сADCйДЁЖAI[8...0]║╒AQ[8...0]║╒BI[8...0]║╒BQ[8...0]ё╛ц©б╥пе╨е╤╪н╙LVDSйДЁЖё╛╧╡32н╩н╙р╩вИв╙╩╩йЩ╬щDATA[31...0]ё╛кыбйн╙250MS/sё╛р╙╫╚уБ╦Жкы╤хтзFPGAдз╡©╫╣жаRAM©и╫сйэ╣д╥╤н╖║ёя║сцCycloneIIо╣апFPGAё╛фДдз╡©й╠жс©и╧╓вВтз402.5MHzё╛ж╖Ёж╣╔╤к╨м╦ъкы╡Н╤╞╠Йв╪I/O╫с©зё╛╤тсз250MS/s╣дйЩ╬щаВмЙх╚©ирт╫сйу║ёюШсцFPGAдз╡©╣дD╢╔╥╒фВвВн╙╩╨ЁЕё╛╬╜╧Щ4╪╤╩╨ЁЕж╝╨С╥ж╠П╣ц╣╫DBO[127...0]ё╛уБяЫйЩ╬щкы╤х╫╣н╙62.5MS/s║ё╬╜╧Щ╩╨ЁЕ╨С╣дйЩ╬щря╬╜тзя║сц╣дRAM╫сйэкы╤х╪╤╠Пдзё╛╫╚╣ц╣╫128н╩╣дйЩ╬щвВн╙8ф╛RAM╣дйЩ╬щоъё╛мЙЁиакйЩ╬щаВ╣д©ьжф║ёйЩ╬щ╩╨ЁЕ╣дт╜юМхГм╪2кЫй╬║ё

║Я╣ьж╥╥╒иЗфВиХ╪ф

ц©╢н╤ап╢йЩ╬щй╠ё╛╠ьпКлА╧╘йЩ╬щ╣д╢Ф╢╒н╩жцё╛рт╤ап╢пе╨евВн╙й╠жс╪фйЩпе╨её╛кЁпР╡ЗиЗ╣ьж╥пе╨её╛фДжпNWEйгRAM╣дп╢йЩ╬щпе╨её╛NOEйг╤айЩ╬щпе╨её╛╤Чуъ╤╪йг╣м╣Гф╫спп╖ё╛я║тЯAB[17...0]вВн╙RAMвИ╣д╣ьж╥пе╨е║ёCNTENйг╣ьж╥╪фйЩфВ╣дй╧дэпе╨её╛си╤ах║/п╢хКйЩ╬щ╣диН╤х╬Ж╤╗ё╛╣╠н╢мЙЁи╤ах║/п╢хК╣дйЩ╬щй╠ё╛CNTENё╫0ё╛╢кй╠тйпМ╤а/п╢╡ывВ╪лпЬж╢ппё╩╣╠╤а/п╢╡ывВмЙЁий╠ё╛оЮс╕╣д╣ьж╥пе╨е╫╚CNTENиХжцн╙1ё╛тРмёж╧╣ьж╥╪фйЩ║ё╣ьж╥╥╒иЗфВ╣дт╜юМхГм╪3кЫй╬║ё

м╪3╣ьж╥╥╒иЗфВиХ╪ф |