ժҪ�����ܴ��ģ�����ٶȵģƣУǣ���С����������ϵͳ����е�Ӧ�á��ڸ�ϵͳ����У������ˣأ�������˾�ģƣУǣ�оƬ�أãӣ�����Ϊ��Ҫ�����������Ͻ�����ϵͳ�Ĺ��ܼ�������һƬоƬ�ϡ�ʵ��֤�����������˳ɱ�������������ƺ͵��Ե�ʱ�䡣

�ؼ��ʣ����� �ƣУǣ� Ƭ��ϵͳ

�Ӵ�ͳ��������˵���ƣУǣ���ͨ�ÿɱ������������Ӧ�������ʽϵ͵ģģӣ�����У����ڸ��ٵģģӣ�Ӧ���У�������ʹ��ר�õģģӣ�оƬ�����ɵ�·������ơ���������Ȼ�����˶��ٶȵ�Ҫ���ǿ������ڽϳ�����Ʒ�ĵ����������Ƚ����ѣ���������Խϲ

���Ź���ˮƽ����ߣ��ƣУǣ��ȿɱ���������ٶȺ�ģ�����˺ܴ����ߣ������������м��ɶȸߡ����С�����ĵ͡�����������ƣ�������Ϊ���ÿɱ������ʵ�ָ��٣ģӣд��������˵�·��Ŀǰ��һ���ģƣУǣ��ȿɱ���������������ٶ���������ģӣе�Ҫ���ҿɱ����ԴҲ������ӣ���ϵͳ�����ɷ���Ҳ��������Ҫ���Ӷ������ϵͳ������Ժ���Ӧ�ԡ���ˣ��ڿ������ڽ϶̻��ϵͳ�����Ҫ��ϸߵij������ƣУǣ��ܹ��ṩ��ר�ãģӣ��������ߵ�ϵͳ�ٶȺ��õĽ��������

���������С�����ɵĹ����У�����ϵͳ��Ҫ�����ˣأ�������˾�ģӣ������� �أãӣ���оƬ��

1 ��������

�ӣ�������ϵ�еģأãӣ����ǣأ�������˾�Ƴ��ĵͼ۸����ܵ��ֳ��ɱ�������С�������Ҫ�ص��ǣ�

��ϵͳ�ŵ���Ŀ�ﵽ�ˣ������������̣���� �ã�����Ŀ���������ϵͳ��Դ�ḻ

���߱�Ƭ�Ͽ����÷ֲ�ʽ�ң��͢� ������õģң��ͱ��������������λ

���ֲ�ʽ��������Ԫ��֧�ֲַ�ʽ�ģӣ�����

��֧�֣��������� �ã��弰ϵͳ����

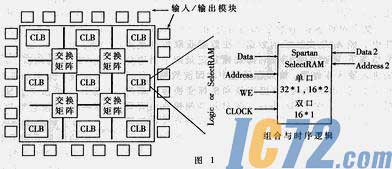

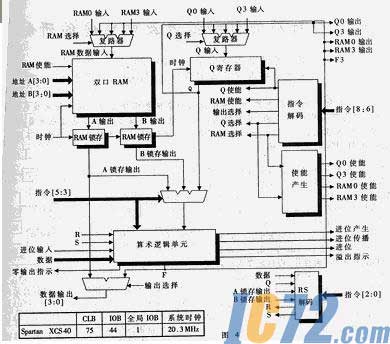

��Ƭ�ڽṹ��ͼ����ʾ��

2 �ɣأãӣ������ɵ�����ϵͳ��ԭ��

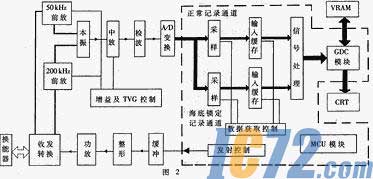

�ԣأãӣ���Ϊ���幹�ɵ��������ɵĻ������ܿ�ͼ��ͼ����ʾ�����У������ڵĹ���ģ��ȫ�������ڣأãӣ���оƬ�ڡ�

С����������ϵͳ�Ļ�������ԭ���Ǹ��ݴ�ˮ�·���������ز��źţ���ʾˮ����Ⱥ�ͺ���������������С�͵�����̽��ϵͳ����ҵ�����ͺ�����ȫ�����ź���Ҫ�����ã���С�ʹ�����ʹ���൱�ձ顣����ϵͳ��Ϊģ����������֡�

ģ�ⲿ�ָ��ݻ������������̵�Ҫ������ȣ�������ȣ���Ƶ�ļ������徭�����塢���Ρ��ƶ������칦��֮�����ź��͵����������������䵽ˮ�С����յ�·Ϊһ�����ջ�����ͬƵ�ʵķ����źž���ǰ�ź��뱾���ľ����Ƶ��������������ȣ�����Ƶ�źţ����������зźͼ첨���ɣ����ı任���γɣ����ص������źţ��͵����ɵ����ִ������֡��շ�ת��ģ��������շ��źŵĸ��룬��������֮��Ĵ��ţ�����Ҫ���ⷢ���źŴ�����ջ��˶�������ջ����ܵĴ�����½���ͬʱ��ͨ��ʱ��������ƣ��ԣ֣ǣ����ֶΣ�ʹ�������źŵĶ�̬��Χ�õ���ѹ���������˽��ջ��Ĺ�����Χ��Ҳʹ������ģ�ⲿ�ֵĿ������Ժ�����ȵõ�����ߡ�

��������ϵͳ�����ֲ��ּ�����һƬ�أãӣ���оƬ�С��������ı任������ݣ������ݻ�ȡ���Ƶ�Ԫ��Э���£�ͨ��������¼�ͺ���������¼����ͨ���ֱ��������洢��������洢���еĻز����ݣ�������ش������Ӳ�������ǿ�ȱ任������任��һϵ���źŴ������ڣƣУǣ������õ���ʾ����ģ��Ĺ�����д��֣ң��͡����ͬʱ����ʾ����ģ������г�ͬ���źţ����Ѳ�ͬǿ�ȵĻز��ź�ת����α��ɫ�źţ�������Ӧ�ģҡ��ǡ�����������֣ң����е�����������ʾ�ڼ������ϡ���������ϵͳ������Ҳ�ɣƣУǣ����õģͣã�ģ�������ƣ������ϵͳ�ļ��ɶȡ�

3 �ֲ�ʽ���������ãң���

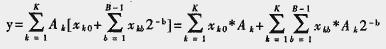

���ڣƣУǣ����ڣӣң��͵����ԣ��ر��ʺϳ˷����ۼӵȣģӣ��㷨��Ҳ��������ʵ�ֹ㷺����ѧ�������㡣�������Ҳ���Բ��ò��нṹ�ͷֲ�ʽ�㷨��ʹ����Դ�ﵽ���ŵ����á��ڸ����ɵ�����У�ʹ��������˲�������ȥ��Ƶ���š� �Ӳ��Լ������������÷ֲ�ʽ���㣬���������źŴ���Ч�ʡ����ڶ�����ϵͳ��һ������ʱ������������Ӧ����������Ĺ�ʽ����ʾ��

�ɼ�������Ĺ�ʽ�����üӷ����ͷֲ�ʽ�������ұ���ʵ�֡����������õ�����˲���������������ıȽϼķ�����ʵ�֣�

�������������������ʱ����ÿ�λز�����������ÿ�㣳���ص����ݣ���ֱ�Ӷ�ÿһλ������ش�����ֻ��һ��ʱ�����ڼ���������㡣���ڳ�������ˣƣУǣ��ڲ��ķֲ�ʽ����ģ��Ͳ��м�����ŵ㣬ʹ���źŴ������ٶȵõ��˺ܴ����ߡ�

Ϊ��ʵ����Ƭ����ɣģӣеĹ��ܣ����˱�Ҫ��������������ģ��֮�⣬����߱�һ����Ŀ��Ƭ�ڴ洢�����������Ӧ�õģӣ������� �أãӣ����;߱��˷ֲ�ʽ��Ƭ�ڣң��͡����ڣأ����� �ƣУǣ�����Ҫ����ģ�鶼�ǻ��ڣӣң��Ͳ��ұ��ṹ�ģ���˷ֲ�ʽ�ң��͵Ľṹ�����ڣƣУǣ��ڵ��κ�һ��ʵ�֡���Ҳ�Ƿֲ�ʽ�ң������Ƶ���������ȥ�ạ̃¡��ɣ�ģ��Ͳ���ģ���⣬�ֲ�ʽƬ�ڣң����Ѿ���Ϊ����һ��Ƭ����Դ�����ڷֲ�ʽƬ�ڣң���û�й��Ⱥ������������Դﵽ�൱��Ķ�д�����ٶȡ������ǵ�����У��ֲ�ʽ�ң��ͱ��������ݵ����뻺�漰���ݼĴ�������Ƭ�ڣ���Щ�ң��ͱ������������źŴ������ֵĸ������Ӷ����������ݴ������ʱ��

4 ���ɵ���ʾ���ƺͣͣã�ģ��

�ڴ�����ʾ��ϵͳ������У�һ�㶼����ͼ�ο���оƬ���ǣģã���ʵ��ͼ����ʾ�Ϳ��ơ�ͼ�ο���оƬ��������г�ͬ���źţ�������ص��źţ������ַ�ͼ�κ�ֱ�ߡ�Բ�Ȼ���Ԫ�ص��������д�֣ң��Ͳ����ƣ֣ң��͵�ˢ�¡�������ʾ��ϵͳ�ĺ��ġ������������������õ��ǣΣţù�˾�ģգУģ����������������ڵ����з��֢����ڸ���ʾ����оƬ����Ƶ��ϵͳ����Ƶ��һ������������ƣУǣ���ʱ������ϡ�

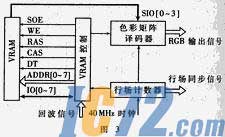

Ϊ�˽��������⣬����������а�ͼ�ο���оƬ�Ĺ��ܼ��ɵ��ˣƣУǣ��Т��γ�һ�����ܱȽ��걸�ģãϣңš�ͼ�ο��Ʋ��ֵĽṹ��ͼ��ͼ����ʾ��ͼ�ο��Ʋ��ֵ���Ҫ���ã��Ǹ���ϵͳ��Ҫ������ȷ���г�ʱ�����壬�Ӷ���ȷ�ؿ������ص�������ϵͳ����ʱ��Ƶ���ǣ����ͣȣ���ͼ�ο��Ʋ��ְ�ϵͳ����ʱ�ӽ��з�Ƶ��������������������ȣ��ͣ����ȣ�����ͬ���źźͳ�ͬ���źţ��ӵ��������Ľӿڣ�������ȷ����ʾ��ͬʱ������ϵͳ��Ҫ��ͼ�ο���ģ����֣ң�����д���µ����ݣ����������Եض����֣ң����е����ݽ�����ʾ�Ͷԣ֣ң��ͽ���ˢ�¡�������в��õ���ʾ����α��ɫ��ʾ������ͬ�IJ�ɫ�źŶ�Ӧ�ڲ�ͬ�Ļز�ǿ�ȡ�Ϊ��ʵ��������ܣ������ڣƣУǣ��е�ͼ�ο���ģ���н�����һ����ɫ���ã���� �ͣ������������Ӧ�ڲ�ͬǿ�ȵ����ص����ݣ��þ�����Խ���ת����Ϊ��Ӧ��������ģҡ��ǡ����źţ��Ӷ�ʵ��ǿ�ȵ���ɫ��ת����

Ϊ�˽�һ�����ϵͳ�ļ��ɶȣ����Dz����ˣã��ӣԹ�˾Ϊ�أ������ģƣУǣ�����Ƶģã�������������������ȡ�������룬��������ϵͳ�����С����������˵���Դʹ��״�����ڲ��ṹ��ͼ��ͼ����ʾ��

���ڲ��ø߶ȼ��ɵ�Ƭ����Ʒ������������źŴ��������������С������ϵͳ����ģ���·�� �أãӣ������洢�����ɣ���ƺ͵��Զ��dz���㣬������������Ҳʮ���ȶ���

|