��ʮ��������FPGAΪ�����ṩ��������Ӧ�Լ�ǿ�����ٵ���ƻ��������ڵ�DSP�����Ա���֣��ɽ�һ�ֿ��ٱ�̵��ź����������źŴ�������������õ�FPGA�ܹ��еij˷������ӷ������ۼӵ�Ԫ����������Ϳ������ô��ģ���м���ʵ����Ч���˲����㷨��

��δ�ӹ�Ƶ�����ܷ������ʧ��ͨ�����м���õ����ֲ������ҵ�Զ����ʧ����ν��ʧ֮���磬��֮ɣ�ܡ����ɴ˻�õ�DSP������ȫ���������������������ʱ������ƣ��˷����ͼӷ�����ʵʩԽ��Խ��Ч��1998�꣬Xilinx˳�������Ƴ��˵�һ��������Virtex™-IIFPGAϵ�в�Ʒ�е�Ƕ��ʽ�˷�����Xilinx®Virtex-II��Virtex-IIProϵ�в�Ʒ������ģ��ƶ�����FPGA��DSP���ϲ�¥��������ÿ��ʮ�ڴ�MAC����ı��ϡ�

������ͨѶ�����¡���������Ƶ��ͼ���г�����������£�Xilinx��һ�������������ɹ�Ӧ����һϵ�ж�����ս��ʹ�����ģ����ʵʩ��ʽ������һ����̨�ס����ų˷����ͼӷ������ܺ��������������Թ��Ľ��й���Ҳ���Խ��Խ���ѡ�

Xilinx�Ĺ���ʦ����Ƴ���DSP48Slice��ʹ��һ����ӭ�ж��⡣DSP48Slice��һ�ֳ����ġ������ܡ�ȫ��λ�������źŴ���Ԫ�����ɷ����ʵ�ּ���������ռ���κ�FPGA�ܹ���Դ����Ԫ����Virtex-5�����еõ���һ����ǿ������������ΪDSP48ESlice����֧�ָ��ߵľ��ȡ�SIMD����ָ������ݣ�����������ģʽ����·������Ԫ��

�Կ������������ϵ���洢���������ʹXilinx������һ��ƽ̨������DSP48ESlice������֮��ǰ��δ��������ӵ�м����ԣ��BlockRAM�ͷֲ�ʽRAM����Ϊ�����㾦֮�ʣ�Xilinx�ڴ�ƽ̨��ʹ���������ٶȸߴ�3.125Gbps�ļ��ɸ��ٴ���ͨ������оƬ��������Ƴ����ݱ�ø�Ϊ��ݡ����Ƽʻᣬ��ЩԪ�������һ��Virtex-5SXTƽ̨�ɴ�Ӧ�˶�����

��Ҫ����FPGA�������źŴ������ݱ���̣�����ع�һ��DSP48ESlice����ͼ1����������Ƶ�������Ҫ���档

ͼ1�CVirtex-5FPGA��DSP48ESlice�Ľṹͼ

*���ɳ˷����͵ڶ��Ρ����ü��ɵĶ����ӷ���/������/�ۼ�����չ�˷��������㡣���ڣ��ڵ���һ��DSP48ESlice�У��Ϳ���ִ�������DSP��������ˡ�

*����ʵʩ��Ϊ��������ܡ������ģ�����DSP48ESlice����Ƴɶ���Ԫ����Ȼ��ͨ���ӿ����ľ��һ�����ӵ�һ�𣬶�ÿһ��DSP48ESlice������������FPGA�ܹ���ר��·���ͻ��塣

*ȫ��λ������ơ�Xilinx�����ȷ����Ҫʵ�ָ����ܺ͵��ģ�һ���������¹��ճߴ���������ȫ��λ��������DZز����ٵġ�Xilinx����Ŷ���Arithmeticaͨ��Э�������˷����ͼӷ�����·MathIP����Լ��ɣ���һ�������Ч�ʡ�

���������Ϊ���У�DSP48ESlice��ʵʩ�����ܺ͵���Ч�ʷ���ﵽ��ǰ��δ�е�ˮƽ��Virtex-5�����е�DSP48ESlice�ֱ��Ը���550MHz������500MHz�͵���450MHz���С�����������ʹ��һ��DSP48ESlice���ǽ�����640��DSP48ESlice�㼯������Virtex-5SXT�����У������Դﵽ��һ���ܣ�ʹ��ר�õļ�����ʵ��ÿ��3520�ڴγ˷��ۻ����㣩�����ң�ʵ����һ����̾Ϊ��ֹ�����ܣ�����ʹ����DSP48ESlice����ȫû����������FPGA·����Դ��

����ר�õļ�������ζ���ܺĵļ����ǻ���ÿһ��DSP48ESlice�ģ�Ҳ���������ٶȺ�����ķ�ת�ʡ�����DSP48ESlice��ʵ�������Ϊ1.38mW/100MHz������������ٶ�Virtex-5SX95T����������640��Slice����550MHz���У�����ת��Ϊͨ����38%��������DSP48ESlice�����嶯̬����Ϊ4.92W��

���ġ���������Ƽ���

Ϊ�˳�����ö��ص�Virtex-5SXT�ܹ����������źŴ�����������ѭ���µļ���ָ�ϣ�

*ʵʩ�����ʹ��DSP48ESlice���˲����㷨��ÿһ��25x18λ��DSP48ESlice����ͬ��500�����Ͽɱ����Slice������Ϊͬ����ʵʩ��1/10�����������������ٶȸߴ�550MHz��

*����DSP48ESlice�����й��ܡ�ÿһ��DSP48ESlice�������óɶ�����25x18�˷�����һ��25x18λ�˷�����ӷ���/������/�ۼ���������һ��48x48λ�ӷ������������ÿһ��DSP48ESlice��֧��SIMD�����Լ��Գƻ�����Բ����

*ʵʩ��������㡣DSP48ESlice�������ڶ���FIR��FFT���ӵĹ������������������IJ�Ʒ��25x18�������С�ͼ���·����ʹ���ǿ���ʹ������DSP48ESlice��ʵ�ָ�Ч��24x24���Ÿ������㡣

�������ź�Ӧ����ʹ��DSP48ESlice

Virtex-5SXTƽ̨��DSP48ESlice��BlockRAM��������ǧ��λ���շ����Ķ��ؽ�ϣ�ΪDSP��������Ӧ���ṩ�˸߳ɱ�Ч�桢�����ܡ����ĵĽ��������Ϊ��˵����һ�㣬�����ǿ���Virtex-4SX��Virtex-5SXT����ƽ̨�����߿���Ӧ�ã��Ա�һ����������µĹ��IJ��

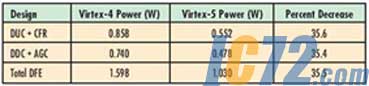

WiMAX����ǰ��(DFE)�������������ݣ������ϱ�Ƶ(DUC)/�����±�Ƶ(DDC)�����������С(CFR)���Զ��������(AGC)���������Ҫ��Ĺ��˹���������һ��Virtex-4SX25FPGA��һ��Virtex-5SX35TFPGA�����ṩ��DSP48ESlice��ƥ�䡣���������Ƶ��Ϊ276MHz������Virtex-4SX25FPGA��73%��DSP48��Դ��128���е�95����������Virtex-5SX35TFPGA��48%��DSP48E��Դ��196���е�95������

���ܵ���WiMAXDFE�����ı��ֺ�������ʵʩ����Դ�����˾�̾����������һ���Ļ����书��Ч�ʡ��������Ҫʹ��DSP48����DSP48ESlice����Ҳ����BlockRAM��������1����Щ���������˶Աȣ���չʾ��Virtex-4��Virtex-5������ʵ��ĺͽ���ˮƽ��

����

�������źŴ�����Ҫ���ڲ�����ߣ��ṩ����չ������DSP�ĺ���������������ˣ���ÿ�뼸��GMAC�������ߵ�ˮƽ�Ϲ������ĵ�����Ҳ�������ȡ�XilinxVirtex-5SXTFPGAƽ̨�ṩ�˶��صĵ�оƬ���������������ô��ģ���м���ﵽ�������ܣ�ͬʱ�����Ľ�����͡� |