现场可编程门阵列(FPGA,FieldProgrammableGateArray)是一种高密度可编程逻辑器件,其逻辑功能是通过把设计生成的数据文件配置进芯片内部的静态配置数据存储器(SRAM)来实现的,具有可重复编程性,可以灵活实现各种逻辑功能。由于FPGA器件采用的是SRAM工艺,在断电的情况下FPGA内的配置数据将丢失。所以,在典型的采用FPGA器件的电子系统中通常将FPGA的配置数据存放于其兼容的SPROM中,上电时由控制电路将SPROM中的配置数据装入FPGA器件中。但是通常的SPROM价格昂贵,且是一次性,不利于FPGA程序的更新,所以有必要分析FPGA的配置原理,采用廉价、能重复使用的方式配置FPGA。

本文主要根据Altera公司手册及以前的经验,设计和完成了一种新的FPGA配置文件下载更新的方法。其主要原理是在每次启动系统时,由配置控制器从Flash中读出FPGA配置文件,再下载到FPGA中以完成器件的配置功能。当系统需要升级更新FPGA配置文件时,可通过网络或者由主机通过JTAG接口(未联网时)将配置文件发送给基于NiosII处理器的嵌入式系统中,由NiosII处理器更新系统中的Flash。当Flash内容更新后,系统就可实现在加电时由配置控制器自动将配置文件下载到FPGA中。而配置控制器是采用复杂可编程逻辑器件(CPLD),主要功能是实现并串转换。这样在不需要任何硬件动作和专业软件的情况下,只需要进行常规软件操作就可以更新FPGA的配置文件。不仅节约了成本,还有效地缩小了系统体积,有利于以后系统工程的升级更新。

1基于NiosII的嵌入式系统简介

NiosII是Altera公司在第一代软核处理器Nios的基础上于2004年5月为其FPGA产品配套开发的软核CPU。NiosII是一种采用流水线技术、单指令流的基于RISC技术的通用嵌入式软核处理器、哈佛体系结构,地址、数据、指令均为32位,最高性能可达到200DMIPS(DhrystonesMIPS)。NiosII系统中的外设具有可配置性,用户可根据实际应用来裁剪,并且NiosII处理器有很好的自定义指令支持,大部分指令均可以在一个时钟周期内完成,这也是可配置处理器的优势所在。NiosII在逻辑功能上是32位的精简指令集CPU;而在实现方式上,它是在FPGA上通过编程方式实现的,这也是与传统的CPU一个根本差别。NiosII的总线方式也采用了一种简单的总线体系结构――Avalon总线。该软核CPU为可编程片上系统SOPC给用户提供了一套综合解决方案,它可以与用户自定义逻辑结合构成SOC系统,并下载到Altera的FPGA芯片中,使得FPGA在嵌入式系统领域的地位越来越重要。

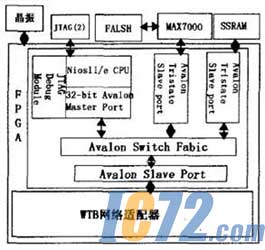

基于NiosII的嵌入式系统主要实现了绞线式列车总线(WTB,WireTrainBus)网络节点机的功能,该系统是基于SOPC技术,首先定制NiosII的嵌入式CPU、必要的外部和相关配置的芯片,然后按照WTB标准和NiosII特有的Avalon总线接口设计并通过VHDL实现MAU的功能,由NiosII来控制WTB网络通信功能。基于NiosII嵌入式软核WTB网络节点机硬件体系结构主要由FPGA、Flashnemory、SSRAMMemory、MAX7000配置控制器等硬件组成。FPGA采用Altera公司的Cyclone系列的EP1C6Q240C8,使用Altera公司的MAX7000系列的EPM7256配置控制器完成对EP1C6Q240C8的配置,基于NiosII的嵌入式系统的原理图如图1所示。

其中图中的JTAG2表明有2个JTAG接口,一个用来在线配置调试,一个用来下载更新配置文件。

2FPGA器件的配置方式

FPGA的配置方式分为主动方式(AS,ActiveSerial)、被动方式(PS,PassiveSerial)和JTAG方式,数据宽度有8位并行方式和串行方式两种。在主动模式下,FPGA在上电后,由PLD器件引导配置操作过程,它控制着外部存储器和初始化过程,自动将配置数据从相应的外存储器读入到SRAM中,实现内部结构映射;而在被动模式下,FPGA则作为从属器件,由相应的控制电路或微处理器提供配置所需的时序,实现配置数据的下载。

下面对基于ICR(In-CircuitReconfigurability)FPGA器件的配置方式进行详细分析:

(1)主动串行方式(AS,ActiveSerial):主要使用EPC配置器件,适应用低速设备的配置;

(2)被动串行方式(PS,PassiveSeria1):使用配置控制器的串行接口;

(3)被动并行同步方式(PPS,PassiveParallelSynchronous):使用配置控制器的并行同步接口;

(4)被动并行异步方式(PPA,PassiveParallelAsynchronous):使用配置控制器的并行异步接口;

(5)边界扫描方式(JTAG,JointTestActionGroup):使用JTAG下载电缆。

基于AS方式配置使用EPC配置器件进行配置时,首先将配置文件从计算机下载到EPC配置器件中去,然后由EPC配置器件控制配置时序对FPGA进行配置。EPC配置器件有一次可编程和可擦写编程型两种:一次可编程型芯片只能写入一次,不适于开发阶段反复调试、修改及产品的方便升级;可擦除编程型价格昂贵,且容量有限,对于容量较大的可编程逻辑器件,需要多片配置芯片组成菊花链进行配置,增加了系统设计的难度。

使用PS、PPS、PPA方式配置时,配置文件事先是以二进制形式保存在系统ROM中,然后通过配置控制器将配置数据送进FPGA中。PS是通过串行方式送到FPGA中,PPS是以并行方式送给FPGA。FPGA在其内部将并行数据转换成串行数据,该数据转换时需要外部配置时钟的驱动。比较PS和PPS,所用的配置时间几乎相同,而PS的接口方式比较简单,所以嵌入式系统中通常选择PS方式配置FPGA。使用PPA方式配置数据时,配置控制器将配置数据以并行方式送给FPGA,然后在FPGA内部进行数据串行化处理。与PPS不一样的地方是串行化处理时不需要配置外部时钟的驱动,但接口更复杂,工程中很少使用。

边界扫描方式需要连接计算机,无法在现场使用,嵌入式系统中很少采用这种方式。

通过上述的分析,在嵌入式系统中要使用FPGA时,可以采用专用EPC配置器件、PS、PPS、PPA和CPLD配置器件,但是PS、PPS、PPA比专用EPC配置更具成本和体积优势。在PS、PPS、PPA中,PS又是最优的通信方式。所以在嵌入式系统中,选择利用CPLD配置器件的PS被动串行方式来配置FPGA最为合适。

而本文正是利用CPLD配置控制器基于PS方式进行FPGA配置的新方法,在每次启动系统时,由配置控制器从Flash中读出FPGA配置文件的数据信息,再下载到FPGA中以完成器件的配置功能。当系统需要升级更新FPGA配置文件时,可通过网络或者由主机通过JTAG接口(未联网时)将配置文件发送给基于NiosII处理器的嵌入式系统中,由NiosII处理器更新系统中的Flash。当Flash内容更新后,系统就可实现在加电时由CPLD配置控制器自动将配置文件下载到FPGA中。这样在不需要任何硬件动作和专业软件的情况下,只需要进行常规软件操作就可以更新FPGA的配置文件。CPLD配置控制器主要是在配置FPGA时将FLASH存放的配置文件中的并行数据转化为串行数据,实现系统的加电自运行。

3嵌入式系统中FPGA的配置电路设计

3.1PS方式配置时序

在嵌入式系统中,配置控制器可以产生配置时序,能够和FPGA直接通信,将FLASH中的配置文件传输到FPGA的SRAM中去。通常使用PS被动串行方式进行配置FPGA,下面就通信中使用到的5根信号线的配置时序进行说明。

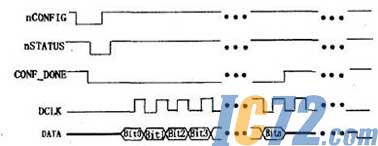

5根信号线分别为nCONFIG、nSTATUS、CONF_DONE、DCLK、DATA,连接配置控制器的5个I/O口和对应的FPGA的引脚,配置时序图如图2所示。

图2PS方式配置信号时序图

配置控制器上的5个I/O端口连接上述5个信号线。其中连接nCONFIG、DCLK、DATA端口设置成输出态,nSTATUS、CONF_DONE端口设置成输入态。当配置控制器开始与FPGA通信时,配置控制器首先在nCONFIG上送出一个大于8um的负脉冲,并且检测nSTATUS上的信号。当FPGA接收到nCONFIG上的下降沿时,迅速将nSTATUS和CONF_DONE拉低,并且保持低电平信号一直到nCONFIG抬高电平。当nCONFIG上抬高电平后过1um,nSTATUS也将电平抬高,配置控制器检测到nSTATUS上的变化后认为FPGA已经做好了接收数据的准备。下一步配置控制器将产生配置时钟脉冲,配置时钟的第一个上升沿至少要比nSTATUS上升沿晚1um。又由于配置数据和配置时钟上升沿同步,所以在配置时钟上升沿发生之前,数据线必须已经有了配置数据信号。配置数据是按照低位在前高位在后的顺序把数据送上数据线。当所有数据都传输完毕后,CONF_DONE线上电平被抬高以示配置完毕。如果传输中出现了异常,FPGA迫使nSTATUS拉低电平,配置控制器一旦检测到了这种现象将重新开始配置。由于配置文件中已经包含了FPGA初始化的一些代码,所以传输完配置文件后,FPGA就可以正常工作了。

3.2基于CPLD配置控制器的配置电路设计

CPLD是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助QuartusII开发软件平台,通过JTAG下载电缆将代码传送到目标芯片中,实现系统配置所需的时序要求和功能需求。而更重要的是CPLD配置控制器可以进行上万次的烧写操作。

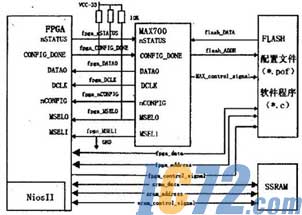

嵌入式系统中FPGA的PS方式配置方式电路设计如图3所示。FPGA和FLASH、SSRAM组成了一个最基本的嵌入式系统,其中将NiosII软核处理器嵌入到FPGA中。FLASH作为程序的存储器,其中存储着系统的整个软件应用程序和配置文件。SSAM作为系统程序运行空间,可以有效地解决配置控制器自身SRAM容量小的问题。

图3PS方式配置方式电路设计

在图3所示的设计中,MSEL0和MSEL1是配置专用线,如果MSEL0接高电平(VCC),MSEL1接地(GND),则此时的配置模式为PS模式;如果MSELO和MSEL1都接地(GND),则配置模式为AS模式。CPLD控制器的控制信号MAX_control_signal主要包括flash_CS_n(片选)、flash_OE_n(输出使能)、flash_RW_n(读写使能)、flash_RESET_n(重置)、flash_BYTE_n(字节传输)等信号线。

配置文件通过Altera的QuartusII软件以.pof(ProgrammerObjectFiles)文件格式下载到EPM7256配置控制器内,如果配置有错误,该配置控制器可以进行多次下载,直至最终完成配置功能。

FLASH中存储的程序包括系统配置程序文件、软件程序,其格式为.flash。系统加电后,配置控制器从FLASH的0地址开始将配置文件进行并/串转换后(即将图3中的flash_DATA[7..0]转换为DATA0)加载到FPGA中,完成系统加电时的自动配置功能;同时NiosII处理器将FLASH中的应用程序移至到SSRAM中运行,从而实现嵌入式系统的初运行。通过NiosIIIDE工具可以将配置文件FPGA的.sof文件格式转换为Flash存储器所需要的.flash文件格式。

4配置文件的设计与实现

为了确保配置过程的正确,提高系统的配置性能,在配置文件设计时应严格按照FPGA的Ps配置流程进行,并在配置过程中始终监控配置工作状态,在完善的配置程序配合下可以纠正如上电次序导致配置不正常等错误。该配置程序是采用VHDL语言编写的,编写完成后,将配置文通过JTAG接口下载到EPM7256配置控制器内,根据图2的PS配置时序,其配置流程如下:

(1)配置信号的初始化:DATAO=0,DCLK=0,nCONFIG=0,CONF_DONE=1和nSTATUS=1,并保持2us以上。

(2)检测nSTATUS,如果为“0”,表明FPGA已响应配置,可开始进行配置,否则报错,并返回1。正常情况下,nCONFIG=0后1us内nSTATUS为“0”。

(3)置nCONFIG=1,并延时5us。

(4)DATAO上放置数据(低位在前),DCLK=1,延时。

(5)DCLK=0,并检测nSTATUS,若为“0”,则报错,重返1。

(6)准备下一位数据,并重新执行(4)、(5),直到数据发送完为止。

(7)此时CONF_DONE应变成“1”,表明FPGA已完成配置,如果数据发送完后,CONF_DONE为“0”,必须重新配置返回1。

(8)配置完成后,再送出299个周期(Cyclone要求的)的DCLK,以便FPGA完成初始化。

5结束语

本文介绍了通过用CPLD的MAX7000系列配置控制器EPM7256和Flash实现Cyclone系列的EP1C6Q240C8FPGA配置文件下载更新的方法。与传统的JTAG或PROM串行下载配置方法相比,此方法具有更新配置文件灵活方便、易于操作、更加有利于系统配置文件的升级等特点。与常用的串行配置方法相比,该配置方法更具有配置时间短,准确率高、易于实现等优点。虽然该配置控制电路是为配置Altera公司cyclone系列的FPGA器件而设计的,但稍加修改也适用于其它系列的。FPGA器件,故其有一定的通用性,采用此方法特别适用于需要不断更新的系统设计中,具有较为广阔的应用前景。 |