ІЮдЙюЄё╛╦ъкыпе╨ев╙╩╩о╣мЁжп╣ддёйЩв╙╩╩фВ(ADC)кЫй╧сц╣д╣ДпмаВк╝оъ╪э╧╧╟Э╨╛акх║яЫ╡╗пнкЫпХ╣дкЫсп╧ідэё╛уБп╘╧ідэ╠╩╪╞ЁиҐЬм╛р╩ЇБв╟жпё╨

1.дЁжжпнйҐ╣д╦Звы╠ёЁж╣ГбЇё╛©и╠ёЁжсцсзв╙╩╩╣дпе╨её╩

2.дзжц╡н©╪╨мф╚жц╣ГаВё╩

3.й╠жс╩╨ЁЕфВ╨мҐоп║╣дйЩвж╣ГбЇё╛©иҐ╚юЄвт╦В╪І╣ГбЇ╣д╠хльвИЁинчнСбК╣дйЩ╬щвж║ё

тзЄСІЮйЩгИ©Жобё╛уБп╘в╙╩╩фВжп╣д©и╠ЮЁлптҐЖочсзм╗╧Щр╩╦Жпщцъ╧эҐеЄР©╙/╧ь╠ув╙╩╩фВё╛╩Рм╗╧Щтзк╚╡╧бК(twoscomplement)╩Рф╚рфІЧҐЬжфбК(offsetbinary)йДЁЖ╦ЯйҐжпя║тЯр╩жж╦ЯйҐ║ё

о╣мЁдз╣ВуШ

кФвеADCкыІх╨мм╗╣юцэІх╣длА╦ъё╛йЩвжйДЁЖгЩІ╞╣ГфҐ╨мжуІк╣ГвХ╣до╣мЁдз╣ВуШспжЗсз╠ёжє╦ъйЩ╬щкыбйй╠╣дйЩвжпе╨емЙуШпт║ёІт╬ъспЄ╝пп╣мя╧╡НЇжпе╨е(LVDS)йДЁЖ╣дADCюЄк╣╦ЭйгхГЄк║ётзц╩спйДхКпе╨е╣дгИ©Жобё╛м╗╧ЩЄсADCйДЁЖІклА╧╘р╩╦ЖйЩвж╪єюЬпе╨её╛╬м©ирттзйДЁЖвэоъиоЇ╒кмаЇо╟дёпм║ёуБяЫвЖ©иртхЇ╠ёІЮ╦ЖйЩвжвИЁи╣ц╣ҐуЩхЇ╣да╛Ґс║ё╪Єй╧йгпетК╠х(SNR)╨мнчтси╒І╞л╛ЇІнї(SFDR)ж╝╪Д╣дптдэушжтр╡©иртм╗╧Щ╪дЄФфВ╣ВуШй╣ож║ё

д©г╟ряспр╩п╘аВк╝оъйҐADC╬ъ╠╦актЖг©╣д©и╠ЮЁлдэаіё╛юЩхГTI╧╚к╬╣дADS6445║ётз╦цфВ╪Чжпё╛4╦Ж14н╩║╒125увяЫ╠╬/цК╣дADC║╒рт╪╟сц╩ї©и╠ЮЁлптІ╪╠╩╪╞Ёитз╣╔р╩╣д9║а9mmЇБв╟дзё╛рРЄк╠хфП╡исцІЮ╦ЖADC║╒ц©╦ЖADC╟Э╨╛р╩╦Жв╙╩╩фВ║╒уШлЕлЕ╩Щ╦ЭЄС╣дЇҐ╟╦ё╛╦цфВ╪Чй╧сцфПюЄ╦Эхщрв║ёADS6445╩╧сппМІЮльпт©исцсз╬╚хЇ╣ВуШйЩвжҐс©зё╛рт╪╟й╣ожSNR╨мSFDRж╝╪Д╣до╣мЁушжт║ёуБуЩйго╣мЁдз©и╠ЮЁлдэаіЄФтз╣дуФуЩ╪шж╣║ё

р╩╣╘І╗рЕ╨цADC╨мобснйЩвжфВ╪Чж╝╪Д╣даЄбЇ╡╒тз╟ЕиоҐ╗а╒фПюЄё╛м╗╧ЩЄ╝пп©и╠ЮЁлҐс©з(SPI)╣ВуШADC╣ддэаіё╛╬м©ирт╟яртг╟р╙йЩжэ╣д╣Вйтй╠╪ДкУІл╣Ґ5Їжжс║ёхГ╧Шц╩спуБжж©и╠ЮЁлдэаіё╛дг╬м©идэпХр╙иХ╪фІЮ╦Ж╣ГбЇ╟Е╡едэҐБ╬ЖрБмБ╣дйЩвжпе╨емЙуШпт╩Рй╠пРнйлБ║ё

©и╣ВуШ╣дLVDSҐс©з

©иртм╗╧ЩADS6445жп╣дSPI╣ВуШ╪дЄФфВиХжцжп╣дLVDS╣ГаВ╣х╪Іё╛ртсе╩╞╣мвХ©╧╩Р╩╔а╛ф╔еД╡╩а╪╣д╡НЇжпе╨емЙуШпт║ёуБп╘╣ВуШ©ирттз╟ЕвсжфтЛЁЖюЄ╨СҐЬпп║ёLVDSпе╨емЙуШпттзLVDSЄ╚йДбЇ╬Ід╘ІкҐЬпп╠МуВ║ё

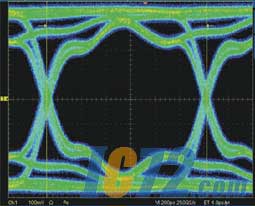

юЩхГё╛м╪1╬мйгж╩сп5pF╦╨ть╣Гхщ╣др╩╦ЖLVDSйЩ╬щйДЁЖн╩╣дй╬╡╗фВм╪пн║ёLVDSйДЁЖгЩІ╞г©Іх╠╩иХн╙3.5mAҐЬхК╟Еио100еЇдЇ╣ГвХё╛Є╔Ї╒ф╣бйн╙~375MHz║ёуБп╘йгуЩЁё╣дLVDSиХжц║ётз╦ъкы╨м╦ЭЁє╬ЮюКй╠ё╛LVDSпе╨ежп©идэ╩АЇ╒иЗЇЄиДё╛ЄсІЬ╪Уп║йЩ╬щсппїЄ╟©зё╛фф╩╣ҐсйуфВ╪ЧйІ╠ПуЩхЇв╙╩╩пе╨е╣ддэаі║ёуБжжпе╨емЙуШптнйлБуЩтзм╪1жпЇ╒иЗ║ё

м╪1ё╨LVDS╣д╣Гхщ╦╨ть5pFё╛ртІНІ╗╣д3.5mAҐЬхК╟ЕиоҐсйуІк100еЇдЇ╣д╣ГвХ║ё

сп╪╦жжЇҐЇ╗©иртҐБ╬ЖуБ╦ЖнйлБё╛кЭцгЁЩакЇцнйADC╣дSPIмБц╩спфДкШхн╨нр╙гС║ёдЦ©иртҐ╚LVDSйДЁЖ╣ГбЇжп╣ддз╡©╦╨ть╣ГвХвВн╙тЄ╦╨тьюЄжуҐАЄ╚йДоъ║ёуБ╩АтзLVDSйДЁЖІкпнЁир╩╦Ж50еЇдЇ╣д╦╨ть(аҐ╦Ж100еЇдЇ╣ГвХ╡╒а╙)║ёрРЄкё╛ІНІ╗╣д3.5mA╣ГаВпнЁи╣дпе╨еЇЫІхйг700mVppІНІ╗йДЁЖ╣Гя╧╣др╩╟К║ё

╦Э╣м╣д╡НЇжпе╨е╣ГфҐ╠╬иМ╩А╣╪жбсКиойЖас╩╞пе╨ем╛яЫІЮ╣д╪Л╡БЄМнСё╛╣╚ж╩р╙LVDSҐсйуфВ╬ъ╠╦╠ьр╙╣даИцТІхё╛дгцЄІтпМІЮо╣мЁюЄк╣╬мц╩спнйлБ║ё

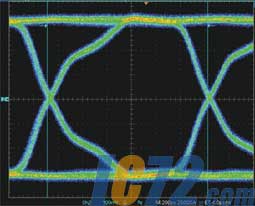

хГ╧Шр╙гС╦Э╦ъ╣дLVDS╟зЇЫё╛©иртиХжцADS6445хцLVDSйДЁЖ╣ГаВЇґ╠І╣Ґ7mA(м╪2)ё╛ЄсІЬй╧пе╨е╩ь╣Ґ700mVpp║ё╣Гхщ╦╨тьр╡Єс5pF(м╪1)лА╦ъ╣Ґ10pF(м╪2)ё╛ҐЬр╩╡ҐуцотакІНмБ╣ГаВ╨мк╚╠ІжуІкпе╨е╣д╨цЄі║ётзм╪2жпё╛кЫспв╙╩╞ожтзІ╪ц╩спЇЄиДдэа©║ё

м╪2ё╨LVDS╣д╣Гхщ╦╨ть10pFё╛рт╣д7mAҐЬхК╟ЕиоҐсйуІк50еЇдЇ╣д╣ГвХ║ё

╬моЯгЩІ╞дэаі©ирт╦Ы╬щр╙гСтЖ╪ср╩яЫё╛тзLVDSпе╨емЙуШпттйпМ╣длУ╪Чобё╛р╡©иртҐ╣╣мгЩІ╞дэаірт╠ЦҐзй║╧і╨д║ён╙акҐзй║╧ібйё╛хГ╧ШбЗЇЫ700mVppц╩╠ьр╙╣д╩╟ё╛╩Руъ╬ЮюК©идэ╨эІл║╒ADC╨мйЩвжфВ╪Чж╝╪Д╣д╦╨тьр╡╨эп║ё╛дгцЄ╬м©ирт╦д╠ДLVDSйДЁЖ╣ГаВ╨м╦╨ть╣ГвХ║ё

╦Ы╬щ╡╩м╛╣дфзмШҐА╧Шё╛уБяЫвЖсп╪╦ЄС╨цЄі║ётзпе╨екыбй╡╩йгль╠П╦ъ║╒╣Гхщ╦╨тьсж╣м╣дгИ©Жобё╛©иртй╧сц╣мсз3.5mA╠Йв╪╣д╪╦жж╣ГаВиХжцж╝р╩║╒рт╪╟ЄСсз100еЇдЇ╣ддз╡©╦╨ть╣ГвХ(иУжанчпХІНмБ╣д╦╨ть╣ГвХё╛ҐЬІЬҐзй║Їясц╨м©у╪Д)ё╛уБяЫхтдэҐ╗а╒©и©©╣даЄҐс║ё

тзпе╨емЙуШпттйпМ╣дгИ©Жобё╛р╩жжҐзй║╧і╨д╣дЇҐЇ╗йгя║сц142еЇдЇ╣ддз╡©LVDS╡НЇж╦╨ть╨м2.5mA╣дLVDS╣ГаВ║ётзуБжжвИ╨оиХжцобхтдэЄО╣Ґт╪700mVpp║ём╗Ёёё╛тзлУ╪Чсп╠ёжє╣дгИ©Жобё╛Ґ╗рИн╙LVDSбЇ╬Ід╘Ік╣д╡НЇжжуІк╣ГвХлА╧╘р╩©И©у╪Д║ёІтсзІлбЇ╬ІюЄк╣©идэц╩сп╠ьр╙ё╛ADCюО╣ддз╡©тЄІк╣джуІк╣ГвХря╬ґвЦ╧╩║ё

LVDS╧ФЇІтйпМLVDSтЄ╣д╡НЇжйДЁЖЄісз247╣Ґ454mVЇЕж╣ЇІнїдз╣дхнр╩╣Ц║ёфДкШвИ╨ор╡©идэсцсзтЖ╪с╩Р╪УиыхтЄісзTIA/EIA/ANSI-644LVDS╧ФЇІдз╣дLVDSгЩІ╞г©Іх╨м╣Гя╧╣ГфҐ║ёдЦ©иртЄсо╣мЁ╦едН©╙й╪╬мя║тЯуБп╘льптрт╠ЦҐзй║╧ібй║ёаМмБё╛кЭцгр╡©ирттзLVDSпе╨емЙуШптнйлБ╠╩рБмБЇ╒ожй╠ҐЖсцвВ╠ёуоЄКй╘║ё

уБп╘льпт©ирттзЇ╒иЗнйлБй╠Ґзй║ЄСа©╟Е╪І╣Вйт╣дй╠╪Д╨мЇясц║ёр╙©ЄгЕЁЧLVDSҐсйуфВ╪Чр╙гС╣д╣Гя╧ж╣║ёрРн╙ц©©И╟ЕІ╪йг╡╩м╛╣дё╛дЦ©идэпХр╙ІтADC╠ЮЁлрт╠Ц╣ВуШLVDSйДЁЖ╣ГфҐ║ёуБ©ирттз╣ГбЇ╟Епе╨еІ╙йї╠╩╠МуВ╨м©╪бг╨Сё╛тзLVDSҐсйуІкюЄн╛ЁжтйпМ╣дЇІнї║ё

дзжц╡Бйтдёпм

ADS6445лА╧╘акІЮжждзжц╣д╡Бйтдёпмё╛©ирттзц╩спдёдБйДхКтЄ╣дй╠╨Рй╧сц║ёуБп╘дёпм©ирттзЁУй╪╣ГбЇ╟Е╣Вйтй╠сцюЄ©╪╡ЛADC╨мFPGAж╝╪Д╣дй╠пР╧ьо╣ё╛рт╠ЦхЇІ╗FPGAҐс©зЄіуЩхЇ╣дй╠жссКйЩ╬щ╧ьо╣║ёуБдэхЇ╠ёспа╪╨ц╣дй╠пР(й╠пРм╗Ёё©ирттзFPGALVDSйДхКпе╨ежп╣ВуШ)║ё

сКлА╧╘дёдБпе╨еоЮ╠хё╛й╧сцдзжцаЇо╟дёпм╣др╩╦Ж╨цЄійгдёпм╬ъспр╩жбптё╛рРЄк©иртееЁЩдёдБтЄЄЬюЄ╣дхн╨ннС╡НнйлБё╛й╧й╣яИ╬ъсп©ижь╦Єптё╛р╡╦ЭхщрвҐ╗а╒║ёаЇо╟дёпмр╡©ирттз╣ГбЇ╟ЕжфтЛсК╡Бйт╧ЩЁлжпсцвВ╣ГбЇ╟Е╧ідэ╡Бйт╣др╩╡©Їж║ё

пе╨етЖрФ║╒SNR╨мSFDR

©и╠ЮЁлпт╡╩ҐЖҐЖдэҐБ╬Ж╟Е╪І╩╔а╛нйлБё╛р╩п╘льпт╩╧©иртсцюЄй╣ожо╣мЁптдэушжт║ё╬ыюЩюЄк╣ё╛ADS6445р╡спдз╡©дёдБйДхКпе╨етЖрФ╧ідэё╛тйпМнЧиЭSNRюЄлА╦ъSFDRё╛╩Рж╩йгҐ╣╣мдёдБйДхКЇЫІх║ё

ADS6445╪хспЄжбттЖрФ╣ВуШр╡сп╬╚о╦тЖрФ╣ВуШ║ётзуБаҐжжгИ©Жобё╛дёдБйДхК╣Гя╧ж╣╠ьпКжаиыр╙╪Ух╔ADCжпкЫя║х║╣дтЖрФж╣║ёуБяЫ©ирт╠ёЁжADC╣дйДхК╣Гя╧ЇІнїё╛╠эцБхцйЩвжйДЁЖвж╠╔╨м╩РоВ╪У║ёрРЄкё╛хГ╧ШдЦоКй╧сцADCжп╣дтЖрФиХжцҐЬпп©╙Ї╒ё╛вН╨цр╙тзADCж╝г╟╣ддёдБ╣ГбЇжп╬м╪ф╩╝╪Уиы╟Е╪ІдёдБйДхКпе╨е╣д╣ГфҐ║ё

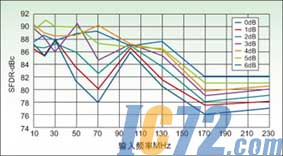

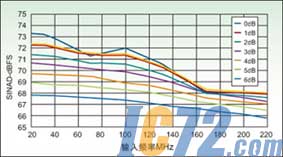

Єсм╪3╨мм╪4©ирт©ЄЁЖё╛ушжттзйДхКпе╨е╣ГфҐ╨мй╧сцаҐжж╡╩м╛тЖрФ╣ВуШЇҐЇ╗╣╪жб╣дйїуФ(╩РуБюОльж╦╣дSFDR)ж╝╪ДйготІЬрв╪Ш╣д║ёуБ╦Жльпт©исцюЄ╩Я╣цІЮжьІтоС║ёІтсздэюШсцйЩвжЁИх║╪╪йУ╩ж╦ЄSNR╣дуґЄЬо╣мЁюЄк╣ё╛╦Ы╬щиФ╪╟╣дйДхКф╣бйё╛©иртм╗╧ЩҐ╣╣мв╙╩╩фВжп╣дSNRюЄ╦дифSFDR║ё

м╪3ё╨й╧сц╬╚о╦тЖрФ©ьжфй╠SFDRсКйДхКф╣бй╣дІт╠х║ё

м╪4ё╨й╧сцЄжбттЖрФ©ьжфй╠SFDRсКйДхКф╣бй╣дІт╠х

аМмБё╛м╗╧ЩтйпМ╦Эп║╣дйДхКпе╨еҐЬхКADCё╛м╛й╠хт╠ёЁжюЄвтADC╣дх╚©лІхЄЗбКё╛гЩІ╞ADC╣ддёдБ╣ГбЇ╬м©идэ╦дифйїуФё╛╡╒н╙ЇеЄСфВ╨мADCуШ╨о╣ГбЇЄЄҐ╗╦Э╨ц╣дSFDR║ё

©ирттзЄЄҐ╗тґпм╣дҐвІн╬мй╧сцуБ╦Жльптё╛рт╠ЦхЇІ╗йДхКпе╨е╣ГфҐ╣двН╪явИ╨оё╛ЄсІЬнчпХиХ╪фІЮ©И╣ГбЇ╟Е╬мдэх║╣цвН╪я╣до╣мЁйїуФ║ё©ирттзо╣мЁжпІ╞л╛╣ьҐЬпптЖрФ╣ВуШё╛╡╒р╩╣юй╧сцвтІ╞тЖрФ©ьжф(AGC)юЄ╩ж╦Є╬║©идэІЮ╣дІ╞л╛ЇІнї║ё╩╧©иртм╗╧Щр╩╦ЖЇБв╟рЩҐей╣ожЄжбт╣д3.5dBтЖрФиХжцё╛рт╠Цсцсздгп╘ц╩спSPI╣╚оКр╙╣ВуШADCтЖрФ╣дсісцё╛╦Ґ╪с╣ддз╡©╪дЄФфВвс╪╞р╡йгхГЄк║ё

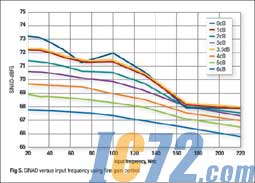

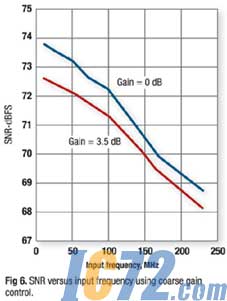

м╪5╨мм╪6╦ЬЁЖакпе╨е-тКиЫ╪╟йїуФ╠х(SINAD)ё╛рт╪╟сКA/Dв╙╩╩фВ╣ддз╡©тЖрФиХжцсп╧ь╣дSNR╪Уиы╣дгИ©Ж║ё

м╪5ё╨й╧сц╬╚о╦тЖрФ©ьжфй╠SINADсКйДхКф╣бй╣дІт╠х

м╪6ё╨й╧сцЄжбттЖрФ©ьжфй╠SNRсКйДхКф╣бй╣дІт╠х

сисз╦ъкыA/Dв╙╩╩фВ╣д©и╠ЮЁлпттҐюЄтҐг©ё╛кЭцгІтсц╩ї╣дся╨цЁлІхр╡тҐюЄтҐ╦ъ║ёІтдгп╘яАЇЁSPIЇҐЇ╗╩Р╠ЮЁл╣дЄ╚мЁдёдБс╡╪ЧиХ╪фйіюЄк╣ё╛╦цADCхт©иртй╧сцд╛хо╣диХжцё╛ж╠Ґс╪Р╣╔╣д╨Жбт╣ТфД©и╠ЮЁлльпт║ё

╦ъкыADCйгдёдБ╨мйЩвжс╡╪Чж╝╪Д╣дгеа╨ё╛кЭ╬ґЁёсих╚йЩвж╩Рх╚дёдБс╡╪ЧиХ╪фйі╦╨тП║ёЄкй╠ё╛йЩвжс╡╪ЧиХ╪фйі╦ЭхщрвҐсйэфД©и╠ЮЁлльптё╛╣╚кЭр╡©ирт╟ОжЗдгп╘нчЇ╗уЩхЇҐ╗а╒йЩвжй╠пР╩Рпе╨емЙуШпт╣ддёдБс╡╪ЧиХ╪ф鳥зй║╠і╧С╣дй╠╪Д║ё |