1 ТэСФ

ФЪРЕәЕҙҰАнБмУтЈ¬DSPјјКхөДУҰУГФҪАҙФҪ№г·әЈ¬»щУЪDSPөДРЕәЕІЙјҜҙҰАнЖҪМЁІ»¶ПіцПЦЎЈіЈјыөДDSPРЕәЕІЙјҜҙҰАнЖҪМЁАыУГЧЬПЯҪшРРКэҫЭІЙјҜЈ¬ЧЬПЯЙП¶аёцЙиұёөДКэҫЭҙ«КдҫӯіЈПа»ҘіеН»ЎЈADI№«ЛҫөДTiger SHARCl01РНDSP(јтіЖTSl01)Ц»УРЧЬПЯәНБҙВ·ҝЪҝЙТФУлНвЙиНЁРЕЈ¬»щУЪ»әҪвЧЬПЯіеН»өДДҝөДЈ¬ұКХЯЙијЖБЛТ»ЦЦТФПЦіЎҝЙұаіМГЕХуБР(FPGA)ЧчОӘКэҫЭҪУҝЪ»әіеЖчЈ¬ұЬҝӘЧЬПЯЈ¬ҫӯTSl01өДБҙВ·ҝЪҪ«¶аёцA/DЧӘ»»ЖчІЙјҜөҪөДКэҫЭҙ«ЛНөҪTSl01ЎЈУЙFPGAНкіЙ¶аёц¶аВ·A/DЧӘ»»ЖчІЙјҜКэҫЭөД»әіеЕЕРтЈ¬ІўРОіЙ·ыәПTSl01БҙВ·ҝЪҙ«КдРӯТйөДКэҫЭБчЈ¬ЛНөҪTSl01өДБҙВ·ҝЪЎЈёГЙијЖКөПЦБЛБҙВ·ҝЪУлЖдЛы·ЗБҙВ·ҝЪНвІҝЙиұёөДНЁРЕЎЈјхЙЩБЛTSlOlЧЬПЯЙПөДКэҫЭҙ«КдБҝЈ¬»әҪвБЛЧЬПЯҫәХщөДОКМвЎЈ

2 ADS8361РНA/DЧӘ»»Жч

ADS8361КЗTI№«ЛҫЙъІъөДЛ«НЁөАЎўЛДВ·ЎўДЈДвІо·ЦКдИлЎў16 bitН¬ІҪІЙСщҙ®РРA/DЧӘ»»ЖчЎЈ4В·ДЈДвІо·ЦКдИл·ЦіЙ2ЧйЈ¬ГҝЧйёчУР1ёцA/DЧӘ»»ДЈҝйЈ¬ҝЙН¬КұІЙСщ;¶ФГҝёцКдИлЧоҝмҝЙТФКөПЦ500 ks/sөДІЙСщВКЈ¬јҙ2 ҰМsҫННкіЙ1ҙОA/DІЙСщЎЈІЙСщәуөДКэҫЭУЙҙ®РРҪУҝЪКдіцЈ¬Хв¶ФУЪҫЯұёН¬ІҪҙ®РРҪУҝЪөДҙу¶аКэDSPКЗ·ЗіЈУРУГөДЈ¬DSPөДЧЬПЯҝЙТФ№ТҪУ¶аЦЦЖдЛыЙиұёЈ¬ФЪёЯЛЩБ¬РшІЙСщөД№эіМЦРЈ¬DSPөДҙ®ҝЪәНЧЬПЯҝЙТФ»ҘІ»У°ПмөШ¶АБў№ӨЧчЎЈ

ADS8361ФЪІЙСщЖөВКВКОӘ50 kHzКұЈ¬УР80 dBөД№ІДЈТЦЦЖЈ¬ХвФЪЗҝФлЙщ»·ҫіЦР·ЗіЈЦШТӘЎЈADS8361РиТӘДЈДвөзС№әНКэЧЦөзС№·Цұр№©өзЈ¬ҝјВЗөҪУлНвІҝөзВ·өДЖҘЕдЈ¬ЛщТФДЈДвІҝ·ЦСЎФс5 V№©өзЈ¬КэЧЦІҝ·ЦУлDSPөДI/OөзС№Т»ЦВЈ¬СЎФс3.3 V№©өзЎЈ№ӨЧчКұјИҝЙТФК№УГДЪІҝ2.5 VІОҝјөзС№Ј¬ТІҝЙТФУЙНвІҝМṩІОҝјөзС№ЎЈІо·ЦДЈДвКдИлРЕәЕөДөзС№·¶О§ОӘЎА2.5VЎЈADS8361ІЙУГSSOP-24·вЧ°ЎЈCSТэҪЕКЗADS8361өДЖ¬СЎ;MlЎўM0ЎўAOТэҪЕУГУЪСЎФсІЙСщНЁөАәНКэҫЭНЁөА;RDТэҪЕОӘ¶БИЎКэҫЭТэҪЕЈ¬CONVSTТэҪЕКЗA/DЧӘ»»ВціеЈ¬ФЪК№УГЦРУҰҪ«RDУлCON-VSTТэҪЕПаБ¬;CLOCKТэҪЕУГУЪКдИлІЙСщКұЦУ(УлПВОДЦРFPGAКдіцөДADCLKПаБ¬);2ёцНЁөАөДКэҫЭКдіцТэҪЕ·ЦұрОӘSERIAL DATA AәНSERIALDATA BЈ¬ГҝҙОЧӘ»»Кдіц16 bitКэҫЭЎЈADS8361өД№ӨЧчКұЦУЧоҙуЦөОӘ10MHzЈ¬ёЯөзЖҪәНөНөзЖҪЦБЙЩёч40 nsЎЈ

3 TSl01өДБҙВ·ҝЪј°ҙ«Кд·ҪКҪ

TSl01КЗёЯРФДЬ128 bitёЎөгКэЧЦРЕәЕҙҰАнЖчЈ¬ЖдФЛЛгДЬБҰәЬЗҝ(18ТЪҙО/Гл)Ј¬¶шНвІҝЧЬПЯНМНВДЬБҰПа¶ФІ»Чг(ИфНвІҝЖөВКОӘ100 MHzЈ¬ФтНвІҝЧЬПЯҙ«КдЛЩ¶ИОӘ800 MB/s)Ј¬өұНвЙиҪП¶аКұәЬИЭТЧРОіЙI/OЖҝҫұЎЈІ»№эЛьУРЛДёцёЯЛЩБҙВ·ҝЪЈ¬ГҝёцБҙВ·ҝЪөДҙ«КдЛЩ¶Иј«ПЮОӘ250 MB/sЈ¬ККәПTSl01Ц®јдөДөг¶ФөгёЯЛЩҙ«КдЈ¬ТІҝЙУлЖдПаН¬РӯТйөДНвЙиНЁРЕЈ¬ҙУ¶шҙуҙу»әҪвБЛЧЬПЯС№БҰЎЈ

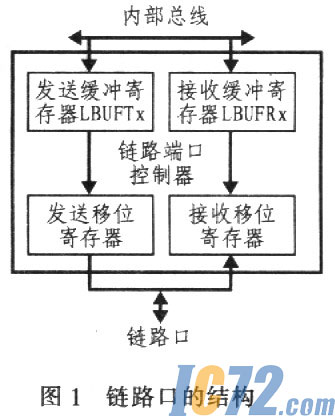

TSl01өДГҝёцБҙВ·ҝЪУЙ·ўЛНЖчәНҪУКХЖчБҪІҝ·ЦЧйіЙЈ¬ГҝІҝ·Ц¶јУР128 bitөДТЖО»јДҙжЖчәН128 bitөД»әіејДҙжЖчЈ¬ЖдҪб№№ИзНјlЛщКҫЎЈГҝёцБҙВ·ҝЪҫщУР8 bitКэҫЭПЯәНLxCLKINЎўLxCLKOUTәНLxDIR(xОӘБҙВ·ҝЪРтәЕ0-3)3ёцҝШЦЖТэҪЕЈ¬ҝЙЦ§іЦ¶аЖ¬TSl01ҙҰАнЖчјдөг¶ФөгөДЛ«ПтКэҫЭҙ«ЛНЈ¬ТІҝЙТФУГУЪУлНвІҝЙиұёҪшРРКэҫЭҙ«КдЎЈЖдЦРLxDIRУГАҙЦёКҫБҙВ·ҝЪөДКэҫЭБчПтЎЈLxCLKINәНLxCLKOUTОӘБҙВ·ҝЪөДКұЦУ/И·ИПОХКЦРЕәЕЎЈ·ўЛНКэҫЭКұЈ¬LxCLKOUTОӘКұЦУРЕәЕЈ¬LxCLKINОӘИ·ИПРЕәЕ;ҪУКХКэҫЭКұЈ¬LxCLKINОӘКұЦУРЕәЕЈ¬LxCLKOUTОӘИ·ИПРЕәЕЎЈ·ўЛНКэҫЭКұЈ¬КЧПИҙ«Кд4ЧЦКэҫЭөҪБҙВ··ўЛН»әіејДҙжЖчLBUFTxЈ¬ФЩҪ«ЖдёҙЦЖөҪТЖО»јДҙжЖч(ИфТЖО»јДҙжЖчОӘҝХЈ¬ҙЛКұLBUFTxҝЙұ»РҙИлРВөДКэҫЭ)Ј¬И»әуТФЧЦҪЪөДРОКҪ·ўЛН(ПИ·ўЛНөНЧЦҪЪ)Ј¬ГҝёцЧЦҪЪФЪБҙВ·КұЦУөДЙПЙэСШәНПВҪөСШұ»Зэ¶ҜәНЛшҙжЎЈҪУКХЖчөДТЖО»јДҙжЖчОӘҝХКұЈ¬ПөНіҪ«ҝӘКјҪУКХ·ўЛН·Ҫҙ«КдөДКэҫЭІўҪ«ЖдЛНИлТЖО»јДҙжЖчЈ¬Н¬КұЗэ¶ҜLxCLKOUTОӘөНөзЖҪЎЈөұХыёц4ЧЦҪУКХНкұПәуЈ¬Из№ыҪУКХ»әіејДҙжЖчLBUFRxОӘҝХЈ¬ПөНі»бҪ«4ЧЦКэҫЭҙУТЖО»јДҙжЖчёҙЦЖөҪLBUFRxЈ¬ІўФЪКэҫЭұ»ёҙЦЖәуЗэ¶ҜЖдLx-CLKOUTОӘёЯөзЖҪЈ¬ТФёжЛЯ·ўЛН·ҪҪУКХ»әіејДҙжЖчОӘҝХЈ¬ҝЙТФЧјұёҪУКХРВКэҫЭЎЈ·ўЛН·ҪјмІвөҪLx-CLKINОӘёЯөзЖҪәуБўјҙҪшРРПВҙОҙ«КдЎЈ

іЈјыөДЖф¶ҜБҙВ·ҙ«КдКэҫЭөД·Ҫ·ЁУР¶юЦЦЈәАыУГTSl01өДIRQЦР¶ПЖф¶ҜәНАыУГБҙВ·ЦР¶ПЖф¶ҜЎЈБҙВ·ҙ«КдТФDMA·ҪКҪҪшРРЈ¬DMA·ҪКҪКЗФЪTSl01ДЪәЛІ»ёЙФӨөДЗйҝцПВЈ¬әуМЁНЁ№эБҙВ·ҝЪёЯЛЩҙ«ЛНКэҫЭөД»ъЦЖЎЈҙУНвІҝЙиұёПтБҙВ·ҝЪҙ«ЛНКэҫЭЈ¬КөјКЙПКЗБҙВ·ҝЪ°СНвІҝЙиұёЛНАҙөДКэҫЭЧФ¶ҜұЈҙжөҪTSlOlөДДЪЎўНвҙжҙўЖчЦРЈ¬ТІҝЙТФҫӯЖдЛыБҙВ·ҝЪЧӘ·ўіцИҘЎЈ¶ФБҙВ·ҝЪј°ЖдDMAјДҙжЖчҪшРРХэИ·өДЙиЦГәуҫНҝЙТФЙиЦГTCBҝйЎЈDMAЖф¶ҜәуЈ¬Т»ө©БҙВ·»әіеЖчОҙВъЈ¬ЛьҪ«ПтНвІҝЙиұёЗлЗуКэҫЭЎЈХвКұЈ¬Из№ыDMAҝЙТФХјУГДЪІҝ»тНвІҝКэҫЭЧЬПЯЈ¬ДЗГҙЈ¬ПөНіұгҝЙҪ«КэҫЭҙУБҙВ·ҝЪҙ«ЛНөҪҙжҙўЖчЦРЎЈ

4 КэҫЭІЙјҜөДУІјюЙијЖ

TSIOIКЗФЛЛгДЬБҰЗҝө«УлНвІҝБ¬ҪУЧКФҙПа¶ФЙЩөДТ»АаDSPЈ¬ФЪ¶аёцTSl01ј¶Б¬өДПөНіЦРЈ¬Из№ыАыУГЧЬПЯҪшРРКэҫЭІЙјҜЈ¬A/DЧӘ»»ЖчНЁіЈРиТӘіӨКұјдХјУГЧЬПЯЈ¬»бҫӯіЈіцПЦХщХјЧЬПЯөДОКМвЈ¬ҙУ¶шөјЦВРЕәЕІЙјҜҙҰАніцПЦЧЬПЯЖҝҫұЈ¬АыУГБҙВ·ҝЪҪшРРКэҫЭІЙјҜҝЙТФәЬҙуіМ¶ИөШКН·ЕЧЬПЯЧКФҙЎЈұҫУҰУГЦРРиТӘ¶Ф10В·ДЈДвРЕәЕН¬КұҪшРР500 kHzөДІЙСщЈ¬ҙ«КдөДКэҫЭВКОӘlOx0.5 MBx2=10 MB/s<250 MB/sЎЈ

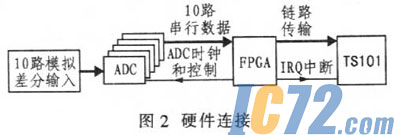

TSl01НЁ№эFPGAҪшРРКэҫЭІЙјҜЈ¬ЛьөДБҙВ·ҝЪЧчОӘКэҫЭКдИлҝЪЎЈЛьГЗөДБ¬ҪУҪб№№ИзНј2ЛщКҫЈ¬Ҫ«БҙВ·ҝЪөДLxCLKINЦұҪУәНFPGAБ¬ҪУЈ¬УЙFPGAЗэ¶ҜЈ¬ФЪFPGAПтБҙВ·ҝЪҙ«ЛНКэҫЭКұЧчОӘБҙВ·ҝЪөДКұЦУКдИлЎЈLxDIRәНLxCLKOUTҝЙТФРьҝХЈ¬БҙВ·ҝЪөД8МхКэҫЭПЯҪУөҪFPGAЙПЎЈ

ЙијЖЦРҪ«ГҝёцA/DЧӘ»»ЖчөДM1ЎўNOЎўA0ТэҪЕҪУөШЈ¬ҪцИЎУГГҝёцA/DЧӘ»»ЖчөД2ёцДЈДвІо·ЦКдИлЎӘЎӘAOәНB0НЁөАЈ¬2ёцНЁөАҝЙТФФЪ2ҰМsЦ®ДЪН¬КұНкіЙ1ҙОІЙСщЎЈұҫЙијЖ№ІУГ5ёцADS8361ј¶Б¬ТФА©ідДЈДвКдИлНЁөАЈ¬КөПЦ10ёцДЈДвНЁөАКдИлЈ¬ГҝёцADS8361өДRDУлCONVSTБ¬ҪУЈ¬УЙFPGAҪшРРҝШЦЖЈ¬5ёцADS8361Н¬КұҪшРРA/DЧӘ»»Ј¬ЧӘ»»әуФЪFPGAДЪН¬КұНкіЙҙ®ІўЧӘ»»Ј¬°СЧӘ»»әуөДІўРРКэҫЭПИЛшҙжФЪFPGAДЪІҝЈ¬ФЩҪ«ёчНЁөА°ҙПИөНЧЦҪЪәуёЯЧЦҪЪТАҙОҙ«ЛНөҪTSl01өДБҙВ·ҝЪЎЈ

5 КэҫЭІЙјҜөДИнјюЙијЖ

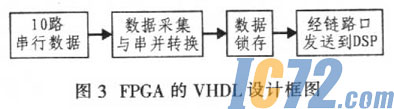

ИнјюІҝ·Ц°ьАЁTSl01ИнјюЙијЖәНFPGAИнјюЙијЖЈ¬FPGAИнјюЙијЖІЙУГVHDLКөПЦЎЈЖдҪб№№ИзНј3ЛщКҫЎЈ

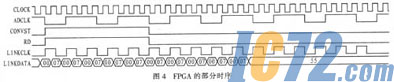

FPGAөДЦчТӘІЩЧчКЗҪ«5ёцADS8361өД10В·ҙ®РРІЙјҜКэҫЭЧӘ»»іЙ20ёц8 bitКэҫЭЈ¬ФЩҪ«КэҫЭЛшҙжЈ¬Н¬КұІъЙъБҙВ·КұЦУЈ¬Ҫ«ЛшҙжәуөДКэҫЭ·ўЛНөҪTSl01БҙВ·ҝЪЎЈРиТӘКөПЦөДКұРтИзНј4ЛщКҫЈ¬ЖдЦРCLOCKКЗTSlOlНвІҝКұЦУЈ¬ADCLKКЗADS8361өД№ӨЧчКұЦУЈ¬КЗCLDCKөД5·ЦЖөЈ¬ХјҝХұИОӘ60%Ј¬CONVSTУлRDПаБ¬ҪУЈ¬LINKCLKКЗБҙВ·КұЦУЈ¬LINKDATAКЗБҙВ·КэҫЭЎЈ

К№УГБҙВ·ҙ«КдКұЈ¬TSl01ФЪБҙВ·КұЦУөДЙПЙэСШәНПВҪөСШ¶јЛшҙжКэҫЭЈ¬20ёц8 bitКэҫЭРиТӘlOёцБҙВ·ВціеЈ¬¶шБҙВ·ҝЪГҝҙОЦБЙЩРиТӘҙ«Кд128 bitөДКэҫЭЈ¬јҙЦБЙЩРиТӘ8ёцВціеЈ¬ЗТ·ўЛНКэҫЭРиТӘөДВціеКэұШРлОӘ8өДұ¶КэЎЈЛщТФЙијЖЦРГҝҙОНЁ№эБҙВ··ўЛНКэҫЭөДВціеКэОӘ16ёцЈ¬З°10ёцҙ«КдA/DЧӘ»»ЖчІЙјҜөҪөДКэҫЭЈ¬ЖдәуөД6ёцВціе·ўЛН0x55ЎЈ·ўЛНөҪБҙВ·өДКэҫЭКЗA/DЧӘ»»ЖчЙПҙОЧӘ»»өДҪб№ыЎЈTSl01ҝЙТФЙиЦГБҙВ·ҝЪ№ӨЧчКұЦУОӘДЪәЛКұЦУөД2Ўў3Ўў4Ўў8·ЦЖөЈ¬ЙијЖЦРTSl01НвІҝКұЦУCLOCKКЗ50MHzЈ¬ДЪәЛКұЦУКЗCLOCKөД5ұ¶Жөјҙ250 MHzЈ¬БҙВ·ҝЪҪУКХКэҫЭКұFPGAёшTSIOIөДБҙВ·КұЦУLINKCLKКЗ25 MHz TSl01БҙВ·ҝЪ№ӨЧчКұЦУУҰҫЎБҝҪУҪьБҙВ·КұЦУLINKCLKЈ¬ЛщТФЙиЦГTSl01БҙВ·ҝЪ№ӨЧчКұЦУОӘДЪәЛКұЦУөД8·ЦЖөјҙ31.25 MHzЎЈ

ПөНіІЙУГБҙВ·ЦР¶П·ҪКҪҪУКХFPGAЛНАҙөДКэҫЭЈ¬БҙВ·ЦР¶П·ҪКҪКэҫЭҪУКХөДіМРтИзПВЈә

6 A/DЧӘ»»ЖчөзВ·өДЙијЖәНК№УГ

ЙијЖёЯҫ«¶ИA/DЧӘ»»ЖчөД№ШјьКЗұЈЦӨУРР§О»КэЈ¬ADS8361өДКдИл¶ҜМ¬·¶О§ОӘЈәЎА2.5 VЈ¬ГҝёцБҝ»ҜөҘО»¶ФУҰ0.076 mVЈ¬ТтҙЛУҰЙи·ЁҪөөНФлЙщәНёЙИЕЎЈФлЙщәНёЙИЕөДАҙФҙЦчТӘУР¶юЦЦЈәТ»ЦЦКЗA/DЧӘ»»ЖчЧФЙнөДФлЙщИзБҝ»ҜФлЙщөИЈ¬БнТ»ЦЦКЗЦЬО§өзВ·ІъЙъөДФлЙщёЙИЕЎЈЗ°ХЯКЗA/DЧӘ»»Жч№МУРөДЈ¬әуХЯөДҙуРЎФ¶Ф¶і¬№эЗ°ХЯЈ¬МШұрКЗөзФҙЎўДЈДв/өзВ·КэЧЦөзВ·Ц®јдөДёЙИЕЎЈADS8361өДІо·ЦКдИл·ҪКҪҙуҙуҪөөНБЛ№ІДЈёЙИЕЎЈЙијЖЦРЦчТӘҝјВЗИзәОФЪөзВ·ЦРјхЙЩЖдЛыФлЙщәНёЙИЕЎЈ

өзФҙЙијЖКЗТЦЦЖФлЙщөД№ШјьЈ¬ұҫОДҪйЙЬөДЙијЖҫЯУР¶аЦЦөзС№(ДЈДв5 VЎў-5 VәНКэЧЦ3.3 VЎў1.2VөИ)ІўЗТКЗ»мәПДЈДвәНКэЧЦРЕәЕөД°еј¶ЙијЖЈ¬СЎФсәПККөДөзФҙөзВ·Ј¬әПАнөШҪшРРөзФҙІгәНөШІгөДЗРёоКЗәЬЦШТӘөДЎЈҝӘ№ШөзФҙҫЯУРМе»эРЎЎўР§ВКёЯЎўКдіцОИ¶ЁөИУЕөгЈ¬Н¬КұДЬ№»әЬәГөШҪвҫцTSlOlөДЙПөзҙОРтОКМвЈ¬ө«ОЖІЁГчПФЎЈҝӘ№ШЖөВКФҪёЯКдіцөзС№ОЖІЁФҪРЎЈ¬өзВ·ЦРСЎУГөДөзёРЖчФЪ10ҰМH~200 ҰМHОӘТЛЈ¬өзВ·ЦРҝЙТФК№УГESRРЎЎўИЭЦөҙуөДөзИЭЖч№№іЙИҘсоөзВ·Ј¬Н¬КұФЪ°еЙП·ЕЦГ¶аЦЦөзИЭЖчҪшРРВЛІЁЎЈ

јхЙЩКэЧЦРЕәЕёЙИЕТІҝЙТФУРР§МбёЯA/DЧӘ»»ЖчөДҫ«¶ИЈ¬Іј°еәНІјПЯКұТӘК№ADS8361ДЈДвІо·ЦРЕәЕКдИлЗшУтҫЎБҝФ¶АлКэЧЦРЕәЕЈ¬FPGAЙијЖЦРҫЎБҝұЬГв¶аёцРЕәЕөзЖҪН¬Кұ·ӯЧӘЈ¬Н¬КұёшA/DЧӘ»»ЖчМṩБјәГөД№ӨЧчКұЦУЈ¬УҰК№УГҙ®БӘЦХ¶Л·ЁЈ¬ҙ®БӘ1Ц»РЎөзЧиЖчҝЙТФәЬәГјхЙЩКұ»щ¶¶¶ҜЈ¬КұЦУРЕәЕҪшИлA/DЧӘ»»ЖчөДІјПЯФҪ¶МФҪәГЈ¬Н¬КұІ»ТӘАлКэЧЦРЕәЕМ«ҪьЈ¬ТІІ»ТӘҝҝҪьДЈДвЗшЈ¬·сФт»бФцјУДЈДвЗшөДФлЙщЎЈН¬КұТӘЧўТвөҘөг№ІөШЈ¬ФЪ№ІөШөДөгЙПҙ®ҪУ1ёцҙЕЦйЎЈЙијЖЦРК№УГБЛ¶аІг°еІјҫЦЈ¬ФЪЗбФШЗйҝцПВҝЙТФҪ«КдіцөзС№ОЖІЁјхөҪ4mVЎЈ

7 ҪбКшУп

ұКХЯЙијЖТ»ЦЦНЁ№эTSl01БҙВ·ҝЪҪшРР¶аA/DЧӘ»»Жч¶аНЁөАёЯҫ«¶ИКэҫЭІЙјҜөДКөПЦ·Ҫ·ЁЈ¬ФЪDSPРЕәЕІЙјҜҙҰАнПөНіЦРҝЙТФІ»ХјУГЧЬПЯЈ¬КөПЦІўРРКэҫЭҙ«КдәНҙҰАнЈ¬УРёьёЯөДКөКұРФЈ¬Н¬КұМҪМЦБЛИзәОМбёЯA/DЧӘ»»Жчҫ«¶ИөДОКМвЎЈёГЙијЖ·Ҫ·ЁТСҫӯУҰУГУЪ¶аЦЦІўРРәНҙ®РРA/DЧӘ»»өзВ·ЦРЈ¬ҫЯУРНЁУГРФЎЈ

|