Ҫ������������źŲ�����������־���ķ�ʽ���������һ���DZ��Ŵ��������������ź�������DZ��Ŵ�������������ӵ�һ������������ַŴ�����һֻ����ˡ���һ�����������DZ��Ŵ������ŵ���������ӵ��裬�����ַ���Ҳ�в��㣬�����뼫����ͬ���������ʱ��������Խϸߵ����ʧ�档��ʱ�����������źŵIJ�ֵ�ӽ���0V����˷Ŵ����������ܲ����뱣�ַŴ������ද̬ȱ�ݵ�Ӱ�졣��һ�ַ���������ֻ�������ַŴ����������������ѹ���������������DZ��Ŵ������������Ŵ����������������ַ����£��������벨�ε�����ź�������Ҫ���ڵ�һ��������

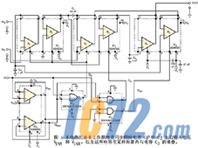

�����ϲ��һ�廯����������ʹ��ͼ1�еĵ�·�ṹ���õ�·ͬʱ�������������ѹVINA��VINB���ڲ��������źŸ���Ч��ƽ������Ϊʹ��A1��B1��A2�ĵ�ѹ�������������VINA�����ڵ���C2�ϣ��ǻ��ء�����C1�����Ϸ������ʱ�ӵأ���IC1Pin9����VINB��ѹ���������ڲ�����������Ϊ��Ч�ĵ͵�ƽʱ������һ���������ڣ�QSB�������ź�Ϊ�ߡ���ѹVC2(TS)=VINA(TS)�任����C1�·����ĵ��ƣ���ΪB3�������ѱ�ʹ�ܡ��ڲ�������ʱ��QSΪ�ߣ�C1���Ϸ�����ڸ��������ڽӵء����ܵ���C3���ͨ��������B2�������ѹVC2(TS)�CVC1(TS)=VINA(TS)�CVINB(TS)��������A3�����迹ת������

A��B��ͨ���ĵ�ѹ������Ե�������ֵ������С�������½�������ͨ��������ͬ����GAINA=��GAINB~(COUTB1/C1)������ͨ�������½��ĵ�ֵԴ�ڴ��ܵ���C1�Ϸ������QSB��Ϊ��ʱ�����������ӵ������ø�����B1���������COUTB1�ϡ�������B1�ڸ������������Ƿŵ���0V������A��B����ĵ�ѹ�ء�����AnalogDevices��˾��AD8592�˷�ʱ���ڽ�ֹ״̬�µ��������COUTԼΪ26.2pF��

��Ӧע�⣬���VINA��VINB�����෴�ҵȷ��ȣ������ﵽVS/2��ֵ���������ѹҪô�ӽ�����ѹ�죬Ҫô�Ǹ���ѹ�졣��������£�����������Լ��ǰ�淽�̸������������������ѹ�ӽ��κε�ѹ��ʱ���˷ŵĵ���Ҳ�������ﵽ55pF��������ӵ������������AD8592������Ļ������ʾ����֮һ����Ϊ��©Դ��ѹ�������ѹ�ӽ�����ѹ��ʱԼΪ0V��©Դ������©Դ��ѹ�½���������MOSFET�ܵĹ������ԡ��������ѹ�ӽ��ڸ���ѹ��ʱ��AD8592��������·����ʾ����Ҳ����ͬ�������

AD8592�ĵ�ͨʱ��Զ���ڹض�ʱ�䡣�������������ݱ���û��ֱ�Ӹ�����Щʱ�䣬�����Դ�IC���ڲ��ṹ������һ�㣬��Ϊ����IC�����м�����on/off���ƣ��ο�����1������ˣ�����������ض���ǰ����״̬�أ���˹ضϺܿ졣��ͼ1��·��һ�����������ڣ�������ͨ��TON�������ĸ��������ӵ��ӳ�(TDE)����һʱ�䴮�;�������̵IJ������ڣ�TMIN~TONB3+4TDE+TONA1B1A2����ʱ��TONA1B1A2�ڸ�����A1��B1��A2�ĵ�ͨʱ���������ֵ����������VINA��VINB��ʵ��ֵ�����ǣ�������Ƶ��Ϊ1/2(TON+2TDE)��

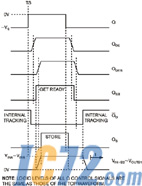

����������ͨʱ����ԴﵽԼ3s�Ĺ�ѹ�ָ�ʱ�䣬�����ӳ�ʱ��ԼΪ0.35s����õ���������Ƶ��ԼΪ135kHz�����ڽӽ���������Ƶ��ֵ�IJ���Ƶ�ʣ��ⲿ�������ź�Q��ռ�ձ�ϵ��ӦΪ��Լ0.5��ͼ2����

|