1引言

随着数字信号处理的高速发展,模拟信号的处理已被数字化处理代替。但对数字系统分辨率的日益提高,作为模数转换系统的核心一A/D转换器,其精度和采样率也随之提高。但精度和采样率是一对矛盾体,很难同时满足要求,因此成为制约A/D采样系统发展的瓶颈。时间交叉采样方案的提出,突破了单个A/D转换器性能的局限性,采用多片高速A/D转换日历交替采样是一种提高系统采样率的有效方法。在多片并行A/D转换器采样系统中,信号重构对于采样时钟精度要求相当严格,传统的晶体振荡器加移位电路和滤波电路的模拟方式已不能满足这一要求。本文提出基于时钟分配器AD9516向四路时间交叉A/D转换器提供采样时钟。

2器件简介及其配置

2.1 AD9516简介

AD9516是一款集低相位噪声时钟发生和低抖动14通道时钟分配功能于一体的时钟分配器。其内部集成1个整数N分频的频率合成器、2个参考输入端、1个压控振荡器(VCO)、可调延迟线和14个时钟驱动器,还包括LVPECL、LVDS和CMOS输出。另外,片内集成的VCO可提高系统可靠性。14个输出通道分别为6路(3对)时钟可高达1.6GHz的LVPECL输出和4路(2对)时钟高达800MHz的LVDS输出,LVDS时钟输出可选为高达200MHz的两通道CMOS输出。

2.2 引脚说明及外围电路配置

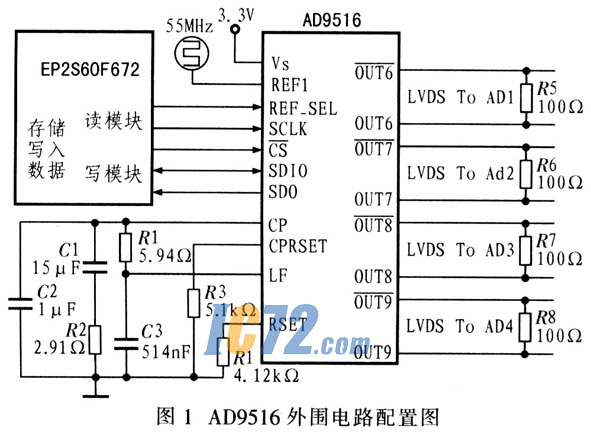

REN_SEL:参考选择。AD9516有REFl和REF2两个参考时钟输入端,该引脚用于定义系统是采用REFl输入(拉低)还是REF2(拉高)的参考信号。

SCLK,CS,SDI0,SD0:串口同步I/0,与SPI协议相兼容,实现与AD9516内部寄存器的通信。其中SCLK为时钟输入;CS为片选信号;SDIO为主机输出/AD9516输入(SCLK的上升沿),或者主机输入/AD9516输出(SCLK的下降沿);SDO为主机输入/AD9516输出。

REFMON,LD,STATUS:状态输出,用于测试AD9516内部信号。通过改变0x17,0x1A,0xlB(内部寄存器的地址)3个寄存器.测试VC0及分频器的输出时钟,获得当前AD9516工作状态。

LF,CP:外部环形滤波,可向内部VCO提供反馈电压。

OUT6,OUT6,0UT7,OUT7,0UT8,OUT8,OUT9,OUT9:输出四路LVDS时钟,可向A/D转换器提供采样时钟。

以上为AD9516主要引脚的功能描述,还有一些包括输入电压,复位等引脚的功能描述可见参考文献。根据上述主要引脚描述,给出了AD9516的外同电路配置图,如图l所示。

2.3 内部寄存器配置

AD9516可设置3种工作模式,包括外部VC0、外部CLK以及内部VC0。本系统设计采用内部VCO和参考输入频率工作模式。

2.3.1 PLL的工作原理

参考输入(REFl输入)先经R分频模块(14位寄存器),再通过R延时模块(延时可调节)后进入PFD(相位/频率监测)模块一端,同时VCO产生的信号通过N分频模块(预分频模块P.P+1和A/B计数模块)和N延时模块(延时可调)后进入PFD的另一端;PFD用于比较两信号的频率和相位差.产生与之成比例的信号传输给CP(电荷泵),电荷泵通过外接环形滤波器连接至VC0的控制端。电荷泵根据PFD的信号对环形滤波器的连接节点充(放)电以达到VCO电压调节目的,使VCO输出和参考输入与PFD的频率和相位完全匹配,此时锁存相位,输出同步。

2.3.2 分频寄存器的配置

除了PLL用于产生稳定的VCO所涉及的寄存器R,A和B外,分频寄存器还包括时钟输出分频寄存器,每对儿输出通道的分频寄存器。时钟输出分频器可以随意设置为2~6中的任意整数,输出通道的每个分频器可选用1~32中的任意整数作为分频参数。需要注意的是:PLL的R、A和B这3个寄存器的配置相互制约,必须合理配置VCO才能工作在由参考输入提供的频率范围内,否则将导致不能锁存锁相模块。这些制约包括:PFD(相位/频率监测)输入频率范围、A和B计数器输入最高频率、A和B值大小。设计时,考虑到这些制约以及设计的需要就能正确配置内部分频寄存器。

2.3.3 输出相位寄存器配置

调整输出相位:包括相位延时粗调和相位延时细调。

(1)相位延时粗调

由于系统要求相差为90°的四路110MHz采样时钟。OUT6作为相位的基准信号,则OUT7相对延时90°,OUT8相对延时180°,OUT9相对延时270°。由于四路LVDS输出是2对,每对共用2个分频器。OUT6与OUT7共用,OUT8与OUT9共用。AD9516的分频器可选用相位延时,因此,可把OUT8与OUT9共用的分频器设置为相位延时180°,则在相位细调时,只需调整0UT7延时90°,OUT9延时90°即可。

(2)相位延时细调

对于OUT7与OUT9相对于OUT6与OUT8的延时90°,通过调节每个输出通道的AT微小延时模块来实现,相位延时细调是通过对△T模块内的电容充放电获得,延时时间可通过电容量和电流值计算。

3软件编程

根据AD9516的工作原理,正确配置所有寄存器,需要把数据加载到AD9516内部寄存器。AD9516的加载模式为串口同步加载,兼容于SPI标准协议和SSR协议,串行控制端允许对AD9516所有寄存器的配置进行读/写,支持单字节和多字节及高/低位优先顺序模式,AD9516串行控制可以配置为单一的双I/O引脚(SDIO)或两个单向引脚(SDIO/SDO)模式。默认模式下,AD9516为双端模式加载,加载时钟为SCLK。

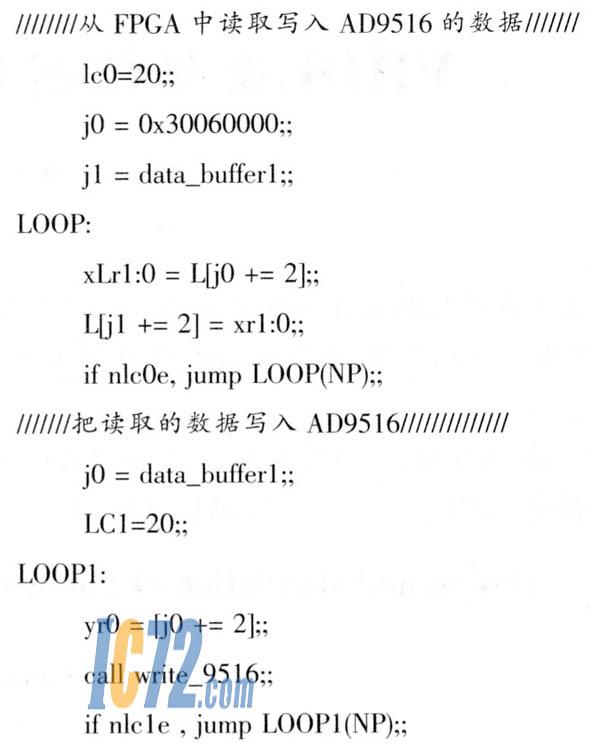

为了便于调试,DSP作为整个读写操作的核心,不管是读数据还是写数据都由DSP完成。写AD9516的软件流程是先把写入寄存器的数值存放在FPGA的ROM中,由DSP通过慢速协议从FPGA读取数据.然后通过DSP写入FPGA的写模块,最后写入AD9516。而读AD9516的软件流程是根据AD9516的读时序,写入读指令,最后由读模块读取AD9516的寄存器数值。

在完成FPGA设计后,由于整个系统控制都是由DSP完成,因此需对DSP进行编程。以下给出部分DSP(TS一201)的写AD9516的程序代码,其中系统寄存器配置为0X189067:64位总线,慢速协议。

最后根据FPGA设计,利用QuartusII仿真。FPGA采用Ahera公司的STRATIXTMII系列的一款EP2S60F672器件。其仿真结果与AD9516的写时序完全吻合。

4结语

交叉采样系统时钟源性能是决定整个采样系统指标的关键。基于此,本文提出了利用AD9516给高速A/D转换提供采样时钟的设计方案。实践证明,利用这种方法产生的时钟能够满足四通道A/D转换实现440MHz的交叉采样的时钟要求,可供其他高速A/D转换的设计人员借鉴。 |