0 引言

近年来,直接频率合成DDS技术的发展,对频率合成器的发展,起到了很好的促进作用,其极低的相位噪声、高分辨率、纳秒级的频率建立时问,使频率合成器的整体性能有了一个质的飞跃。发展前景十分广阔,它将成为频率合成器的新一代方案。采用直接频率合成器(DDS)和分频数字锁相相结合的技术(PLL)。DDS的优点是具有极高的频率分辨率,易实现捷变频,控制方便及能灵活产生多种信号;缺点是DDS杂散抑制差,且分布不易确定,这是该研制课题的难点之一。分频数字锁相技术是长期以来应用成熟的技术,与DDS相比,突出优点是杂散抑制度很高,频率控制方式相对比较方便,可以实现宽带锁相源。因此,采用DDS技术和分频锁相技术相结合,取长补短,可以实现小步进、低相位噪声的频率合成器。

1 电路设计

对于频率范围宽(倍频程)、步进小、相位噪声指标高的频率合成器,主要难点在频率范围、步进、相位噪声三者之问的矛盾。宽带小步进的频率综合器目前常采用的方案有三类,第一类是采用复合环的方案,由2~4个频率合成器复合而成,此方案比较复杂,体积庞大,相位噪声指标很高;第二类是采用现代的小数分频技术来实现,此技术目前已比较成熟,解决了过去离散杂波高的问题,但相位噪声指标比第一类方案差;第三类是采用DDS技术及数字鉴相的方案来实现,此技术根据DDS技术越来越成熟,应用越来越多,该方案解决了步进小、相位噪声指标高的问题,离散杂波指标比第一类方案差,但可以满足一般的系统要求。本课题要求的小体积、低相位噪声、小步进、宽频带,采用第三类方案可以满足技术指标要求。

1.1 设计原理

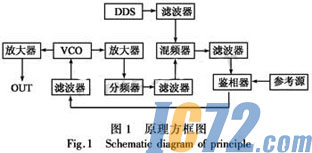

首先VCO的N次分频信号和DDS输出信号进行混频得到中频信号,该信号和参考信号CRO在鉴相器中进行鉴相,产生误差电压来控制VCO的频率和相位,实现锁定,改变DDS的频率控制字来实现1 kHz跳频问隔。VCO信号经功分两路输出,为了改善输出驻波,每个输出端口加了3 dB衰减器,原理方框图如图1所示。

1.2 电路参数设计

频率合成器的相位噪声是指各种随机噪声所造成的瞬时频率或相位起伏,它决定频率合成器的短期频率稳定度。工作在S波段的倍频程带宽VCO自身的近端相位噪声指标不高,通常使用一个外部的参考信号,采用锁相技术来提高其相噪。

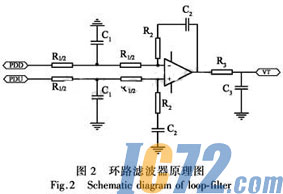

在理想情况下,锁相的典型相位噪声计算公式如下

式中:L(fm)为单边带相位噪声;L(fm)REF为参考源的相位噪声;fI为压控振荡器的频率;fREF为鉴相频率;fm为频偏。

可见,影响频率合成器的相位噪声指标主要因素有参考源的相位噪声L(fm)REF和本振频率与鉴相频率的比值fI/fREF。通常,参考源由晶体振荡器提供,在多年成熟的技术和工艺积累下,国内产品的相位噪声指标已可和国外产品相当。而影响频率合成器相位噪声指标关键因素是N=fVCO/fREF,一般的鉴相电路通常采用将压控振荡器和参考信号分频后在低频鉴相,这样的方法会使得N变得较大,从而使L(fm)变差,同时,低频鉴相的方法也会受到器件自身的限制,甚至比理论计算值恶化10 dB以上。为保证该频率合成器的相位噪声,采取VCO经过分频器、混频器后,转化到中频信号再进行鉴相,避免了N值对相位噪声的限制。

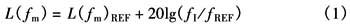

1.2.1环路参数设计

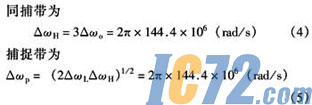

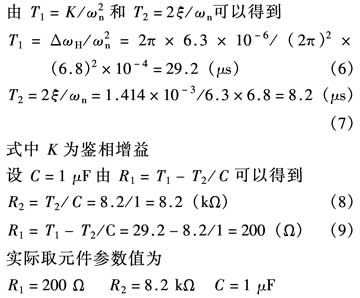

选取参考源的频率为50 MHz,故锁相环路是满足ωi》ωn的高增益二阶环。采用一般高增益二阶环的设计公式进行计算,然后由实验来验证所设条件是否满足,计算是否合理。选取参数如下:环路带宽Fc=50 kHz;阻尼系数ξ=0.707;鉴相频率Fcomp=10 MHz;输出频率Fout=3 000 MHz;鉴相斜率Kd=4 mA/2πrad;压控灵敏度KV=100 MHz/V。计算结果如下

1.2.2杂波抑制设计

杂波在锁相环外主要考虑鉴相泄漏,在锁相环内主要DDS的杂波抑制,在VCO部分主要考虑电源滤波。在VCO的电源端通过采取良好滤波措施、良好接地、合理布线,通常杂波抑制可以做到80 dB以上。在该频率合成器设计中,频率步进为1 kHz通过改变DDS的频率控制字来实现,但是在锁相环内的杂波,是由于DDS的相位截断误差以及D/A转换器精度等引起的固有杂波,因此,只能通过改变DDS的输出频率来避开杂波的方式来减小带内杂波,可以做到65 dB以上。

2试验结果与分析

采用DDS+PLL相结合的技术,通过精心设计,已经研制出1 kHz步进、3~6 GHz倍频程带宽的频率合成器。相位噪声为-100 dBc/Hz/10 kHz。频率转化时间为20μs、杂散抑制为65 dB。

通过对比设计目标与试验结果可知,试验结果与设计值基本相符,利用DDS小步进、频率捷变的优点实现了1 kHz的小步进,对于DDS,该类频率合成器根据实际工程的需要步进可以做到更小,最小为DDS的频率分辨率。因为DDS为直接数字合成,其跳频时间为纳秒量级。利用PLL技术实现了3~6 GHz的倍频程带宽频率合成器,且频率合成器的杂散抑制主要靠环路滤波器进行抑制。因此,该频率合成器取DDS及PLL的优点,避免各自的缺点,获得了性能优越的频率合成器。

3 结语

由以上内容可知,由DDS+PLL技术相结合实现的频率合成器具有频率工作频带宽、相位噪声低、频率步进小、使用灵活、控制方便等优点,可以广泛应用在现代电子系统。具有广阔的市场应用前景,可创造良好的经济效益能力。

|