0 引言

SiGe基区异质结双极型晶体管(SiGe HBT)是利用SiGe合金特性制成的器件。自1987年采用MBE技术首次制作出SiGe基区HBT以来,SiGe集成电路的规模和电路的速度不断发展,电流增益和频率响应等性能已经接近或达到了化合物异质结器件的水平。而SiGe异质结技术和传统的Si集成电路相比,在工艺上并未增加大的复杂性,且成本低于化合物半导体器件。最新的SiGe HBT的研究表明已研制出超过200 GHz电流增益峰值达到400的晶体管,并且低温下fT达到200 GHz的SiGeHBT也已制成。

Ge的电子迁移率是Si的2.6倍,空穴迁移率达到Si的3.5倍。而器件的速度最终取决于在一定的电压下载流子被"推动"而通过器件的速度。通过对SiGe HBT的结构和工艺参数的设计,可以定向地对SiGe HBT的能带结构进行剪裁,在器件结构设计中使用Si1-xGex薄膜作基区,发射结的带隙宽度变化使电子注入基区的势垒降低,使发射效率提高,电流增益增大。通过对基区Ge分布的设计使得基区产生一个内建电场,减小载流子的基区渡越时间从而使fT得到提高,制成超高频晶体管。因此如何通过设计器件结构和控制Ge的组分,包括对Si1-xGex合金的x值的选择和对Ge分布形状的设计,使器件获得更好的电学特性,充分发挥异质结半导体器件的特性成为这一领域研究的重点之一。

综上所述,SiGe HBT的电学特性参数fT和β与Ge的含量和分布关系密切,本文通过计算分析,得到SiGe HBT中Ge的组分和含量对其主要电学特性的影响。

1 Si/Si1-xGex异质结与SiGe HBT

1.1 Si1-xGex异质结

在异质结晶体管中基区采用带隙宽度较小的半导体材料,而发射区采用带隙宽度较大的半导体材料,可以使器件获得高的发射效率。通过改变异质结中两种材料的组分,改变材料的结构和带隙宽度,使结的过渡渐变,引起导带和价带产生能量梯度,则带隙宽度的渐变产生的等效内建电场使载流子的渡越时间减小。对于SiGe HBT,通过对基区Ge组分的设计在基区形成内建场,减小载流子基区渡越时间,进一步提高器件的速度。

Si的带隙宽度为1.11 ev,Ge的带隙宽度为0.67eV,用化学气相沉积(CVD)的方法通过控制气体比例可以获得Si1-xGex合金,合金的带隙宽度在0.67~1.11 eV。很多晶体管参数都与能带结构有着直接的关系,而Si1-xGex合金综合了Si和Ge各自能带的特点,故会对其特性有较大的改善,而且由于Si1-xGex的带隙宽度较小,适合于作HBT的基区以提高发射效率。

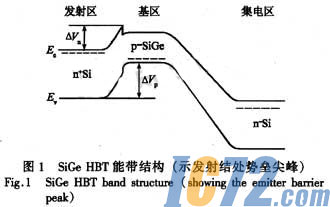

在两种半导体的界面上,由于存在着带隙的差异,如图1所示,其能带会在导带底或价带顶出现不连续的情况,导带底出现的势垒尖峰会阻止非平衡少数载流子(电子)由发射极的注入,从而会降低发射效率γ。但越过势垒尖峰的电子会获得更高的能量,在基区有更高的速度,可以改善器件的频率特性。

对于晶体管的设计,需要在相互关联的性能因素中进行折中考虑,为了缩短基区渡越时间提高晶体管的截止频率,需尽量减小基区宽度。而当基区宽度减小时,器件会受到基区穿通效应的限制,在集电结耗尽层随反偏电压的增高和发射结耗尽层相连时(基区宽度变为零),发生基区穿通。而耗尽层宽度受掺杂浓度影响,增加基区掺杂浓度可以减小耗尽层的厚度,防止基区穿通的发生,但是随着掺杂浓度的提高,发射效率会降低,提高了基区的掺杂浓度,发射区的掺杂浓度也需相应地提高,否则会造成电流增益的下降。而SiGe HBT的基区材料带隙较窄,发射区材料带隙较宽,在进一步提高基区的掺杂浓度时不会对电流增益产生大的影响。

1.2 Si1-xGex薄膜

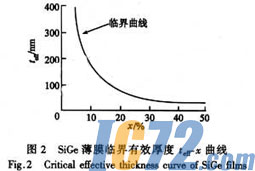

为了保证器件载流子的迁移率,需要小心地外延Si1-xGex薄膜,Si和Ge的晶格常数相差约为4%。对于Si1-xGex合金,当其薄膜厚度较小,Ge含量较低时,Si1-xGex薄膜中价键处于一种畸变的状态,晶格发生弹性应变,以赝晶形式生长,晶格失配较小,不会产生位错失配,弹性应力将保持薄膜的稳定。而当薄膜厚度到达一定程度之后,赝晶体体内积累的应力增大到一定程度时,就会因晶面滑移而形成位错失配,所以要保证薄膜的厚度在不产生位错的范围内。图2为SiGe薄膜临界有效厚度曲线图。在制造工艺中,热氧化工艺、热扩散掺杂等工艺技术需要的温度较高,离子注入掺杂后需要进行退火处理,这对Si1-xGex合金的热稳定性也有一定要求。

超高真空化学气相沉积(UHV/CVD)是在低压化学气相沉积(LPCVD)的基础上,把超高真空技术与化学气相沉积技术相结合,进一步发展出的一种新型异质结生长技术。UHV/CVD外延过程本质上属于反应速率控制生长速率,可以实现均匀性、重复性、可控性良好的多片生长。采用UHV/CVD技术沉积的Si1-xGex薄膜,其中Ge的含量同气源中的Ge含量可以成线性关系,可以由0%~100%任意变化,而HBT复杂的Ge组分分布需通过计算机控制GeH4流量来实现,以获得厚度较均匀的薄膜,另外UHV/CVD加工温度约550℃,不会造成更多的晶格缺陷,保证了载流子的迁移率。

在晶体管设计中,为了减少载流子的基区体复合,增加电子(非平衡少数载流子)扩散通过基区的比例,基区的有效宽度需要远小于电子在基区中的扩散长度(Wb≤Lnb)。在SiGe HBT的设计中为了获得更优良的器件性能需要增加Ge的含量,同时还要保证薄膜的稳定性,以免在工艺过程中受晶格失配的影响。这就要求在不会发生基区穿通的前提下进一步地降低Si1-xGex的薄膜厚度,这也符合晶体管设计对基区宽度小于电子在基区扩散长度的要求。

2 Si1-xGex合金中的Ge组分(x)设计

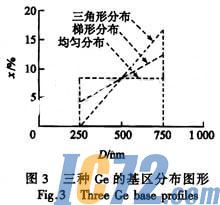

以往的研究指出了三种典型的Ge在基区的分布,分别是三角形分布、均匀分布和梯形分布,如图3所示,而使用何种Ge分布图形受器件的具体应用影响。图3中D为由表面到器件体内的深度。可以看到,对于受到基区渡越时间限制的器件,可以使用缓变基区Ge分布获得一个内建场。

在现代的双极晶体管技术中,一般采用多晶硅发射极结构提高发射效率、电流增益和频率响应。在SiGe HBT中使用多晶硅发射极可以减小发射区的渡越时间,而重掺杂的集电区则可以减小集电区的渡越时间,但是当基区宽度减小时,载流子在基区的渡越时间自然会减小,发射区的渡越时间变得更为重要,基区Ge均匀分布的器件速度更快。

为了获得更好的器件性能,在Ge分布图形设计时使用均匀与缓变相结合的方式,综合二者的优点,可以使用梯形分布。对于不同的应用可以采用不同的分布来达到相应的要求,在要求精度较高的领域,如精确电流源,在数-模和模-数转换器中,电流增益和Early电压之积就较为重要;而在高频应用中,如高频放大器、振荡器等,最高振荡频率就更为重要。

3 Ge的基区组分对器件特性的影响

不同结构参数、不同工艺的Si BJT有着不同的特性参数。SiGe HBT的基区是通过外延生长而成的,在实际应用当中器件是三维的,在电路中会有各种寄生参数,其理论计算会因维数增加变得复杂乃至难以进行。所以,在对器件特性参数进行理论推导时可以认为两种器件的结构是相同的,以简化计算,而且对一维本征器件进行理论推导建模会容易得到Ge的分布情况与器件特性之间的关系。

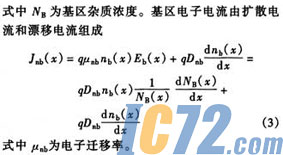

3.1 集电极电流和电流增益

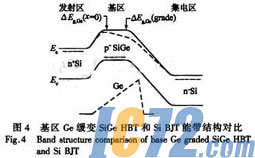

在晶体管基区加入Ge对晶体管直流特性的影响主要是在集电极电流密度上。从物理上来看,电子在EB结处注入基区的势垒,由于Ge的引入而降低,从而对于某一固定的EB偏置,发射区到集电区可以获得更多的电荷输运。图4为基区Ge缓变SiGe HBT和Si BJT能带结构的对比。

式(13)表明β与带隙宽度变化的指数关系,引入Ge使得对于不同的应用可以更容易地获得不同的β值,例如可以适当增大发射结处的Ge组分以增大上式中的分子而增大电流增益;适当减小集电结处的Ge组分以增大该处的带隙宽度,从而使上式中的分母减小,而进一步提高电流增益,减小集电结处的Ge组分会减弱在基区形成的内建场,在速度要求不高而电流增益要求较大的应用场合可以采用这种方法。另外由式(13)可知Ge的组分对β的影响呈指数关系,Ge的组分变化可影响到β,而掺杂浓度的影响相对减小,在对β要求不高的应用中也可以提高基区的掺杂浓度来减小基区电阻而β不会有明显的下降。

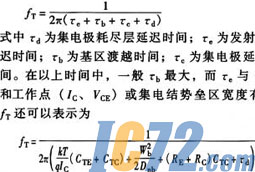

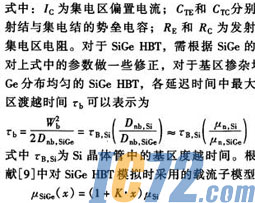

3.2频率特性

SiGe HBT的特征频率fT的表达式和Si-BJT是相同的,即为

可知,提高基区Ge的含量可以提高SiGe HBT的特征频率,通过对Ge组分的设计可以在基区形成一个自建场,使载流子在基区加速,减小载流子基区渡越时间,提高频率响应。

在SiGe HBT中,允许提高基区的掺杂浓度,则在保证基区不发生穿通的前提下,能够尽量减小基区薄膜厚度(基区宽度),从而减小基区渡越时间提高频率特性。另外利用一些工艺技术,如多晶硅发射区自对准技术可使基区串联电阻(包含接触电阻)降低,提高最高振荡频率。

4结论

本文对SiGe技术和Si/Si1-xGex异质结特性进行了分析,研究了对基区Ge组分进行优化设计的方向,对器件主要直流特性参数电流增益等进行了推算,获知Ge的组分对β的影响呈指数关系。根据这一关系,在保证Si1-xGex薄膜稳定性的前提下,可以适当减小集电结处的Ge组分以增大该处的带隙宽度,提高电流增益。而减小集电结处的Ge组分会减弱在基区形成的内建场,在速度要求不高情况下也可以用来提高电流增益。通过提高基区Ge的含量和对Ge组分的设计,提高载流子迁移率,在基区形成自建场,可以提高SiGe HBT的频率特性。在SiGe HBT的设计时需综合考虑薄膜稳定性,Ge组分对电流增益和频率响应的影响,需要在薄膜稳定性与各种晶体管特性参数之间作折中考虑。

|