摘要:详细介绍紫金山天文台红外实验室开发的CCD相机系统的软硬件设计。根据柯达CCD芯片KAF-0401LE的时序要求,用复杂可编程逻辑器件(CPLD)实现了CCD的时序;采用相关双采样技术降低探测信号噪声;用89C51作下位机控制,通过RS232与上位计算机通信;系统控制软件采用VisualC++编写。

引言

CCD通常分为3个等级;商业级、工程级和科学级。3个级别的要求一级比一级高。衡量CCD的性能主要从以下几个方面:量子效率和响应度、噪声等效功率和探测度,即动态范围和电荷转移效率等。科学级CCD以其高光子转换效率、宽频谱响应、良好线性度和宽动态范围广泛用于天文观测,已成为望远镜测必不可少的后端设备。内各天文台望远镜终端都从外围引起的成套设备,使用和维护很不方便,并且价格昂贵,因此国内迫切需要发展自己的CCD技术。紫金山天文台红外实验室对一课题进行了深入研究,广泛调研,认真选取,从芯片开始一直到系统的软硬件设计,搭建了自己的CDD相机系统。

1系统设计

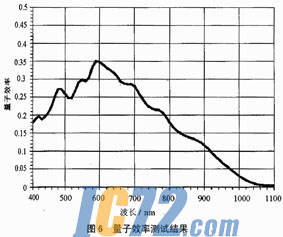

CCD芯片决定相机系统的性能,为此我们广泛调研,最后选定柯达公司的KAF-0401LE芯片。它动态范围大(70dB),电荷转移效率高(0.99999),波响应范围宽(0.4μm~1.0μm),低暗电流(在25℃条件下,7pA/cm2),量子效率为35%,并且具有抗饱和性,能够满足科学观测的要求,既可用于光谱分析,又可用于成像观测。

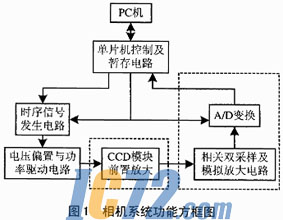

系统设计的重点是解决CCD芯片的驱动和系统噪声的问题。我们的设计如下:采用柯达公司的KAF-0401LE芯片作为探测器,Ateml公司的带闪存Flash的89C51作下位机控制器,复杂可编程逻辑作(CPLD)作时序发生和地址译码,采用相关双采样技术降低噪声,自带采样保持的12位A/D转换顺AD1674进行模数转换,扩展8片128Kbit(628128)的RAM作1为帧图像暂存空间,通过RS232与计算机串口通信,接受计算机的控制。整个系统由图1所示几个功能部件组成。

1.1时序信号发生电路

KAF-0401LE芯片的时序要求:积分期间φV1、φV2保持低电平;行转移期间φH1保持高电平,φH2保持低电平。每行开始φV1的第2个脉冲下降沿后,要有1个行转移建立时间tφHs,读完行后需延迟1个像素时间te才开始下一行φV1脉冲;同样,φV1第2分脉冲下降沿后,开始下一行转移,如此直到读完1帧。

复杂可编程逻辑器件(CPLD)以其高度集成、灵活、方便的特点,在电路设计中运用越来越广泛。Altera公司的复杂可编程逻辑器件EPM712SLC84-15具有2500个可用逻辑门,128个宏单元,8个逻辑块,最大时钟可达147.1MHz,带有68个可供用户使用的I/O引脚,PLCC封装,可通过JTAG接口实现在线编程。我们选用EMP7128SLC84-15,通过硬件描述语言(VHDL)在集成开发环境MAXPLUSII下完成逻辑设计;编译后,通过JTAG接口下载到电路板上的EPM7128SLC84-15中,实现了KAF-0401LE芯片的时序要求。

MAXPLUSII虽然有很丰富的元件库,但并不是针对某一应用而开发的,具有通用性,调用它固有的元件库可能造成资源的浪费,没有必要。因此我们按照需求,编制了自己的元件库,然后在程序中作为元件调用。在本系统中,仅用1片EPM7128LC84-15就实现了CCD的时序要求、暂存RAM和接口扩展芯片8255的片选和地址译码,既简化耻电路的硬件设计,提高了系统可靠性,又降低了成本。

1.2双采取、模拟放大电路及A/D变换电路

我们采用能够满足高频要求的放大器LF356N设计双采样和模拟放大电路。根据CCD的动态范围选用自带采样保持的12位A/D变换器AD1674作模数转换。

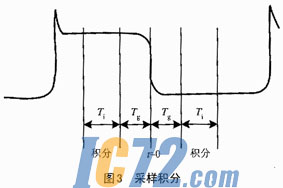

双采样原理如图2所示。RSL是CCD复位电平,光信号相当于SGL与RSL的差值,理论上只要分别在RSL和SGL处各采样一次,然后相减便得到信号的值。然而,实际上RSL和SGL并不是理想的水平线,而是存在着低频起伏噪声。为了降低噪声的影响,通常的做法是,分别在RSL和SGL处多次采样求平均,这样对硬件和数据处理软件的要求都很高。我们这里采用了积分型相关双采样技术,如图3所示,CCD信号分别经过同相和反相放大器连到模拟开关输入端。模拟开关S1打开时,RSL通过电容积分;s2打开时,SGL信号经电容积分;s3打开输入端接地,信号保持不变;s4为复位开关。

积分放大器的输入、输出关系如下:

图2中的积分输出是相关双采样的输出波形图。采样保持后通过A/D进行模数转换,经8255口存在板上的RAM中。

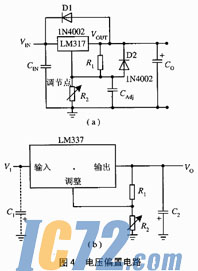

1.3电压偏置电路

CCD驱动信号的直流偏置电压各不相同,CPLD产生的TTL信号必须经过电压变换才能加到CCD的输入端。我们首先用LM317和LM337产生所需要的偏置电压,然后经过时钟驱动芯片DS0026转换得到时序和偏置都符合CCD要求的信号,电路如图4所示。

LM317用于输出正相偏置电压,LM337用于输出负相偏置电压,通过调节可变电阻R2阻值可得到我们所需的偏置电压,计算公式如下:shizi02

其中,Iadj<100μA,Vref=1.25V,图4(a)中R1取240Ω,图4(b)中R1取120Ω。

2软件编程

软件是管理硬件的工具,硬件是实现软件功能的基础。本系统的软件工作任务较重,从可编程逻辑器件的硬件描述语言编程、电路板上单片机的汇编程语言编程,到计算机上控制系统的VisualC++编程。

2.1时序信号的VHDL语言编程

我们用VHDL编制CCD时钟驱动信号、图像暂存RAM和接口扩展芯片8255的地址译码和片选信号,在集成开发环境MAXPLUSII中编译,通过JTAG口下载到EPM7128SLC84-15中。下面给出实现CCD系统时序部分VHDL语言设计和时序仿真结果。VHDL语言编程基本上分为2个部分:实体说明和结构体定义。实体说明部分定义端口,结构体中实现逻辑设计。程序如下:

LIBRARYieee;--包括的库

USEieee.std_logic_1164.all;

USEieee.std_LOGIC_ARITH.ALL;

USEieee.std_logic_unsigned.all;

ENTITYkodak7128IS--实体说明部分

PORT--端口

(clk:INstd_logic;时钟输入

start:INSTD_LOGIC;--启动采集数据输入

rc:OUTSTD_LOGIC;--启动A/D变换输出

s1,s2,s3,s4:OUTSTD_LOGIC;--相关双采样模式时钟输出

v1:OUTSTD_LOGIC;--CCD行转移时钟输出

v2:OUTSTD_LOGIC;

r:OUTSTD_LOGIC;--CCD复位始终输出

h1:OUTSTD_LOGIC;--CCD像素转换时钟信号输出

h2:OUTSTD_LOGIC;

a,b,c:INSTD_LOGIC;--扩展RAM译码输入

a2,a3,a4,a5,a6,a7:INSTD_LOGIC;--口扩展芯片8255地址译码片选输入

a8,a9,a10,a11,a12,a13,a14,a15:INSTD_LOGIC;

ram5,ram6,ram7:OUTSTD_LOGIC;--扩展RAM及8255片选译码输出

ram8,ram9,ram10,ram11,ram12,cs8255:outstd_logic);

ARCHITECTUREmboardOFkodak7128tryIS-结构体实现部分

--PROCESS定义逻辑

ENDmboard;

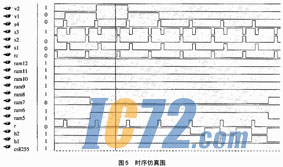

时序仿真结果如图5所示。

2.2下位机的汇编语言编程

89C51作为电路板上的灵魂,负责接收计算机传来的命令,管理CCD数据的采集、接收、传送。与计算机的通信通过串行口中断实现,数据的采集通过外中断实现。

事先需要定义好计算机与单牒同的通信协议,在初始化程序中设置通信波特率、堆栈初始化以及寄存器初值,然后进入循环,等待中断的发生,调用中断子程序,实现预定功能。

当计算机有命令到来时,进入串行中断子程序,在中断中根据预先定好的协议,判断计算机发来的不同命令,调用不同处理子程序。其中的命令有:采集、停止采集、取数、停止取数。

2.3CCD相机控制系统VisualC++编程

Windows以其操作简单、友好的图形界面成为最流行的操作系统。VisualC++是目前公认最强大的Windows程序设计工具。我们用它开发了相机控制系统。

首先定义机接口的操作界面。在程序中主要分为数据的获取、存储与处理几个方面,在数据的获取方面我们专门定义一个串口通信类,开一个线程用于监听串口事件的发生,用于向下位单片机发送命令和接收数据。

3测试结果

我们完成了从芯片到相机系统的软硬件研制,初步测试,效果良好,对于发展我们自己的CCD技术做出有意义的探索和研究。图6是相机CCD量子效率测试结果

|