TMS320C6713是TI公司推出的一款TMS320C6000系列的浮点DSP芯片。其片内有8个并行的处理单元,单字节字长为32位,从而每周期可以执行8条32位指令;他具有强大的外设支持能力,32位外部存储器接口(EMIF)可以很方便地和SRAM,EPROM,FLASH,SBSRAM和SDRAM等同步和异步存储器或者512 MB的外部存储空间连接。

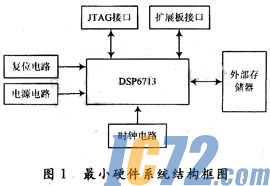

一个DSP硬件系统可以分为最小硬件系统板和外围接口电路2部分,DSP最小板作为开发DSP系统的基础,一般主要包括电源、复位电路、时钟电路、外部存储器总线接口电路、仿真器接口电路等部分,缺一不可。作为控制系统的最小板,需在其外围接入扩展板,以使系统能够实现相应功能,为此,最小板设计扩展板接口,实现DSP与扩展板及其他芯片通信的目的。

2 系统硬件设计

结合DSP-TMS320C6713设计最小硬件系统板对其他基于DSP6713搭建的控制系统以及其扩展电路的设计有实际应用价值。最小板结构框图如图1所示:

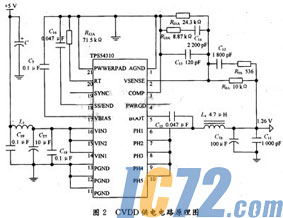

2.1 电源电路

C6000系列DSP采用的是双电源供电方式,即内核与I/O都需要供电,TMS320C6713BGDP300型DSP,其主频最高可达到300 MHz,他对供电电压的要求是:内核电压(DVDD,device voltage)为1.26 V,I/O电压(CVDD,corevoltage)则与外部其他芯片相同为3.3 V。在电源电路设计的芯片选用上,采用的是TI公司的开关电源DC/DC稳压芯TPS54310,其核电压供电电路如图2所示。3.3 V电源电路可以通过改变分压电阻值来获得,结构与图2相似。

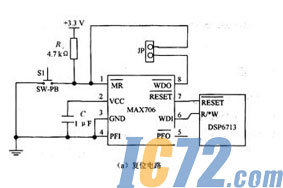

2.2 复位电路

DSP6713需要系统在上电时为其提供一个100~200 ms的复位脉冲,并且由于DSP6713的工作频率达到300 MHz,在运行时很可能发生干扰和被干扰的现象,导致系统不稳定以致死机,所以需要自动复位电路具有监视功能(Watchdog)。系统采用的是Maxim公司生产的MAX706监控器,MAX706的外围电路简单,能有效提高系统的可靠性和抗干扰能力。电路如图3(a)所示。

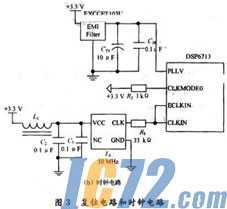

2.3 时钟电路

DSP6713的时钟引脚为CLKIN和ECLKIN。采用频率50 MHz的有源晶振为其提供时钟信号,晶振的输出引脚直接与CLKIN和ECLKIN相连,并通过设置PLL电路的CLKMD0-CLKMD2引脚值来确定倍频系数,经过倍频,产生CPU的工作时钟以及同步接口所需的时钟信号。CLKMD0经1 kΩ的上拉电阻与电源相连,设置为1。如图3(b)所示。

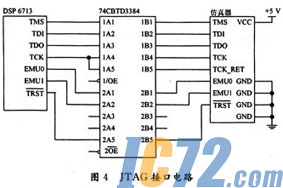

2.4 JTAG接口电路

仿真器的JTAG接口都满足IEEE1149.1标准,与仿真器上的接口一致。系统采用标准的14脚接口,在DSP与JTAG接口之间设置由TI公司生产的74CBTD3384场效应管总线开关芯片组成的电路,通过设置1/OE和2/OE输入电平,以起到控制A脚与B脚导通,从而对TMS,TDI,TDO和TCK_RET信号进行缓冲驱动,叫嚣传播中的延迟,并对电路进行过压保护。如图4所示。

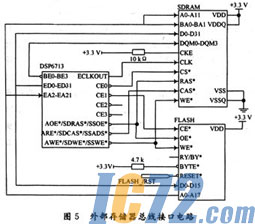

2.5 外部存储器总线接口电路

根据系统设计的要求,采用外接SST公司生产的16位,8 Mb的FLASH-SST39LF800A,以增大系统程序的存储空间,以提高系统工作效率。同时采用Micron公司的32位,64 Mb的SDRAM MMT48LC2M32B-6,其主频最高可达166 MHz,电路如图5所示。

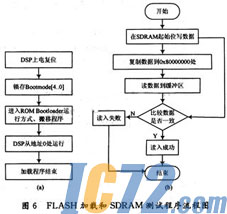

系统采用ROM加载方式,CE0作为SDRAM的寻址空间;CE1作为FLASH的寻址空间,FLASH的加载程序从CE1空间引导装载。当系统复位时,DSP6713通过锁存Bootmode[4…0],设置好地址0处的存储器类型为MAP0,进入ROM Bootloader运行方式,DSP6713通过EDMA把CE1中1 kB数据拷贝到地址0处的存储器中,开始从地址0处运行,读取FLASH的程序。FLASH加载流程图如图6(a)所示。为测试SDRAM连接的是否正确,可通过测试程序在SDRAM起始地址0x0000 0000处写入1 k各数据,并将其复制到0x8000 0000处,同时读入数据缓冲区,和写入数据进行比较。测试程序流程图如图6(b)所示。

2.6 扩展接口电路

作为控制系统的最小系统板,为了与外部扩展板的之间的通讯,使系统模块化,以及满足系统自身及升级的要求,最小系统板为此设计了扩展板接口电路。接口采用96针的针脚式接口,针脚分别分配给地址线、数据线、EMIF接口信号线、电源线、复位线、时钟等。作为扩展板的接口,需在电路输入端加驱动隔离,以保护DSP核心器件,同时增大DSP的驱动能力。为避免最小系统板与扩展板之间的干扰,在接口处需加光电耦合器进行隔离,在此光电耦合器对信号有反向作用,以调整信号的极性。

3 其他电路的设计

(1)由于电路中芯片共用电源,需要在芯片之间接电容电阻去耦,可加33 Ω的排阻以起到减小芯片之间干扰的作用。同时应注意在电源和地之间的去耦,合理分布去耦电容以滤除噪声,提高系统的稳定性。一般对于0402型号0.1μF电容设置在60个左右,其中30个设置在CVDD电路附近,30个设置在DVDD电路附近。并且这些电容放置的位置距DSP不要超过1.25 cm。由于寄生电感会影响电容的工作效率,所以应尽量用体积小的电容。

(2)由于SDRAM在处理、传输数据时会产生大小不一的工作电流,可在SDRAM与DSP之间加入排阻,起到稳压作用,使系统工作更稳定。

(3)为了在DSP芯片焊接之后可以直接通过焊盘检测到芯片引脚的状态,可以将这些引脚引出,为其设计测试孔,以确保在以后改动中可直接从这些测试孔跳线。DSP芯片的有些引脚必须接4.7 kΩ或10 kΩ的上拉电阻拉高,例如READY,EMU0,EMU1,HOLD*,XBUS,RSV等。

4 结 语

最小系统板是DSP系统的核心部件,对DSP系统的近一步开发起着重要作用,可根据不同DSP系统的设计要求进行扩展,具有良好的通用性。基于TMS320C6713设计的最小板方案,以电路板的方式运用于厂家生产中,对产品的开发提供了良好的平台,为进一步开发系统提供了基础。