DMA 控制器具有三条独立的通道。每条通道在配置后都可以用于将数值在任何地址之间进行转移。因此,一个数据表可以同时用于正弦波与余弦波,而两条 DMA 通道只需存取数据表的不同部分,以便形成正弦与余弦输出。

此外,每条 DMA 通道都可以独立递增其源地址或目的地址。本例中,每条 DMA通道编程后递增其源地址,但目的地址不变,始终为其对应的 DAC 数据寄存器。

DMA 传输次数也可以配置。在每条 DMA 通道传输完已编程数据值数量之后,即可以从最初编程的源地址开始进行下一次传输,从而使每条 DMA 通道都构成一个带数据表的环形缓冲区并生成周期波形。

为移动数据值,每条 DMA 通道都需要一个触发器。本例中,来自每个 DAC 的中断标记用作其相应 DMA 通道的触发器。如果 2 条通道同时触发,则需要对DMA 通道进行优先排序,这样一来,会在其中一个接收数据的 DAC 中造成延迟,进而造成输出信号失真,因此应单独处理 DAC 更新。

这些器件中的每个 DAC 都能通过定时器触发,这样在需要下一个 DAC 数据值之前就可以将其加载到 DAC 数据寄存器中,当定时器触发 DAC 时,每个 DAC均能输出新的值。本例中设置由 Timer_A1 输出信号触发每个 DAC。由于 2 个 DAC 采用相同的触发信号,因此每个 DAC 的输出波形相互同步,以便保持相应的正弦/余弦关系。

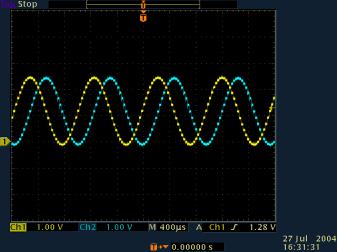

下面列出完整代码以及 2 个输出波形的示波器画面。

------------------------------------------------------------------------- #define FS_Val 4095

static int Sin_tab[40] = {

0.500*FS_Val,

0.598*FS_Val,

0.691*FS_Val,

0.778*FS_Val,

0.854*FS_Val,

0.916*FS_Val,

0.962*FS_Val,

0.990*FS_Val,

1.000*FS_Val,

0.990*FS_Val,

0.962*FS_Val,

0.916*FS_Val,

0.854*FS_Val,

0.778*FS_Val,

0.691*FS_Val,

0.598*FS_Val,

0.500*FS_Val,

0.402*FS_Val,

0.309*FS_Val,

0.222*FS_Val,

0.146*FS_Val,

0.084*FS_Val,

0.038*FS_Val,

0.010*FS_Val,

0.000*FS_Val,

0.010*FS_Val,

0.038*FS_Val,

0.084*FS_Val,

0.146*FS_Val,

0.222*FS_Val,

0.309*FS_Val,

0.402*FS_Val,

0.500*FS_Val,

0.598*FS_Val,

0.691*FS_Val,

0.778*FS_Val,

0.854*FS_Val,

0.916*FS_Val,

0.962*FS_Val,

0.990*FS_Val

};

void main(void)

{

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

ADC12CTL0 = REF2_5V + REFON; // Internal 2.5V ref

//Setup DMA triggers for both DMA channels

DMACTL0 = DMA0TSEL_5 + DMA1TSEL_5; // DAC12IFG trigger

// Setup DMA0

DMA0SA = (int) Sin_tab; // Source block address

DMA0DA = DAC12_0DAT_; // Destination single address

DMA0SZ = 0x20; // Block size

DMA0CTL = DMADT_4 + DMASRCINCR_3 + DMAEN; // Rpt single ch, inc src, word-word

//Setup DAC0 Load with Timer_A, group with DAC1

DAC12_0CTL = DAC12LSEL_2 + DAC12IR + DAC12AMP_2 + DAC12IFG + DAC12ENC + DAC12GRP;

//Setup DMA1

DMA1SA = (int) Sin_tab+8; // Source block address

DMA1DA = DAC12_1DAT_; // Destination single address

DMA1SZ = 0x20; // Block size

DMA1CTL = DMADT_4 + DMASRCINCR_3 + DMAEN; // Rpt single ch, inc src, word-word

//Setup DAC1 Load with Timer_A

DAC12_1CTL = DAC12LSEL_2 + DAC12IR + DAC12AMP_2 + DAC12IFG + DAC12ENC;

//Setup Timer_A

CCTL1 = OUTMOD_3; // CCR1 set/reset

CCR1 = 1; // CCR1 PWM Duty Cycle

CCR0 = 3; // Clock period of CCR0

TACTL = TASSEL_1 + MC_1; // ACLK, upmode

//Turn Off CPU forever

LPM3;

}

-------------------------------------------------------------------------

最后,每次 DMA 传输都会强行占用 2 个 CPU 时钟周期。虽然 CPU 并不用于传输操作,但时钟周期的占用会造成必要的 CPU 开销且大于零。不过,对于 1kHz 的正弦波来说,假设有 32 个数据点,第 31.25个数据点之外的 2 个周期仅需要 6.4%的开销,相比之下不使用 DMA 时开销达到近 50%。另外,产生 2 个波形只需要 4个周期或 7.8% 的开销,而在不使用 DMA 时几乎不可能产生 2 个 1kHz 正弦波。